Professional Documents

Culture Documents

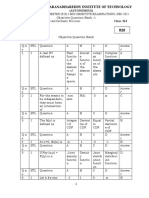

KKR & KSR Institute of Technology & Sciences: Answer All of The Following Questions

KKR & KSR Institute of Technology & Sciences: Answer All of The Following Questions

Uploaded by

madhu0 ratings0% found this document useful (0 votes)

4 views1 pageOriginal Title

VLSI MID-1 online bits-2021

Copyright

© © All Rights Reserved

Available Formats

DOCX, PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

© All Rights Reserved

Available Formats

Download as DOCX, PDF, TXT or read online from Scribd

0 ratings0% found this document useful (0 votes)

4 views1 pageKKR & KSR Institute of Technology & Sciences: Answer All of The Following Questions

KKR & KSR Institute of Technology & Sciences: Answer All of The Following Questions

Uploaded by

madhuCopyright:

© All Rights Reserved

Available Formats

Download as DOCX, PDF, TXT or read online from Scribd

You are on page 1of 1

KKR & KSR INSTITUTE OF TECHNOLOGY & SCIENCES

(Approved by AICTE, New Delhi, Affiliated to JNTUK Kakinada)

(Accredited by NBA , Accredited by NAAC – ‘A’ Grade )

B.Tech III Year II Sem. Regulation : R16

ECE

Date : 14/10/2020

Sections: I,II and III Academic Year :2018-19

Online Test No: 02 Max. Time : 20 Mnt

Sub Code :R1632043 Sub: VLSI Design Max Marks : 10

Answer all of the following Questions

1. In FPGA, vertical and horizontal directions are separated by [ ]

a) A line b) A channel c) A strobe d) A flip-flop

2. Which type of device FPGA are? [ ]

a) SLD b) SROM c) EPROM d) PLD

3. FPGA is [ ]

a) Digital logic design b) Analog design c)DC design d) AC design

4. In FPGA-based design, designers [ ]

(a) design the layout and fabricate the IC (b) download the bit stream to program the device.

(c) both (a) and (b) (d) none of the above

5. LUT is used in [ ]

(a) CPLD (b) ASIC (c) FPGA (d) SPLD

6. Which of the following is not a part of FPGA? [ ]

(a) RTL (b) I/O (c) PI (d) CLB

7. Different FPGA programming technologies are based on [ ]

(a) Anti-fuse (b) SRAM (c) EPROM (d) all of these

8. Testing cost is maximum at __________ level of testing. [ ]

(a) system (b) field (c) board (d) wafer

9. BIST means __________ . [ ]

(a)board integrated system testing (b) built-in system test

(c)built-in self test (d) board-in self test

10. An n-bit LFSR will cycle through __________ . [ ]

(a) 2n – 1 states (b) 2n states (c) 2n–1 states (d) 2! states

11. JTAG means __________ . [ ]

(a) joint test action group (b) joint telecom agency

(c) junior test activity guide (d) joint test activity group

12. BST was originally developed by __________ . [ ]

(a) JTAG (b) JETAG (c) IEEE (d) ANSI

13. Cost of the die depends on [ ]

(a) wafer cost (b) number of die per wafer (c) yield (d) all of these

14. Dynamic power does not depend on __________. [ ]

(a)transistor dimensions (b) load capacitance

(c)power supply voltage (d) switching activity

15. Short-circuit power dissipation does not depend on __________. [ ]

(a)power supply (b) load capacitance (c)rise/fall time (d) transistor dimensions

16. Leakage power is due to __________. [ ]

(a)subthreshold current (b) leakage current (c)both (a) and (b) (d) none of these

17. Standby mode __________ power dissipation. [ ]

(a)increases (b) decreases (c) does not cause (d) none of these

18. Battery operated devices must have __________ power dissipation. [ ]

(a)more (b) less (c) zero (d) none of these

19. Low Vt transistors consume [ ]

(a)more power (b) less power (c) no power (d) none of these

20. High Vt transistors have [ ]

(a)more speed (b) less speed (c) no speed (d) all of these

You might also like

- 2000 Paper 4 NovDocument8 pages2000 Paper 4 Novrajdeepghai5607No ratings yet

- Mapeh 5Document3 pagesMapeh 5areeya mae factores100% (7)

- To Calculate A Quick Budget Price For A Stainless Steel Tank That Includes The FollowingDocument18 pagesTo Calculate A Quick Budget Price For A Stainless Steel Tank That Includes The Followingjayvijay009No ratings yet

- Ade Mid 2impDocument3 pagesAde Mid 2impSasmi AnjaliNo ratings yet

- CS 801D PDFDocument4 pagesCS 801D PDFarnab paulNo ratings yet

- EdaDocument4 pagesEdaJyotirmoy GuhaNo ratings yet

- CO MID-1 BitsDocument6 pagesCO MID-1 BitsMᴀɴɪ TᴇᴊᴀNo ratings yet

- Btech Cse 8 Sem Vlsi Design 2013Document7 pagesBtech Cse 8 Sem Vlsi Design 2013Samshul Ajam AnsariNo ratings yet

- 2011 Eda For Vlsi Design: CS/B.TECH (ECE) (Separate Supple) /SEM-7/EC-702/2011Document7 pages2011 Eda For Vlsi Design: CS/B.TECH (ECE) (Separate Supple) /SEM-7/EC-702/2011John CaterNo ratings yet

- Technical Test For Placement DriveDocument8 pagesTechnical Test For Placement DriveVaibhav GuptaNo ratings yet

- 5 Oct11Document12 pages5 Oct11Manu SeaNo ratings yet

- LP2 PracticeDocument9 pagesLP2 PracticeJUAN PABLO MARTINEZ VARGASNo ratings yet

- Cse5 Cpi Dec09Document2 pagesCse5 Cpi Dec09Navneet Kaur GillNo ratings yet

- Quiz-2 Name: - Date: - Roll NumberDocument2 pagesQuiz-2 Name: - Date: - Roll NumberSyed Hasan RizviNo ratings yet

- 5228 PDFDocument4 pages5228 PDFddNo ratings yet

- Digital QuizDocument17 pagesDigital QuizSri MathiNo ratings yet

- HT TP: //qpa Pe R.W But .Ac .In: 2010 Information System Analysis & DesignDocument4 pagesHT TP: //qpa Pe R.W But .Ac .In: 2010 Information System Analysis & DesignSourav NayakNo ratings yet

- EKT+Question+series+GDocument4 pagesEKT+Question+series+GMota ChashmaNo ratings yet

- EKT2 SetJDocument4 pagesEKT2 SetJShubam ManhasNo ratings yet

- AJP (22517) Unit Test 2 CMIF5I 2022-23Document4 pagesAJP (22517) Unit Test 2 CMIF5I 2022-23Dhaval SarodeNo ratings yet

- Expt FPGA SimulationDocument5 pagesExpt FPGA SimulationArnold SNo ratings yet

- MCQ Basedtest FDPDocument9 pagesMCQ Basedtest FDPKishor Kumar DasNo ratings yet

- Module-5 (Cat.B1.1) Dec-18 Dgca Paper With Ans PDFDocument15 pagesModule-5 (Cat.B1.1) Dec-18 Dgca Paper With Ans PDFMegha ChaudharyNo ratings yet

- AFCAT EKT Question Paper 2 2015 For Computer Science StreamDocument5 pagesAFCAT EKT Question Paper 2 2015 For Computer Science Streambadhautiyaakash48No ratings yet

- Stucor Qp-Ec8791Document5 pagesStucor Qp-Ec8791NGSNo ratings yet

- Technology, Tbengal: Maulana Abul Kalam Azad University OFDocument7 pagesTechnology, Tbengal: Maulana Abul Kalam Azad University OFBikash ChoudhuriNo ratings yet

- Technical Quiz: R.M.K College of Engineering and TechnologyDocument3 pagesTechnical Quiz: R.M.K College of Engineering and TechnologypenaticNo ratings yet

- Verilog - FPGA QP - 3Document4 pagesVerilog - FPGA QP - 3Mohsin Khan ANo ratings yet

- CS302 - Analog and DigitalDocument5 pagesCS302 - Analog and DigitalGaitonde GaneshNo ratings yet

- Unit IV & V Question BankDocument5 pagesUnit IV & V Question BanknithyasaviNo ratings yet

- Assignment Week1Document4 pagesAssignment Week1shwetaNo ratings yet

- VLSIDesignDocument5 pagesVLSIDesignVenkatesh KolatiNo ratings yet

- MPMC Mid-2 Objective Questions 2020-21Document3 pagesMPMC Mid-2 Objective Questions 2020-21ace4No ratings yet

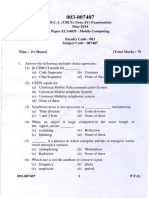

- M.C.A. (CRCS) (Sem.-IV) Examination May-2014 Paper ECA4035: Mobile Computing Faculty Code: 003 Subject Code: 007407Document7 pagesM.C.A. (CRCS) (Sem.-IV) Examination May-2014 Paper ECA4035: Mobile Computing Faculty Code: 003 Subject Code: 007407andre the giantNo ratings yet

- WWW - Manaresults.co - In: Set No. 1Document4 pagesWWW - Manaresults.co - In: Set No. 1Machine BatteryNo ratings yet

- EKT Model Question Paper (Computer Science) - IIDocument4 pagesEKT Model Question Paper (Computer Science) - IInixsNo ratings yet

- DDH 100+ MCQsDocument22 pagesDDH 100+ MCQsENTC-LYB-47-harshal KadamNo ratings yet

- Isro Question Paper 2008Document16 pagesIsro Question Paper 2008singaramani3870No ratings yet

- Aeie 4182 - 2017Document2 pagesAeie 4182 - 2017Adreeja MahatoNo ratings yet

- PLCDocument5,314 pagesPLCmarathi sidNo ratings yet

- 4458-542 Vlsi Design ElexDocument3 pages4458-542 Vlsi Design Elexuttareshwar shindeNo ratings yet

- MCQ Unit-4-Set-1Document10 pagesMCQ Unit-4-Set-1Neha KardileNo ratings yet

- Iot MCQDocument11 pagesIot MCQBiplab SarkarNo ratings yet

- rr421202 Internet TechnologiesDocument5 pagesrr421202 Internet TechnologiesSRINIVASA RAO GANTANo ratings yet

- McqComputer Applications - ScholarexpressDocument6 pagesMcqComputer Applications - ScholarexpressIsmatNo ratings yet

- Internet and Web Technology Exercises With AnswersDocument87 pagesInternet and Web Technology Exercises With AnswersAnonymous 8pCXXs100% (1)

- Operating Systems 1Document4 pagesOperating Systems 1Manoj KanaujiaNo ratings yet

- Digital Vlsi Design (Ecen 3201) - 2017Document2 pagesDigital Vlsi Design (Ecen 3201) - 2017gaurav kumarNo ratings yet

- Digital Systems Design: Time Allotted: 3 Hrs Full Marks: 70Document4 pagesDigital Systems Design: Time Allotted: 3 Hrs Full Marks: 70Vikash KumarNo ratings yet

- Vlsi DesignDocument2 pagesVlsi DesignXXXNo ratings yet

- SLR-PK - 278: SLRPK278Document4 pagesSLR-PK - 278: SLRPK278Mayur HanchateNo ratings yet

- Recent Electronic Components - STUDENTSDocument20 pagesRecent Electronic Components - STUDENTSaryan KadamNo ratings yet

- APCI ET1605 1516S2 SemExamDocument9 pagesAPCI ET1605 1516S2 SemExamzarni77No ratings yet

- Lab Manual: Syllabus Micro Project Final Year Projec MCQ With Answer Model Answer Sample QuestionDocument46 pagesLab Manual: Syllabus Micro Project Final Year Projec MCQ With Answer Model Answer Sample QuestionSOURABHNo ratings yet

- Geethanjali College of Engineering and Technology: Unit - I: Introduction To IC TechnologyDocument19 pagesGeethanjali College of Engineering and Technology: Unit - I: Introduction To IC TechnologyECE A5No ratings yet

- Ldcs MCQDocument7 pagesLdcs MCQUmaNo ratings yet

- PreExam 08 07 2023 CDocument21 pagesPreExam 08 07 2023 CViet Nguyen TuanNo ratings yet

- Btech Cse 4 Sem Advance Computer Architecture 2012Document7 pagesBtech Cse 4 Sem Advance Computer Architecture 2012souravnaskar12578954No ratings yet

- Exploring BeagleBone: Tools and Techniques for Building with Embedded LinuxFrom EverandExploring BeagleBone: Tools and Techniques for Building with Embedded LinuxRating: 4 out of 5 stars4/5 (2)

- Embedded Software Design and Programming of Multiprocessor System-on-Chip: Simulink and System C Case StudiesFrom EverandEmbedded Software Design and Programming of Multiprocessor System-on-Chip: Simulink and System C Case StudiesNo ratings yet

- Kallam Haranadhareddy Institute of Technology: Subject: Random Variables and Stochastic Processes ClassDocument7 pagesKallam Haranadhareddy Institute of Technology: Subject: Random Variables and Stochastic Processes ClassmadhuNo ratings yet

- Sources of Power Dissipation: Dr. M. Madhusudhan ReddyDocument7 pagesSources of Power Dissipation: Dr. M. Madhusudhan ReddymadhuNo ratings yet

- VLSI Design Unit-2 Question BankDocument1 pageVLSI Design Unit-2 Question BankmadhuNo ratings yet

- VLSI MID Important Questions-2021Document1 pageVLSI MID Important Questions-2021madhuNo ratings yet

- Frank Vahid/Tony Givargis: Part-1Document39 pagesFrank Vahid/Tony Givargis: Part-1madhuNo ratings yet

- Magnetic Tunnel Junction: Tunneling Magnetoresistance Spin-Dependent TunnelingDocument3 pagesMagnetic Tunnel Junction: Tunneling Magnetoresistance Spin-Dependent TunnelingmadhuNo ratings yet

- Memory and Programmable LogicDocument26 pagesMemory and Programmable LogicmadhuNo ratings yet

- IETE Template JRDocument7 pagesIETE Template JRmadhuNo ratings yet

- Standby Leakage Power Reduction in Digital CircuitsDocument4 pagesStandby Leakage Power Reduction in Digital CircuitsmadhuNo ratings yet

- SU3712Document107 pagesSU3712Akash ShilimkarNo ratings yet

- 06 Introduction To Investment ABM BF12 IVm N 25Document32 pages06 Introduction To Investment ABM BF12 IVm N 25jcxes Del rosario100% (2)

- Automatic Clothesline REVISEDDocument8 pagesAutomatic Clothesline REVISEDJongin KimNo ratings yet

- CHM256 Experiment 14 Paper ChromatographyDocument8 pagesCHM256 Experiment 14 Paper ChromatographyQistina NayliNo ratings yet

- Aaz 1z Ahu DisassemblDocument40 pagesAaz 1z Ahu DisassemblSergi Hernandez CasagoldaNo ratings yet

- Manual Evo DSP Plus TT 10-20-30!40!60 Ita EngDocument100 pagesManual Evo DSP Plus TT 10-20-30!40!60 Ita Enghytham.midani.63No ratings yet

- Revision Questions Chapter1 Class XDocument2 pagesRevision Questions Chapter1 Class Xm.khalidkuttyNo ratings yet

- Compellent Best Practices With Site Recovery ManagerDocument41 pagesCompellent Best Practices With Site Recovery ManagerLenin KumarNo ratings yet

- Application Notes Rudder Angle Indication System - 10... 0... 10 V Voltage Input 4189350048 UKDocument15 pagesApplication Notes Rudder Angle Indication System - 10... 0... 10 V Voltage Input 4189350048 UKSyam NairNo ratings yet

- Design of Subsea Equipment Exposed To Cathodic ProtectionDocument20 pagesDesign of Subsea Equipment Exposed To Cathodic ProtectionDaniel DamboNo ratings yet

- An Eco-Friendly Method For Synthesis of PDFDocument4 pagesAn Eco-Friendly Method For Synthesis of PDFWalid Ebid ElgammalNo ratings yet

- Common Applications Utilizing A Spherical Roller BearingsDocument12 pagesCommon Applications Utilizing A Spherical Roller BearingsdynamicbearingNo ratings yet

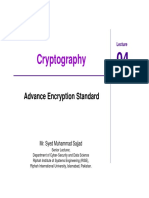

- 4 - Advance Encryption StandardDocument33 pages4 - Advance Encryption StandardDaneil RadcliffeNo ratings yet

- 2ND Floor Electrical Power OutletDocument1 page2ND Floor Electrical Power OutletPatrixia MiclatNo ratings yet

- Triangles Mind Maps + Top 10 QsDocument46 pagesTriangles Mind Maps + Top 10 QsnirikdhaNo ratings yet

- Mobile Crane SpesificationDocument14 pagesMobile Crane Spesificationkacang mete0% (1)

- Carlin GarwinDocument16 pagesCarlin GarwinGalih 'djawa' Parikesit100% (1)

- Notes On Nuts and BoltsDocument6 pagesNotes On Nuts and BoltsRichard HockleyNo ratings yet

- Sequences and SeriesDocument32 pagesSequences and Seriesugharsha1729cinfinityNo ratings yet

- 9 RollingDynamicsDocument10 pages9 RollingDynamicsSonia YadavNo ratings yet

- Chapter 4 Professor YDocument15 pagesChapter 4 Professor YLê Đình VươngNo ratings yet

- Quasi-Static Axial Compression of Thin-Walled Circular Aluminium TubesDocument21 pagesQuasi-Static Axial Compression of Thin-Walled Circular Aluminium TubesJoshua HobsonNo ratings yet

- Economics Honors Exam 2008 Solutions Question 9Document4 pagesEconomics Honors Exam 2008 Solutions Question 9ADITYANo ratings yet

- The Poincar E-Lindstedt Method: The Van Der Pol Oscillator: Joris VankerschaverDocument2 pagesThe Poincar E-Lindstedt Method: The Van Der Pol Oscillator: Joris VankerschaverSaikat GopeNo ratings yet

- Whitepaper Data Communication With Victron Energy Products - ENDocument13 pagesWhitepaper Data Communication With Victron Energy Products - ENDefiant OverlandNo ratings yet

- CE 370 Tutorial Note 4Document5 pagesCE 370 Tutorial Note 4Ibrahim AlmohannaNo ratings yet

- AP-T336-18 Design and Performance of Foamed Bitumen Stabilised Pavements-ReducedDocument310 pagesAP-T336-18 Design and Performance of Foamed Bitumen Stabilised Pavements-ReducedLa FoliakNo ratings yet