Professional Documents

Culture Documents

IC Packaging Endterm

Uploaded by

CynthiaZuycoDeluso0 ratings0% found this document useful (0 votes)

19 views14 pagesAluminum and aluminum alloys are commonly used for metallization in semiconductor fabrication due to their low cost, high conductivity, and compatibility with fabrication processes. During thermal processing, aluminum readily reacts with silicon dioxide to form a protective alumina layer. However, heating aluminum in contact with silicon can cause junction spiking as silicon diffuses into the aluminum. Adding a small amount of copper to aluminum helps address this issue by preventing silicon diffusion while maintaining aluminum's advantages. Barrier metals are also used to prevent diffusion between aluminum and underlying silicon or dielectric layers during high temperature processing.

Original Description:

Copyright

© © All Rights Reserved

Available Formats

DOCX, PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentAluminum and aluminum alloys are commonly used for metallization in semiconductor fabrication due to their low cost, high conductivity, and compatibility with fabrication processes. During thermal processing, aluminum readily reacts with silicon dioxide to form a protective alumina layer. However, heating aluminum in contact with silicon can cause junction spiking as silicon diffuses into the aluminum. Adding a small amount of copper to aluminum helps address this issue by preventing silicon diffusion while maintaining aluminum's advantages. Barrier metals are also used to prevent diffusion between aluminum and underlying silicon or dielectric layers during high temperature processing.

Copyright:

© All Rights Reserved

Available Formats

Download as DOCX, PDF, TXT or read online from Scribd

0 ratings0% found this document useful (0 votes)

19 views14 pagesIC Packaging Endterm

Uploaded by

CynthiaZuycoDelusoAluminum and aluminum alloys are commonly used for metallization in semiconductor fabrication due to their low cost, high conductivity, and compatibility with fabrication processes. During thermal processing, aluminum readily reacts with silicon dioxide to form a protective alumina layer. However, heating aluminum in contact with silicon can cause junction spiking as silicon diffuses into the aluminum. Adding a small amount of copper to aluminum helps address this issue by preventing silicon diffusion while maintaining aluminum's advantages. Barrier metals are also used to prevent diffusion between aluminum and underlying silicon or dielectric layers during high temperature processing.

Copyright:

© All Rights Reserved

Available Formats

Download as DOCX, PDF, TXT or read online from Scribd

You are on page 1of 14

Oxidation growth 4.

TCA (trichloroethane) – less corrosive,

fallen out of favor because it is ozone-

Diffusion – the movement of one material depleting chemical

through another

- Atoms diffuse from regions of high Rate of oxide growth

concentration to regions of low concentration • Describes how fast the oxide grows on

for solid, liquid, or gas states the wafer

- accelerated by temperature • Depends on parameters: temperature,

- (in this process), occurs during oxidation pressure, oxidizing condition (dry or

process wet), Si crystal orientation, doping

levels

Liquid state diffusion • Reduces the thermal budget

• Wide range of thickness (300-20,000 A)

Fick’s Law – describes the rate of movement of • 2 growth stages: linear stage, parabolic

diffusing materials based on temperature, stage

concentration, and the energy necessary to Linear stage

drive diffusion. • Initial growth of silica

• Consumes Si (wafer surface) as a linear

Oxide-Si Interface function of time

• There is an abrupt transition at the • Oxide layer is growing into the wafer at

oxide-Si interface b/w single crystal Si a linear rate over time

to amorphous SiO2. • Valid up to about 150A of oxide

• SiO2 molecule: each Si is bonded to thickness

four O atoms & each O atom is bonded Parabolic stage growth

to two Si atoms • Starts after about 150A of oxide

thickness

Uses of chlorinated agents in oxidation • This stage is slower than the linear

Cl-containing gas: stage

- to neutralize the charge accumulation at the • Diffusion controlled process

interface Factors affecting oxide growth

- Cl ions diffuse to the postively charged layer • Dopant effects

(to form neutral layer) -heavily doped Si oxidizes at a faster

- Cl is kept below 3% (>3% causes instability) rate than lightly doped material

- Tend to increase the oxide growth rate by 10- - In parabolic, B doping will oxidize

15% faster than P.

- Can immobilize (getter) MICs • Crystal orientation

- Linear is dependent on the

Chlorine compound used: orientation of the crystal (e.g. ρ of

1. HCl- extremely toxic & corrosive atoms on the (111) plane > (100)

2. DCE (dichloroethylene) – common Cl plane; therefore, (111) Si crystal

compound will oxidize in the linear stage at a

3. TCE (trichloroethylene) - less corrosive, faster rate than (100))

carcinogenic & not used anymore

- During parabolic, the parabolic rate - Also known as vertical diffusion

constant, B is independent of the furnace (VDF)

crystal orientation - Better temp. control and uniformity

• Pressure effect - Hot wall furnace

- Growth rate will increase with • Rapid Thermal Processor (RTP)

pressure (oxide layer depends on - Small, fast-heating system that

the movement of the oxidizer) processes a single wafer at a time

- Higher pressure increases the linear with a radiant heat source and

and parabolic rate constants cooling source

(forcing the oxygen atoms to - Also known as rapid thermal anneal

penetrate through the growing (RTA)

oxide more rapidly) - Cold wall furnace (heats only the

• Plasma enhancement wafer)

- Increases the oxide growth rate at a

low temperature (reducing the METALLIZATION

thermal budget) • The process of depositing metal film

- Carried out in an oxygen-plasma over a dielectric film and later

discharge generated by an RF patterning it to form the

source interconnecting metal lines and plugs of

- The Si is biased and collects the ICs

charged oxygen in the plasma on • Deposition of a thin film of conductive

the wafer metal onto a wafer by use of chemical

- Results in rapid oxidation and or physical process

allows oxides to be grown at a temp • Metal lines conduct the signal through

< 600oC the IC circuit while dielectric layers

Drawbacks: particle generation, higher ensure signals are not influenced by

film stress, inferior film quality adjacent lines

• Important terms: interconnect, contact,

Furnace Equipment vias, plug

• Horizontal Furnace

- The workhorse in thermal Interconnect – describes the conductor

processing (oldest) materials that create the metal wiring that

- Its name derives from the carries electrical signals to different parts of the

horizontal position of the quartz chip

tube where wafers are located and - a general term for the wiring between devices

heated on a die and the overall package

- Hot wall furnace Contact – the electrical connection at the Si

• Vertical Furnace surface between the devices in the Si wafer and

- Replaced horizontal furnace in the the first metal layer

early 1990s Vias – openings that pass through the various

- Easier to automate, improves dielectric layers to form an electric pathway

operator safely, and reduces from one metal layer to the adjacent metal

particulate contamination layer

Plug – a metal fills the vias to form the electrical • Ag and Au are both prone to

connection (interconnect) between the 2 metal corrosion and high diffusivity of Si

layers and silica

• Ag and Au are much more

REQUIREMENTS: expensive and do not adhere well

• Conductivity: highly conductive, to the oxide films

capable of handling high current • Al reacts readily with silica when

densities heated to form an alumina layer

• Adhesion: ability to adhere to the • Al is easily deposited on the wafer

underlying substrate, easily connect to and etches on solution that do not

external connections attack underlying films

• Deposition: readily deposited with a • Al is compatible with the major

uniform structure & composition by processes in Si IC fab, inexpensive

low-temp. process

• Patterning/planarization: high- Ohmic contact (of Al)

resolution patterning without etching • to form an ohmic contact b/w Al

the underlying dielectric and Si: heat the surface in an inert

• Reliability: metal is soft & ductile to gas or H2 at 450-500oC (the thermal

withstand temp. variations during bake process is known as sinter or

processing & service anneal)

• Corrosion: high resistance to corrosion • undesirable interconnection is

• Stress: resistance to mech’l stress to called spiking

reduce wafer distortion mat’l failures • junction spiking occurs when the

interface of pure Al and Si is heated,

METALS AND ALLOYS USED IN WAFER causing the diffusion of Si into the

FABRICATION Al (amount of about 0.5% and

• Aluminum leaves behind voids)

• Aluminum-copper alloys Problems with spiking: addition of Si to the Al

• Copper

• Barrier metals Al-Cu ALLOYS

• Silicides electromigration - another undesirable

• Metal plugs interconnection

- a reliability problem which is a movement of

Aluminum – the earliest interconnect metals Al atoms in the conductor due to momentum

- the most common interconnect metal wafer transfer from the electron carrying the current

- under high-current conditions, electrons

Selection of Al collide with Al atoms causing the atoms to

• one of the thickest films deposited gradually move

on the wafer (1st metal layer: 5,000 - can be controlled by alloying Al with 0.5-4% Cu

A, upper noncritical layer: 20,000 A)

• has higher resistivity than Cu, Au, Hillocks – another undesirable interconnection

and Ag (2.65 uΩ-cm at 20oC) - accumulation of metal atoms, atoms pile up

- protrusions on the surface of metal films due

to electromigration.

The Limitations of using Al-Cu alloy as Barrier metals – a thin layer of deposited metal

interconnect: or metals that is designed to prevent

1. Cu is difficult to etch intermixing of the materials above and below

2. Residual Cu remaining after etching the the barrier

Al alloy can promote corrosion - Thickness: 100 mm for feature size (0.25-um);

3. Possible to have electromigration in 400 – 600 nm (0.35 um); 23 nm or less for 0.18

contacts and vias um

- prevents the Si and W from coming into

Copper – will replace Al in metallization contact with each other.

Barrier metals – a class of high melting point

known as refractory metals

- common refractory metals: Ti, W, Ta,

Mo, Co, and Pt

Why Ti? Improved adhesion, reduced contact

resistance, reduced stress, and controlled

electromigration

- TiW and TiN are common barrier

metal layers that inhibit diffusion between Si

substrate and Al

Cu Challenges: For Cu interconnect: Ta, TaN, and TaSiN are

• Cu diffuses quickly into oxides & Si candidate materials for barrier metals

• Cu cannot be easily patterned using - Diffusion material must be about 75 Å

regular plasma etching techniques thick

• Cu oxidizes quickly in air at low temp. - can be deposited using HDPCVD

(<200oC) & does not form a protective

layer to stop further oxidation Silicides – formed when refractory metals react

Solution: converting the traditional with Si when alloyed together

interconnect flow to dual damascene flow - a metal compound that is thermally

stable and provides for low electrical resistivity

at the Si/refractory metal interface

- Co and Ti are common refractory photolithography operation in the fab

metals process

- If the refractory metal is reacted with - Produces a three-dimensional pattern

polySi, it is called polycide on the surface of the wafer using a

- Forms extremely good contact to the Si light-sensitive photoresist material and

- Serves as critical adhesion layer controlled exposure to light

between contact metal and the Si - Refers to any printing process that

junction regions transfers a pattern to a planar surface

- Also known as photo, lithography,

Metal Plugs masking, and patterning, printing and

sometimes referred to as optical

- vias filled with plugs to form electrical

photolithography

pathways between 2 metal layers

- It is used to connect the Si devices in Microlithography - describes the process

the wafer to the 1st level of used to pattern the ultraminiature features

metallization necessary for submicron wafer fabrication.

- The most common plug is W (known as Concepts:

W plugs) The most critical step in the IC process

Why W? Requires superior performance to

achieve high yield in other process

• its ability to uniformly fill the high- areas

aspect ratio vias when deposited by Patterns are semiconductor devices in

CVD

the Si wafer, isolation trenches,

• resistant to electromigration failure

contacts, metal interconnects, and vias

• serves as a barrier to inhibit diffusion

Patterns are transferred into a light-

and reaction between Si and the 1st

sensitive photoresist mat’l to prepare

metal layer

the substrate for etch or implantation

• refractory material

Patterned photoresist images are 3-

• melting temp of 3417oC

dimensional (width, length, and height)

• resistivity of 52.8 uΩ-cm at 20oC

Employs a light-sensitive photoresist

(resist), that is applied on the substrate

surface as a polymer solution

Al is desirable as plug material because

The resist is then baked, which drives

of its lower resistivity (2.65 uΩ-cm at

out the solvent

20oC) but cannot fill high-aspect ratio

The resist is exposed to a controlled

vias

light

Al is used as interconnect material & W

The light passes through a reticle that

is limited to the plug

defines the desired pattern

Lithography Photoresist is a temporary mat’l placed

on the wafer surface to transfer the

Photolithography - At the center of the

pattern and is removed once the

wafer fab process, by how wafers

pattern is etched or implanted onto the

repeatedly flow into and out of the

wafer surface.

Photoresist or resist - The ability to reduce the critical

- A temporary material placed on the dimension permits more die to

wafer surface solely to transfer the be placed on a single wafer,

necessary pattern and is removed once lowering fabrication costs and

the pattern is etched or implanted onto improving profitability

the wafer surface material • Light spectrum and wavelengths

- Energy is required to activate

Components of Conventional Photoresist the photoresist and transfer the

pattern from the reticle

Solvent: gives resist its flow characteristics - Deep ultraviolet (DUV)- less than

Resin: mix of polymers used as binder; gives 300nm wavelength) light source is the

resist mechanical and chemical properties source of energy

Sensitizers: photosensitive component of the - The electromagnetic spectrum is used

resist material to introduce the UV light spectrum of

Additives: chemicals that control specific most interest for photolithography

aspects of resist material • Resolution

- The ability to differentiate between two

Photolithography Concepts: closely spaced features on the wafer

surface

• Patterning process - Actual dimensions of the patterned

– Photomask - a mask, a quartz images on the wafer are the feature

plate that contains the full die sizes

array needed to define one Note: features sizes - actual dimensions

process layer for the entire of the patterned images on the wafer

wafer. - Critical dimension (CD) – minimum

– Reticle - a quartz plate that feature size dimensions

contains the pattern to be • Overlay accuracy

reproduced on the wafer, just - Precise alignment between the pattern

as the negative of a camera film on the mask and the existing features

has the pattern for a on the wafer surface

photograph. This pattern may - Alignment is critical because the mask

contain a single die or several pattern must be precisely transferred to

die the wafer from layer to layer

• Critical dimension generations Overlay budget – overlay misalignment

- The width and space of critical

(smallest) circuit elements in an Misregistration – caused by poor

IC alignment between the mask and the

- Also referred to as CD, wafer

minimum geometry, or feature Runout – a net difference in the

size distance from die to die, caused by

- Used to describe device temperature variations

technology nodes or generation

Ex: sub-0.25 um nodes are 0.18 • Process latitude

um, 0.15 um and 0.1 um

- Represents the capability of the The dark portion of the mask is a thin

photolithography process to film of Cr deposited and patterned to

consistency produce products that form the desired mask artwork

meet the specified requirements The chrome is opaque (does not permit

- Examples of process variables: the passage of the UV light)

equipment setting, types of materials, The regions underneath the opaque

human performance, machine chrome of the mask are not exposed to

alignment, and the stability of materials light and therefore remain unchanged

over time

- Objective: to achieve the largest

process latitude possible to make the Positive Lithography

process more capable of producing Regions of the positive resist exposed to

good parts light are removed in a developer

Process latitude means critical solution, whereas resist not exposed to

dimensions can be met within the light underneath the opaque mask

specified limits even with all the process pattern remains on the wafer

variations encountered during The resist that remains was already

production hardened before light exposure and

remains on the wafer surface to protect

Important Wavelengths for the top layer during processing

Photolithography Exposure

Types of Lithography Mask

UV Wavelength Wavelength

UV Emission Source

(nm) Name

436 g-line Mercury arc lamp Dark-field mask – much of the quartz plate is

405 h-line Mercury arc lamp coated with chrome

365 i-line Mercury arc lamp - used for negative resist

248 Deep UV (DUV)

Mercury arc lamp or - used for source/drain implant, contact etch

Krypton Fluoride (KrF) excimer laser

193 Deep UV (DUV) Argon Fluoride (ArF) excimer laser

157 Vacuum UV (VUV) Fluorine (F2) excimer laser Clear field mask –has very thin patterns of

chrome with large areas of clear quartz

- used for positive resist

Negative Lithography - used for gate etch and metal interconnect

The resist remains soft and dissolves etch

when exposed to the developer

chemical Photolithography Process

UV light passes through the clear areas

of the mask and hardens the resist so Types:

that it does not dissolve in the Negative Resist

developer chemical - Wafer image is opposite of

The negative resist has a pattern that is mask image

the opposite of the pattern on the mask - Exposed resist hardens and is

The mask for the photoresist is a insoluble

transparent plate of quartz - Developer removes unexposed

resist

Positive Resist HOW: to coat the wafer with

- Mask image is same as wafer photoresist as quickly as possible,

image maintain a controlled room humidity

- Exposed resist softens and is below 50% RH

soluble Done (usually) before priming and resist

- Developer removes exposed spin coating

resist Bake temp: 200 – 250oC

Done in convection oven with a dry

inert gas (N) or in a vacuum oven, hot

plate (followed by cold plate)

Automated Equipment Integrated into the wafer handling

Also known as coater, developer track system

system, tracks

Employs robots, automated material 8 Steps of Photolithography

handling, and computers to perform all

8 steps w/o human intervention 1. Vapor Prime

Improves process controls (by - The First Step of

controlling delays), processes wafers Photolithography (to clean and

efficiently, increases flexibility, reduces prepare the surface of the

contamination due to environmental wafer):

control, minimal operator handling, - Promotes Good Photoresist-to-

increases safety due to reduced Wafer Adhesion

operator exposure to chemicals - Wafer must be wet cleaned

using DI water

Prior to Vapor Priming - Dehydration dry bake is done to

Wafer Cleaning remove the moisture

- The 1st step of photolithography - Primes Wafer with

- Contaminants: native oxides, metallic Hexamethyldisilazane, HMDS

impurities, particles and organic (acts as adhesion promoter)

contaminants - Serves as the link b/w Si and

- Effects of contaminants: poor adhesion resist (chemically compatible)

*particulates – uneven resist coating and - Coating must be done no later

pinholes 60 min after priming

Dehydration Bake - Priming Techniques (HMDS may

- Wafer exposed to moisture is known as be applied by):

hydrophilic or hydrated.

- Wafer must be hydrophobic for resist Puddle Dispense and Spin

adhesion • used for single wafer processing

- Bake temp: 200-250C, done in an • Consumes a large amount of

convection oven with a dry inert gas (ex. N), HMDS

or on a hot plate Spray Dispense and Spin

For resist adhesion: dry, hydrophobic • Uses nozzle spray to deposit a

(dehydrated) wafer surface fine mist of HMDS on the wafer

surface

• spray will assist in particle Increased process latitude (less

removal from the wafer surface sensitivity to process variations)

• Longer application time and

consumption of HMDS Negative VS Positive Photoresist in Spin Coat

Vapor Prime and Dehydration Bake Negative resist:

• Dehydration bake and vapor - Negative resist was used since the start

priming in the vacuum chamber til mid-70s

w/ N gas - Good adhesion

• Batch process where wafers are - Good resistance to etching

placed in a quartz plate in the - Resolution limit (due to swelling and

oven chamber distortion during develop: about 2 um

• Batch process: heated chamber,

filled with HMDS vapor, after Positive resist:

pretreatment (fill with N) - Desirable in VLSI and ULSI

- Has power adhesion

2. Spin Coat - Improved resolution is not needed

After the wafer has been cleaned, - Remains the dominant type of resist

dehydrated, baked, and primed,

photoresist is then applied Physical Characteristics of Photoresist

Photoresist is done by spin coating • Resolution

Photoresist: - The ability to differentiate b/w 2 or

- An organic compound that experiences more closely spaced patterned features

a change in solubility in a developer on the wafer surface

sol’n when exposed to UV light - Practical way to interpret: the smallest

Is applied as a liquid but dried into a feature that can be printed on the

film. wafer and meets specified quality

Process Summary: requirements

• Wafer is held onto vacuum chuck

• Dispense ~5ml of photoresist • Contrast

• Slow spin ~ 500 rpm - Represents the sharpness of the

• Ramp up to ~ 3000 to 5000 rpm transition from exposure to non-

• Quality measures: exposure in photoresist

– time - Represents the ability of the resist to

– speed become exposed only in those areas

– thickness defined by the clear region of the

– uniformity photomask.

– particles and defects

Poor Resist Contrast

Progressive Improvements in Photoresist - Sloped walls

Better image definition (resolution).

- Swelling

Better adhesion to semiconductor

wafer surfaces. - Poor contrast

Better uniformity characteristics.

Good Resist Contrast

- Sharp walls - Must withstand exposure,

developments, and subsequent

- No swelling

processing

- Good contrast

• Etch resistance

• Sensitivity - Resist film must maintain its adhesion

- The minimum amount of light energy - Resist film protects the substrate

(mJ/cm2) at a certain wavelength that is surface from the wet and dry etch

needed to produce a good pattern in processes

the photoresist on the wafer surface - Dry-etch temperatures: > 150oC

- Exposure dose: the amount of light - Resist must have thermal stability to

energy supplied to a resist maintain its shape

- Important for new resists

• Surface tension

• Viscosity - Refers to the molecular

- Represents a quantitative measure of attraction forces in a liquid that

flow characteristics for the liquid resist tend to pull surface molecules

- time-dependent: increases as the toward the body of the liquid

solvent in the resist evaporates during - -must be low enough to provide

usage for good flow and wafer

- As viscosity increases, the resist has less coverage during application

tendency to flow and its thickness on

the wafer increases • Storage and handling

- Provides better step coverage and

better dry etch resistance - Photoresist chemicals are activated in

- Solid content: represents the amount the presence of energy (light or heat)

of the liquid resist that would remain as - Resists have specific shelf-life and

a solid if the solvent were evaporated storage temp environments

- Specific gravity (SG): a measure of the - If the solvent was evaporated due to

resist density and is related to the solid unsealed environment, viscosity

content in the resist changes rapidly and solids precipitate

- a higher SG means there are more from the liquid

solids in the resist (higher viscosity and - Resist containers: collapsible pouches

lower tendency to flow) that are opaque and loaded directly

- Viscosity: is measured in poise (or into the wafer tracks to avoid opening

centipoise: 1/100th of a poise)

• Contaminants and particles

• Adhesion

- Describes how strongly the resist sticks - Most purity concerns: MICs and

to the substrate particles

- Resist must adhere to various types of - The resist is applied to the wafer

surfaces: (Si, polySi, silica, SiN, and surface material and can easily

different metals) introduce contamination

- Lack of resist adhesion: distorted

patterns on the wafer surface

- To control contamination: must meet 3. High solvent levels would cause

tight filtrations and packaging inadequate discrimination b/w exposed

procedures & unexposed resist for proper

- Control contamination: < 1ppb dissolution during development

4. Outgassing from the resist (from heat

during exposure) could contaminate the

lens of the optical system

3. Soft Bake

Or also known as pre-bake Soft Bake Equipment

Reasons: Vacuum hot plate by heat conduction –

- Drive off the solvent from the coated commonly used

resist on the wafer Infrared (IR) heating

- Improve the adhesion of the resist so Microwave heating

that it adheres adequately during the Convection heating

development step

- Relieve stresses in the resist film that Purpose of Soft Bake:

occurred during the spin process • Partial evaporation of photoresist

- Prevent resist from getting all over the solvents

equipment (keep the cool clean)

• Improves adhesion

Characteristics of Soft Bake:

After the resist applied to the wafer, • Improves uniformity

Improves Photoresist-to-Wafer • Improves etch resistance

Adhesion

Promotes Resist Uniformity on Wafer • Improves line width control

Improves Linewidth Control During Etch • Optimizes light absorbance

Drives Off Most of Solvent in characteristics of photoresist

Photoresist

Typical Bake Temperatures are 90 to 4. Alignment and Exposure

100°C This operation of the wafer stepper

- For About 30 Seconds on a Hot commences once the wafer surface has

Plate been coated with the photoresist and

- Followed by Cooling Step on soft baked

Cold Plate Resist-coated wafers are automatically

Typical time: 30 – 60 sec loaded onto a wafer stage in the

If the resist films were not soft baked & stepper

continued to alignment & exposure, at this stage, the wafer is raised or

problems are: lowered as needed to bring into the

1. Resist film would be tacky & susceptible focus range of the stepper optics

to particulate contamination The wafer is aligned to the reticle so

2. Inherent stresses in the resist film from that the pattern can be transferred to

spin coating would lead to adhesion the proper location on the wafer

problems surface

Once the best focus and alignment are * the develop process then transfers the

obtained, a shutter opens to allow UV film’s image to paper from which a picture is

light to pass from the illuminator to the obtained

reticle through a projection lens and •in photolithography, photomask and its

then onto the resist-coated wafer pattern are the objects to be photographed

The entire focusing, wafer alignment, - Optics and a light source are used to

and exposure operation is done by the project the image of the pattern of the

stepper mask onto the resist coated wafer

Once a pattern is exposed, the stepper - Once the resist is developed, (just as

will step to the next location on the the negative film of the camera) the

wafer and repeat the alignment and mask pattern appears in the resist

exposure (which explains the step-and- Exposure sources:

repeat) - UV light is used to expose resist (resist

Stepper is attached to an automated reacts to light at this wavelength)

wafer track machine Types of UV exposure sources:

1. Mercury arc lamp

Optical exposure High – pressure mercury arc lamp

- During exposure, light from an illumination In this type of lamp, electrical current is

source passes through the aligned reticle passed through a tube of mercury-

xenon gas to create a discharge arc

Reticle has opaque and transparent areas that UV wavelength emissions between

define a pattern to be transferred to the about 240 nm and 500 nm in length

photoresist to the wafer surface Light intensity - import aspect of the

exposure source

GOAL: for the reticle pattern to be accurately

Light intensity

replicated (within specification) in the resulting

- defined by power per unit area

image in the resist

(mW/cm2) & measured on the surface

of the resist

- the quantity of light per unit area or

Process Summary:

brightness

The mask is aligned to the correct location of

Energy

the resist-coated Si wafer

- The product of power and time

Mask and wafer are exposed to UV light to

If the light intensity (power per unit

transfer the mask image to the resist-coated

area) is multiplied by the time of

wafer

exposure = represents the amount of

• The light activates photo-sensitive

exposure energy, or exposure dose

components of photoresist

(mJ/cm2)

• Quality measures:

– Line width resolution

2. Excimer laser

– overlay accuracy

- Provides more light intensity at the DUV

– particles and defects

wavelength of 248 nm and below

Optical lithography

- Similar to photolithography

Ex: *a camera uses light and lens to transfer an

image of an object to a negative film

Excimer – an exotic molecule formed 3. Produce an adequate quantity of

from an atom of a noble gas and acceptable wafers per unit time to meet

halogen, such as ArF production requirements

- comes from the expression excited

dimer (a molecule formed from 2 5. Post- Exposure Bake

identical atoms, such as F2) Required for Deep UV Resists

- is used to represent the noble gas and Typical Temperatures 100 to 110°C on a

halogen molecules hot plate

- uses high-voltage pulse discharge (10 Immediately after Exposure

– 20 kV) Has Become a Virtual Standard for DUV

Most common excimer lasers: and Standard Resists

1. Krypton-fluoride (KrF) – 248 nm, 10-20

W at a frequency of 1 kHz 6. Photoresist Development

2. Argon-fluoride (ArF) – 193 nm, < 20 W Process Summary:

3. Fluorine (F2) – 157 nm, low output • Soluble areas of photoresist are

energy dissolved by developer chemical

General process • Visible patterns appear on wafer

The wafer is 1st positioned within the - windows

focus range of the optical system - islands

Wafer alignment features are aligned to Methods: spin, spray and puddle

similar matching features on the Then, wafers are rinsed in DI water and spin-

photomask, and the UV light is dried

projected through the optics and the • Quality measures:

mask pattern - line resolution

The mask pattern appears as light and - uniformity

dark features on the wafer, thus - particles and defects

exposing the photoresist

7. Hard Bake

Alignment and Exposure Equipment A Post-Development Thermal Bake

Step-and-repeat aligner (thermal bake) to evaporate the

- the critical equipment for remaining photoresist solvent

photolithography Improve Resist-to-Wafer Adhesion

- also known as stepper bake Temperature : 120 to 140°C that is

- aligns and exposes successive reticle higher than Soft Bake

patterns by stepping from one exposure

site to another on the resist-coated 8. Develop/Inspect

wafer surface Purpose:

Purposes: - Identify Quality Problems

1. Focus and align the wafer surface to the (Defects)

quartz plane reticle (containing the - Characterize the Performance

pattern) of the Photolithography Process

2. Reproduce a high-resolution reticle - Inspect to Verify a Quality Pattern

image on the wafer through exposure Prevents Passing Defects to

of photoresist Other Areas

- Etch

- Implant

Rework Mis-processed or

Defective Resist-coated Wafers

- Typically an Automated Operation

You might also like

- OxidationDocument47 pagesOxidationskgarg04100% (1)

- The Deposition Process: An Overview of Thin Film Deposition TechniquesDocument43 pagesThe Deposition Process: An Overview of Thin Film Deposition Techniquesvijayamkulkarni86No ratings yet

- Null 1Document13 pagesNull 1Ankita KotkarNo ratings yet

- ECE 510-Digitial Integrated Circuit-I Winter-2011 CMOS Processing TechnologyDocument39 pagesECE 510-Digitial Integrated Circuit-I Winter-2011 CMOS Processing TechnologyGuru VelmathiNo ratings yet

- DiffusionDocument50 pagesDiffusionNikhil MMNo ratings yet

- IC_FABRICATION_STEPSDocument9 pagesIC_FABRICATION_STEPSR TharunishNo ratings yet

- 1 - Integrated Circuits FabricationDocument116 pages1 - Integrated Circuits FabricationaboudeltohamyNo ratings yet

- NMP 3Document17 pagesNMP 3kalai dossanNo ratings yet

- MCE328 - Pipeline CorrosionDocument74 pagesMCE328 - Pipeline CorrosionM PNo ratings yet

- M.E VLSI Technology UNIT IDocument64 pagesM.E VLSI Technology UNIT IMahendra BabuNo ratings yet

- CMOS Fabrication Processes OverviewDocument30 pagesCMOS Fabrication Processes OverviewJames Hyun Wook ParkNo ratings yet

- WINSEM2018-19 - CHY1701 - ETH - SJT304 - VL2018195004125 - Reference Material I - EC - Module-4-Corrosion ProtectionDocument61 pagesWINSEM2018-19 - CHY1701 - ETH - SJT304 - VL2018195004125 - Reference Material I - EC - Module-4-Corrosion ProtectionkumarklNo ratings yet

- Physical Vapor DepositionDocument30 pagesPhysical Vapor DepositionUgur SenNo ratings yet

- Surface Hardening: - Core With Fine Pearlite, Surface MartensiticDocument28 pagesSurface Hardening: - Core With Fine Pearlite, Surface MartensiticRaghuNo ratings yet

- FALLSEM2015 16 CP3624 24 Aug 2015 RM01 Module 5 CoordinatorDocument43 pagesFALLSEM2015 16 CP3624 24 Aug 2015 RM01 Module 5 CoordinatorPlaya 5No ratings yet

- Electroplating IIDocument53 pagesElectroplating IIGarima UppadhyayNo ratings yet

- 03 - Elec5804 - f2023 - CMOS ProcessingDocument116 pages03 - Elec5804 - f2023 - CMOS Processingclarice.wenNo ratings yet

- VLSI M5 Etching LayoutDocument90 pagesVLSI M5 Etching LayoutMalavika R NairNo ratings yet

- T2 VLSI FabricationDocument24 pagesT2 VLSI FabricationM. Bilal NoorNo ratings yet

- Vlsi TechnologyDocument64 pagesVlsi TechnologySougata GhoshNo ratings yet

- Microelectronics (Ec 305) : Btechece5 SemesterDocument138 pagesMicroelectronics (Ec 305) : Btechece5 SemesterDevansh GuptaNo ratings yet

- C-1 CMOS Processing FlowDocument76 pagesC-1 CMOS Processing FlowKu Ble YanNo ratings yet

- Electric Arc Welding or Smaw: Fernando O. Paras JRDocument17 pagesElectric Arc Welding or Smaw: Fernando O. Paras JRMirasol Nilo GumbaNo ratings yet

- Current Microfabrication and Nanofabrication TechnologiesDocument40 pagesCurrent Microfabrication and Nanofabrication TechnologiesCarlos Alberto López MedinaNo ratings yet

- Surface Hardening: - Core With Fine Pearlite, Surface MartensiticDocument28 pagesSurface Hardening: - Core With Fine Pearlite, Surface MartensiticVaibhav GuptaNo ratings yet

- lec 11 ESE 825 diffusionDocument12 pageslec 11 ESE 825 diffusionMaina PhysicistNo ratings yet

- Flow Diagram For Generic IC Process SequenceDocument46 pagesFlow Diagram For Generic IC Process SequenceMuhammad Muzammil SaleemNo ratings yet

- 2017 Thin Film GrowthDocument70 pages2017 Thin Film GrowthPankaj Kumar100% (1)

- Material Aspects, Wafer Bonding & High Aspect-Ratio ProcessesDocument31 pagesMaterial Aspects, Wafer Bonding & High Aspect-Ratio ProcessesAtul YadavNo ratings yet

- SE&T Week 8-1Document52 pagesSE&T Week 8-1Fahad ShakeelNo ratings yet

- Process Och Komponent K.DDocument28 pagesProcess Och Komponent K.DLuthfiyah13No ratings yet

- Thin Film Deposition TechniquesDocument37 pagesThin Film Deposition TechniquesTadesse BeleteNo ratings yet

- Metal Corrosion and Its Prevention: Material ScienceDocument49 pagesMetal Corrosion and Its Prevention: Material Sciencedr nfNo ratings yet

- Galvanic, Concentration and Pitting CorrosionDocument42 pagesGalvanic, Concentration and Pitting CorrosionLeeMayYanNo ratings yet

- Dielectric Deposition ProcessesDocument43 pagesDielectric Deposition ProcessesSumeet SharmaNo ratings yet

- File 1697182269 GUSBAS202131582 L3 DiffusionandannealingDocument3 pagesFile 1697182269 GUSBAS202131582 L3 DiffusionandannealingÃMĪT KUMAR SINGHNo ratings yet

- Eem413e Lecture-Week4Document47 pagesEem413e Lecture-Week4Furkan AvcıoğluNo ratings yet

- Semiconductor Fabrication: Presented by P JaswanthDocument31 pagesSemiconductor Fabrication: Presented by P JaswanthPullepu JaswanthNo ratings yet

- Epitaxy PDFDocument68 pagesEpitaxy PDFShubham MittalNo ratings yet

- EE669 - Lecture 27 - 15.10.2019 MetallizationDocument19 pagesEE669 - Lecture 27 - 15.10.2019 MetallizationRashmi RavindranathNo ratings yet

- Lecture 4 Thin Film Solar Cell TechnologyDocument83 pagesLecture 4 Thin Film Solar Cell TechnologyHui QingNo ratings yet

- Eee Module 1Document75 pagesEee Module 1Anitha BRNo ratings yet

- Semiconductor Fundamentals Doping Junction The Diode Equation Zener Diode LED ResistorsDocument48 pagesSemiconductor Fundamentals Doping Junction The Diode Equation Zener Diode LED Resistorsershelly9No ratings yet

- Electrodeposition PDFDocument4 pagesElectrodeposition PDFcb gNo ratings yet

- STRUCTURES AND PROPERTIES OF CERAMIC MATERIALSDocument42 pagesSTRUCTURES AND PROPERTIES OF CERAMIC MATERIALSangelo macatangayNo ratings yet

- Thin Aluminum Films PDFDocument13 pagesThin Aluminum Films PDFsmani170No ratings yet

- Lecture 09 Impact and FractureDocument20 pagesLecture 09 Impact and Fractureantoine demeireNo ratings yet

- Semiconductor Physics: Understanding Semiconductors and DopingDocument47 pagesSemiconductor Physics: Understanding Semiconductors and DopingMahendra Singh83% (6)

- Nature and Properties of MaterialsDocument22 pagesNature and Properties of MaterialsAvi AlokNo ratings yet

- Class 6 - 19th AugustDocument50 pagesClass 6 - 19th AugustAADESH GUPTANo ratings yet

- Imperfections in The Atomic ArrangementDocument20 pagesImperfections in The Atomic Arrangementdaisyclare vernyuyNo ratings yet

- Welding Technology HomeworkDocument4 pagesWelding Technology HomeworkDara IsmailNo ratings yet

- (8 2) Film Preparation PVDDocument25 pages(8 2) Film Preparation PVDkenyaengNo ratings yet

- Seminar Topic ON Galvanic Corrosion Parameters: Prepared byDocument16 pagesSeminar Topic ON Galvanic Corrosion Parameters: Prepared byDevashish JoshiNo ratings yet

- 제15주차 Chapter11 웨이퍼 접합기술Document6 pages제15주차 Chapter11 웨이퍼 접합기술K SiriusNo ratings yet

- Lecture 1-Fundamentals of Welding MetallurgyDocument46 pagesLecture 1-Fundamentals of Welding MetallurgyHamiduNo ratings yet

- Electrodeposition of MetalDocument4 pagesElectrodeposition of MetalvkmsNo ratings yet

- Silicon Integrated Circuits: Advances in Materials and Device ResearchFrom EverandSilicon Integrated Circuits: Advances in Materials and Device ResearchDawon KahngNo ratings yet

- 7 Annex C - Subcommittee On Review of FeesDocument7 pages7 Annex C - Subcommittee On Review of FeesCynthiaZuycoDelusoNo ratings yet

- English For Academic and Professional Purposes Lesson PlanDocument12 pagesEnglish For Academic and Professional Purposes Lesson PlanCynthiaZuycoDelusoNo ratings yet

- Inventory Report On Property Plant and Equipment ofDocument2 pagesInventory Report On Property Plant and Equipment ofCynthiaZuycoDelusoNo ratings yet

- NameDocument1 pageNameCynthiaZuycoDelusoNo ratings yet

- 9 Annex D2 - Proposed Enrollment System FlowDocument3 pages9 Annex D2 - Proposed Enrollment System FlowCynthiaZuycoDelusoNo ratings yet

- ANNEX B2. TEMPLATE FOR ALTERNATIVE MODES OF DELIVERYDocument17 pagesANNEX B2. TEMPLATE FOR ALTERNATIVE MODES OF DELIVERYCynthiaZuycoDelusoNo ratings yet

- 2 Annex A1 - SubCommittee On Government Advisories Progress Report (Revised)Document2 pages2 Annex A1 - SubCommittee On Government Advisories Progress Report (Revised)CynthiaZuycoDelusoNo ratings yet

- Matrix of Government Advisories on COVID-19 Implications for SchoolsDocument12 pagesMatrix of Government Advisories on COVID-19 Implications for SchoolsCynthiaZuycoDelusoNo ratings yet

- 10 Annex D3 - Enrollment System Flow - For ParentsDocument8 pages10 Annex D3 - Enrollment System Flow - For ParentsCynthiaZuycoDelusoNo ratings yet

- 4 Annex A3 - Updates On Compensation of Employees During COVID (Revised)Document7 pages4 Annex A3 - Updates On Compensation of Employees During COVID (Revised)CynthiaZuycoDelusoNo ratings yet

- Trial Balance 2020 SCADocument2 pagesTrial Balance 2020 SCACynthiaZuycoDelusoNo ratings yet

- 5 Annex B1 - Redesigning The Curriculum and Modes of Delivery in The Time of COVIDDocument2 pages5 Annex B1 - Redesigning The Curriculum and Modes of Delivery in The Time of COVIDCynthiaZuycoDelusoNo ratings yet

- LitanyDocument10 pagesLitanyCynthiaZuycoDelusoNo ratings yet

- Appendix 9 Property CardDocument1 pageAppendix 9 Property CardCynthiaZuycoDelusoNo ratings yet

- Activity 1Document28 pagesActivity 1CynthiaZuycoDelusoNo ratings yet

- 21ST Century Lit S y 2018-2019Document8 pages21ST Century Lit S y 2018-2019CynthiaZuycoDelusoNo ratings yet

- FDocument9 pagesFSathya NamaliNo ratings yet

- Stock Card: Item: Stock No.: Description: Re-Order Point: Unit of Measurement: Qty. Qty. Office QtyDocument1 pageStock Card: Item: Stock No.: Description: Re-Order Point: Unit of Measurement: Qty. Qty. Office QtyCynthiaZuycoDelusoNo ratings yet

- Negros Occidental Immersion Report School ProgramsDocument225 pagesNegros Occidental Immersion Report School ProgramsCynthiaZuycoDelusoNo ratings yet

- 25 Reading Strategies That Work in Every ContentDocument321 pages25 Reading Strategies That Work in Every ContentCynthiaZuycoDelusoNo ratings yet

- Grade 12 Work Immersion DocumentsDocument1 pageGrade 12 Work Immersion DocumentsCynthiaZuycoDelusoNo ratings yet

- Figures of Speech Power Point NewDocument36 pagesFigures of Speech Power Point NewEdlyn Asi LuceroNo ratings yet

- 21st Century Literature from the Philippines & BeyondDocument7 pages21st Century Literature from the Philippines & BeyondCynthiaZuycoDelusoNo ratings yet

- 21ST Century Lit S y 2018-2019Document8 pages21ST Century Lit S y 2018-2019CynthiaZuycoDelusoNo ratings yet

- 20 Aug MOA Template For Work Immersion Private Company MADDocument7 pages20 Aug MOA Template For Work Immersion Private Company MADAllan Palma Gil100% (4)

- KET SCHL Reading Writing SampleDocument17 pagesKET SCHL Reading Writing SamplefuckingerNo ratings yet

- 2017 Report On Property Palant and Equipment 3Document1 page2017 Report On Property Palant and Equipment 3CynthiaZuycoDelusoNo ratings yet

- Write Resume that Lands a JobDocument7 pagesWrite Resume that Lands a Joballan.manaloto23No ratings yet

- Creative Writing TestDocument38 pagesCreative Writing TestCynthiaZuycoDelusoNo ratings yet

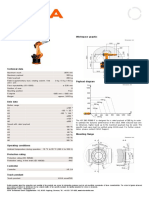

- KR 280 R3080 F technical specificationsDocument1 pageKR 280 R3080 F technical specificationsDorobantu CatalinNo ratings yet

- Lamb To The Slaughter EssayDocument5 pagesLamb To The Slaughter Essaypflhujbaf100% (2)

- Otr Product CatalogDocument116 pagesOtr Product CatalogIwan KurniawanNo ratings yet

- I Am Sharing 'ASSIGNMENT MAT099 - E08G5 - WRTTEN REPORT' With YouDocument23 pagesI Am Sharing 'ASSIGNMENT MAT099 - E08G5 - WRTTEN REPORT' With YouaqilNo ratings yet

- a9ff9ISM - Business DefinitionDocument7 pagesa9ff9ISM - Business DefinitionVikram Kumar100% (1)

- تركيب وتشغيل وحدات تكييف الهواءDocument49 pagesتركيب وتشغيل وحدات تكييف الهواءOmar NabilNo ratings yet

- Sales Target Planning ToolkitDocument7 pagesSales Target Planning ToolkitCarmenLarisaNo ratings yet

- Institute of Graduate Studies (Igs)Document46 pagesInstitute of Graduate Studies (Igs)Syara Shazanna ZulkifliNo ratings yet

- SF-2012AH-QG User' S ManualDocument61 pagesSF-2012AH-QG User' S Manualkamal hasan0% (1)

- 10-09 Oct-Eng-NLDocument4 pages10-09 Oct-Eng-NLdhammadinnaNo ratings yet

- DOE V Rhodes College Ammended Motion For TRODocument19 pagesDOE V Rhodes College Ammended Motion For TROSouwesterdocs100% (1)

- 5.1 Advanced Pattern Making - IDocument9 pages5.1 Advanced Pattern Making - IRisul Islam EmonNo ratings yet

- Faktor OrganisasiDocument9 pagesFaktor OrganisasiNur Fatin NabilahNo ratings yet

- Letter of Request For Brgy. ProfileDocument2 pagesLetter of Request For Brgy. ProfileRhea Mae MacabodbodNo ratings yet

- Exercise 15 Signal TransductionDocument4 pagesExercise 15 Signal TransductionTrina Rose AutidaNo ratings yet

- ZISCO Installs World LongestDocument11 pagesZISCO Installs World LongestJoshua GrahitaNo ratings yet

- State-of-Charge Estimation On Lithium Ion Batteries - Mori W YatsuiDocument5 pagesState-of-Charge Estimation On Lithium Ion Batteries - Mori W Yatsuit3hgoneNo ratings yet

- New Technique for Producing 3D Fabrics Using Conventional LoomDocument1 pageNew Technique for Producing 3D Fabrics Using Conventional LoomSujit GulhaneNo ratings yet

- Second Travel of Rizal: Week 8 Unit 3Document22 pagesSecond Travel of Rizal: Week 8 Unit 3John Russell GasangNo ratings yet

- Kinetic Study of The Catalytic Reforming of Methane With Carbon Dioxide To Synthesis Gas Over Ni - La2O3 Catalyst PDFDocument8 pagesKinetic Study of The Catalytic Reforming of Methane With Carbon Dioxide To Synthesis Gas Over Ni - La2O3 Catalyst PDFMarcus NguyễnNo ratings yet

- Asme A112.4.14-2004 PDFDocument14 pagesAsme A112.4.14-2004 PDFAmer AmeryNo ratings yet

- RIZAL: INSPIRATION FOR A NEW GENERATIONDocument11 pagesRIZAL: INSPIRATION FOR A NEW GENERATIONErica B. DaclanNo ratings yet

- Resilience WorkbookDocument54 pagesResilience WorkbookLeo Siu100% (1)

- Form 4 Biology Chapter OverviewDocument21 pagesForm 4 Biology Chapter OverviewKar KuanNo ratings yet

- A Review of Agricultural Drought Assessment With Remote Sensing Data: Methods, Issues, Challenges and OpportunitiesDocument14 pagesA Review of Agricultural Drought Assessment With Remote Sensing Data: Methods, Issues, Challenges and Opportunitiesاسامة نعمة جبارNo ratings yet

- Lesson Plan For Demonstration (COT) : School Grade Level Teacher Learning Area Teaching Dates and Time QuarterDocument6 pagesLesson Plan For Demonstration (COT) : School Grade Level Teacher Learning Area Teaching Dates and Time Quartermaritel dawaNo ratings yet

- PB ManualDocument23 pagesPB ManualwilyNo ratings yet

- Revised Bsy Elementary Siatonwest 2 and Pio-Macahig - 2014-15 As of June 6 2014Document31 pagesRevised Bsy Elementary Siatonwest 2 and Pio-Macahig - 2014-15 As of June 6 2014api-273918959No ratings yet