Professional Documents

Culture Documents

Elec Dig Ex Gener 14

Uploaded by

Marc CañadaOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Elec Dig Ex Gener 14

Uploaded by

Marc CañadaCopyright:

Available Formats

Universitat de Lleida

Grau d’Enginyeria Electrònica Industrial i Automàtica

Electrònica digital

Examen parcial gener 2014

1. (3 punts) Un consell d’administració està constituït pel president (P), el vicepresident

(V), el secretari (S) i tres consellers (C1, C2, C3). Per aprovar (1 lògic) o denegar (0

lògic) una proposta cal tenir la majoria de vots en el mateix sentit. Si es dóna un empat,

la proposta s’aprova o no per majoria de vots excloent el del president.

a) (1.5) Fer el disseny d’un circuit que prengui com entrada els vots de cadascun dels

participants en el consell d’administració i que sumi els vots afirmatius, donant el valor

de la suma de vots en un número binari de tres dígits (x2,x1,x0). Cal fer el disseny

utilitzant només blocs sumador complet (full-adder) com el de la següent figura.

Ai Bi Cin

Full-adder

Cout Suma

b) (0.75) Fer el disseny d’un circuit, que generi una funció de sortida EMP, que s’activi

si el resultat de la votació ha estat d’empat.

c) (0.75) Fer el disseny d’un circuit, que en el cas d’empat, doni el resultat de la votació

excloent el vot del president.

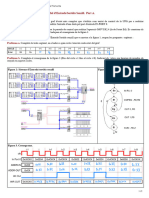

2. (4 punts) El circuit de la figura està format per dos mòduls i té el comportament que

s’indica a continuació:

x7 x6 x5 x4 x3 x2 x1 x0

c1

MÒDUL A

c0

y7 y6 y5 y4 y3 y2 y1 y0

Load

Init MÒDUL B

CK

El MÒDUL A és un circuit combinacional al que se li entra una paraula de 8 bits

(x7,x6,..,x0) i genera com a sortida una altra paraula de 8 bits (y7,y6,..,y0). La paraula

de sortida correspon a la d’entrada modificada, segons el que indiquen les dues entrades

de control c1,c0, tal com marca la següent taula:

c1 c0 Valor de la paraula de sortida

0 0 Paraula d’entrada desplaçada cíclicament a la dreta

0 1 Paraula d’entrada desplaçada cíclicament a l’esquerra

1 0 Paraula d’entrada complementada bit a bit.

1 1 Paraula d’entrada sense modificar

Universitat de Lleida

Grau d’Enginyeria Electrònica Industrial i Automàtica

Electrònica digital

Examen parcial gener 2014

El MÒDUL B és un circuit seqüencial que actua com a registre per emmagatzemar la

sortida del MÒDUL A, quan s’activi la línia Load. A més a més aquest registre té una

línia Init, per inicialització del seu contingut a 0 lògic de manera assíncrona.

a) (2) Dissenyar el MÒDUL A utilitzant multiplexors i portes NOT si cal.

b) (2) Fer el disseny del MÒDUL B. Es disposa per aquest circuit de flip-flops JK amb

entrades de Set i Reset directe, com el que es mostra a la següent figura. Es disposa

també de portes AND, OR i NOT.

3. (3 punts)

a) (2) Fer l’anàlisi del següent circuit seqüencial i donar el diagrama d’estats que

correspon al seu comportament. (Nota: en aquest circuit la notació x’ i Q’ indiquen la

variable complementada).

b) (0.5) Suposant que el circuit es troba a l’estat (Q2,Q1)=(0,0), dir quina serà la

seqüència de valors que anirà agafant la variable z si el valor de x pren els següents

valors en ordre en el temps: 0,1,1,0,0.

c) (0.5) Donar una seqüència de valors de x, que facin que partint de l’estat

(Q2,Q1)=(0,0) es pugui arribar a l’estat (Q2,Q1)=(1,1).

You might also like

- Electrotecnia Pau 2015Document158 pagesElectrotecnia Pau 2015Pau Bon FillgassoNo ratings yet

- Elec Dig Ex Recuperacio Febrer 18Document2 pagesElec Dig Ex Recuperacio Febrer 18Marc CañadaNo ratings yet

- Elec Dig Ex Recuperacio Gener 14Document2 pagesElec Dig Ex Recuperacio Gener 14Marc CañadaNo ratings yet

- Elec Dig Ex Gener 16Document2 pagesElec Dig Ex Gener 16Marc CañadaNo ratings yet

- Elec Dig Ex Gener 13Document2 pagesElec Dig Ex Gener 13Marc CañadaNo ratings yet

- Elec Dig Ex Gener 15Document2 pagesElec Dig Ex Gener 15Marc CañadaNo ratings yet

- Elec Dig Ex Recuperacio Febrer 16Document2 pagesElec Dig Ex Recuperacio Febrer 16Marc CañadaNo ratings yet

- Elec Dig Ex Recuperacio Febrer 13Document2 pagesElec Dig Ex Recuperacio Febrer 13Marc CañadaNo ratings yet

- Elec Dig Ex Gener 17Document3 pagesElec Dig Ex Gener 17Marc CañadaNo ratings yet

- Elec Dig Ex Recuperacio Febrer 17Document2 pagesElec Dig Ex Recuperacio Febrer 17Marc CañadaNo ratings yet

- Solucions Examen 23 01 2012 VAL APNLDocument9 pagesSolucions Examen 23 01 2012 VAL APNLAdri SsNo ratings yet

- ET8a 09 10 Q1 ElectronicDocument7 pagesET8a 09 10 Q1 Electronicrc7pablorNo ratings yet

- Pau Elec18jl PDFDocument8 pagesPau Elec18jl PDFJOSEP MARIA BERGADANo ratings yet

- DOSSIER 4rT ESO-TECNOLOGIA-2017-2018-UNITAT 4 - ELECTRÒNICA DIGITALDocument13 pagesDOSSIER 4rT ESO-TECNOLOGIA-2017-2018-UNITAT 4 - ELECTRÒNICA DIGITALRida Eddellah MohamedNo ratings yet

- PAU 2013 - EnunciatsDocument8 pagesPAU 2013 - EnunciatsTrafalgar LawNo ratings yet

- Gs Tecnolog IndDocument8 pagesGs Tecnolog IndSamuelNo ratings yet

- Problemes de Circuits Lògics - SolucióDocument5 pagesProblemes de Circuits Lògics - SoluciósolercruanyesNo ratings yet

- 5 Sistemes CombinacionalsDocument18 pages5 Sistemes Combinacionalsibn.ruhaim100% (3)

- UntitledDocument7 pagesUntitledArnau Cabrera NdougaNo ratings yet

- Exercicis Funcions I Portes LògiquesDocument1 pageExercicis Funcions I Portes LògiquesHugo HSNo ratings yet

- Estudi-Previ-1b Dispositivos ElectronicosDocument9 pagesEstudi-Previ-1b Dispositivos ElectronicosLolelo1234567890No ratings yet

- Repàs de DigitalDocument1 pageRepàs de Digitalestefaniapitarch8498No ratings yet

- Colec Prob Tema 2 1 v2018Document7 pagesColec Prob Tema 2 1 v2018Ammar Makhlouf HamouriNo ratings yet

- Tecno 2013Document8 pagesTecno 2013sagras34No ratings yet

- ET6a 09 10 Q1 ElectronicDocument6 pagesET6a 09 10 Q1 Electronicrc7pablorNo ratings yet

- DD Prac1 v3 12Document11 pagesDD Prac1 v3 12GaizkaNo ratings yet

- Pau Tecno 16 SetiembreDocument4 pagesPau Tecno 16 SetiembreManoloNo ratings yet

- AltresPau PDFDocument302 pagesAltresPau PDFAnonymous 7alzZ0Yh100% (1)

- Resultats P1 REGA EEBE 1Document2 pagesResultats P1 REGA EEBE 1arnau.gonzalez.almirallNo ratings yet

- Sistemes DigitalsDocument31 pagesSistemes DigitalsAdriNo ratings yet

- PAU 2011 - EnunciatsDocument16 pagesPAU 2011 - EnunciatsSalima AxhaNo ratings yet

- Electrotècnia Setembre 2022 EnunciatDocument16 pagesElectrotècnia Setembre 2022 EnunciatIrene Cabello RodríguezNo ratings yet

- Xarxes de Comunicació de DadesDocument14 pagesXarxes de Comunicació de DadesKhadija Lharrak Ben KtibNo ratings yet

- Garcia Manel 08A ASIXDocument10 pagesGarcia Manel 08A ASIXmgaarciap05No ratings yet

- 04 - Estil I OperacionsDocument13 pages04 - Estil I Operacionsdaniel fernandezNo ratings yet

- Investigacion 4Document10 pagesInvestigacion 4Scott AdielNo ratings yet

- Problemes FINALDocument6 pagesProblemes FINALCristian DazaNo ratings yet

- Enunciat02aPràctica IdentificacioARXDocument2 pagesEnunciat02aPràctica IdentificacioARXBiel Orrit NabauNo ratings yet

- Practica 7 Electrònica - Bautista Sánchez Axel MauricioDocument8 pagesPractica 7 Electrònica - Bautista Sánchez Axel MauricioFlores Coss MauricioNo ratings yet

- MTM II Mayo 2015Document4 pagesMTM II Mayo 2015Bakre ToutaiNo ratings yet

- Informe 1 CADocument14 pagesInforme 1 CAJordi Gallart MartínezNo ratings yet

- Pau Diodes2Document8 pagesPau Diodes2Irene Carmona MarchenaNo ratings yet

- Bpr1.1 - Sistemes Avançats de Control Industrial M6-UF1-provisional PDFDocument17 pagesBpr1.1 - Sistemes Avançats de Control Industrial M6-UF1-provisional PDFOriolNo ratings yet

- Microones Gener05Document4 pagesMicroones Gener05Marianela SaraviaNo ratings yet

- AltresPau PDFDocument302 pagesAltresPau PDFNuria SánchezNo ratings yet

- EnunciatDocument8 pagesEnunciatmiquelsenslNo ratings yet

- Final Analogica 2017Document2 pagesFinal Analogica 2017jose.martinez.garciaNo ratings yet

- Problemes-RI Enunciats PDFDocument24 pagesProblemes-RI Enunciats PDFDomenec MadridNo ratings yet

- Examenes Corregidos Interface de Computadores UPCDocument45 pagesExamenes Corregidos Interface de Computadores UPCJosuéNo ratings yet

- Microones 2010 Primavera FINAL No ProblemasDocument12 pagesMicroones 2010 Primavera FINAL No ProblemasMarianela SaraviaNo ratings yet

- Exercicis Operacions Amb Sist. BinariDocument7 pagesExercicis Operacions Amb Sist. BinariDavid Sánchez MasNo ratings yet

- Exercicis LabDocument25 pagesExercicis LabLurdes VidalNo ratings yet

- 05.562 20141 PAC1 EnunciatDocument3 pages05.562 20141 PAC1 EnunciatdeskisiaoNo ratings yet

- Pau Elec18slDocument4 pagesPau Elec18slJOSEP MARIA BERGADANo ratings yet

- Introduccio SO-tipusDocument6 pagesIntroduccio SO-tipusNewLookNo ratings yet

- Pau Tecn18jlDocument8 pagesPau Tecn18jlArnau VaquerNo ratings yet

- Elec Dig Ex Recuperacio Febrer 16Document2 pagesElec Dig Ex Recuperacio Febrer 16Marc CañadaNo ratings yet

- Elec Dig Ex Recuperacio Febrer 17Document2 pagesElec Dig Ex Recuperacio Febrer 17Marc CañadaNo ratings yet

- Elec Dig Ex Recuperacio Febrer 13Document2 pagesElec Dig Ex Recuperacio Febrer 13Marc CañadaNo ratings yet

- Elec Dig Ex Gener 17Document3 pagesElec Dig Ex Gener 17Marc CañadaNo ratings yet