Professional Documents

Culture Documents

Digital System Desgin Prac 5

Uploaded by

quintqasCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Digital System Desgin Prac 5

Uploaded by

quintqasCopyright:

Available Formats

CSSE4010 – Digital System Design

Prac 5 – Implementation of a Digital FIR Filter

NOTE: Things can take time. So be prepared with the lab activity, do all the preliminary

designs and as much implementation as you can beforehand.

Design Task

You are required to implement the following digital filter (a finite impulse response (FIR) filter) on an

FPGA and test its performance.

"#

𝑦(𝑛) = & 𝑎! 𝑥(𝑛 − 𝑖)

!$%

Digital implementation of this filter is done using the Xilinx System Generator (or Model Composer)

tool flow, which integrates Matlab-Simulink and Xilinx Vivado tools to allow rapid prototyping of

digital signal processing (DSP) systems on FPGAs using a model-based structural approach. More

details on this tool flow are provided in supporting resources on Blackboard and also will be

provided during the lectures and labs. Unless you have an in-person practical session at 47-401 lab,

you should use the RDP connections to lab computers to complete this lab. Also, you must use only

the basic processing elements such as adders, multipliers, delays, multiplexers etc, to implement

your designs and you are not allowed to use system level Xilinx IP-blocks for DPS such as FIR filters,

FFTs etc.

1. Verify the operation of the filter using the Matlab code provided, which also produces the

filter coefficients. The filter is a low-pass filter and the provided Matlab script uses a two-

tone signal to verify the filter operation in software implementation.

2. Implement the filter using the Xilinx System Generator/Mode Composer tools in Matlab-

Simulink using the standard direct-form structure with no-pipelining and without any

optimisation. You will have to select appropriate fixed-point word lengths for both the input

(i.e. gateway in blocks) and the filter coefficients. Verify the correct operation of your

implementation by playing the output sound and also by comparing the output to the

output obtained from the software implementation. Obtain the FPGA resources, critical path

delay, maximum frequency, and throughput for this implementation using HDL netlist

generation and using Artix-7 series FPGA family as the target.

3. Now, optimise the above design using pipelining/register-retiming/data broadcast structure

(use one or a combination of these techniques covered in the lectures) as much as you can

to improve the critical path delay (i.e. time complexity) at the cost of area complexity. Also,

optimise the fixed-point word lengths as much as you can (i.e., by comparing the hardware

output to the software output and try to minimise the error between the two). Verify the

correct operation of the filter and obtain the FPGA resources, critical path delay, maximum

frequency, and throughput figures for this optimised implementation using HDL netlist

generation and using Artix-7 series FPGA family as the target. Tabulate your findings and

compare and contrast the two designs. Hint: plot the distribution of filter coefficients and

make use of any observation there to optimise the implementation further.

4. Optionally (i.e., not assessed), hardware co-simulate the optimised design on Nexsys 4 FPGA

board and verify the functionality.

Prac 5 – Implementation of a digital FIR filter Page 1

CSSE4010 – Digital System Design

Report Content and Format

A typeset PDF report must be submitted by the due date with the following content:

Introduction stating the problem description, any assumptions, and design objectives

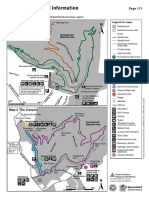

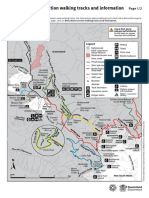

Design description including a block diagram explaining the complete design. Block diagrams should

be drawn using standard symbols for inputs/outputs, signals and busses as shown below.

• Block diagram (either drawn or a screenshot from the System Generator model with clear

labelling of input, output, and basic functional blocks being used), functional verification (i.e.

a plot showing the software and hardware outputs or an error figure between the two), and

FPGA resources, speed, throughput performance of the un-optimised design

• Block diagram (either drawn or a screenshot from the System Generator model with clear

labelling of input, output, and basic functional blocks being used), functional verification (i.e.

a plot showing the software and hardware outputs or an error figure between the two), and

FPGA resources, speed, throughput performance of the optimised design

• Selected system word lengths and how you obtained them (i.e. justification)

• Comparison of the two designs

• Conclusion – a reflection of what you’ve achieved in this exercise, problems (if you had any)

and potential improvements to your design (if any)

• References (if any)

• You must have the marking sheet on the next page as the last page of your report and your

marks will be indicated on this sheet (this has also been uploaded on BB as a single pdf file

so that you can append this to your report as the last page)

Prac 5 – Implementation of a digital FIR filter Page 2

CSSE4010 – Digital System Design

Marking Criteria

The pracs in this course are marked to a specific criteria. This means you must demonstrate

sufficient understanding and functionality and the marking will be done according to the rubric

provided below. You must attempt each prac (i.e., a report must be received by the due date) to

pass the course. All designs VHDL code used must be your own work. You are NOT permitted to use

other VHDL code sources, unless directed to. Plagiarism is unacceptable and please read and

understand the School Statement on Misconduct, available on the ITEE website

at: http://www.itee.uq.edu.au/itee-student-misconduct-including-plagiarism .

Marks Criteria

Simulation

0 Not sufficient results are provided

1 Results shown only for the un-optimised design – working correctly

2 Results shown only for the optimised design – working correctly

3 Results shown for both designs - working correctly

4 Both designs are working correctly, and a comparison is provided

Report

0 No evidence of content or work

1 Some content, insufficient explanation of circuit

2 Reasonable content, some explanation of circuit (both approaches are explained)

3 Good content, reasonable explanation of circuit (both approaches are explained)

4 Excellent content, good explanation of circuit (both approaches are explained)

Oral assessment

0 No knowledge of the design

1 Very little knowledge of the design

2 Reasonable knowledge of the design

3 Good knowledge of the design.

4 Excellent knowledge of the design.

Total (12): Marker Initials:

Date:

Prac 5 – Implementation of a digital FIR filter Page 3

You might also like

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (122)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (74)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (897)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (345)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (589)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (842)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (401)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5806)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1091)

- Digital System Desgin Prac 1Document7 pagesDigital System Desgin Prac 1quintqasNo ratings yet

- Digital System Desgin Prac 4Document3 pagesDigital System Desgin Prac 4quintqasNo ratings yet

- Digital System Desgin Tutorial 5Document1 pageDigital System Desgin Tutorial 5quintqasNo ratings yet

- Digital System Desgin Lecture 8Document17 pagesDigital System Desgin Lecture 8quintqasNo ratings yet

- Lect6 AnnotatedDocument35 pagesLect6 AnnotatedquintqasNo ratings yet

- LEC4Document47 pagesLEC4quintqasNo ratings yet

- Between Impunity and Accountability EnglishDocument28 pagesBetween Impunity and Accountability EnglishquintqasNo ratings yet

- Intelligent Neural Network Based STLF: January 2009Document12 pagesIntelligent Neural Network Based STLF: January 2009quintqasNo ratings yet

- Digital System Desgin Tutorial 6Document6 pagesDigital System Desgin Tutorial 6quintqasNo ratings yet

- Digital System Desgin Course OutlineDocument1 pageDigital System Desgin Course Outlinequintqas100% (1)

- Workforce TimesheetDocument1 pageWorkforce TimesheetquintqasNo ratings yet

- Springbrook Inset MapsDocument3 pagesSpringbrook Inset MapsquintqasNo ratings yet

- Flight Details: Travel History DeclarationDocument6 pagesFlight Details: Travel History DeclarationquintqasNo ratings yet

- آکورد گیتار آهنگ چشم من از داریوش - لامینور PDFDocument8 pagesآکورد گیتار آهنگ چشم من از داریوش - لامینور PDFquintqasNo ratings yet

- Lamington Green Mts MapDocument2 pagesLamington Green Mts MapquintqasNo ratings yet

- آکورد گیتار آهنگ عاشقانه از فرزاد فرزین - لامینور PDFDocument12 pagesآکورد گیتار آهنگ عاشقانه از فرزاد فرزین - لامینور PDFquintqasNo ratings yet

- Vivado Design FlowDocument39 pagesVivado Design FlowquintqasNo ratings yet

- Week 5 Tutorial: GoalsDocument2 pagesWeek 5 Tutorial: GoalsquintqasNo ratings yet

- آکورد گیتار آهنگ بی قرار از امین حبیبی - لامینور PDFDocument5 pagesآکورد گیتار آهنگ بی قرار از امین حبیبی - لامینور PDFquintqasNo ratings yet

- Afghanistan: Current Health Expenditure by Revenue SourcesDocument2 pagesAfghanistan: Current Health Expenditure by Revenue SourcesquintqasNo ratings yet

- Prac 2 - Registers and Combinational Logic in VHDL: Design TaskDocument4 pagesPrac 2 - Registers and Combinational Logic in VHDL: Design TaskquintqasNo ratings yet

- Eng Us PDFDocument54 pagesEng Us PDFquintqasNo ratings yet

- Sustainability 10 02022 PDFDocument18 pagesSustainability 10 02022 PDFquintqas0% (1)

- Csse1001 NotesDocument184 pagesCsse1001 NotesquintqasNo ratings yet

- 100 Renewal Energy Tri Fold ACCESSDocument6 pages100 Renewal Energy Tri Fold ACCESSquintqasNo ratings yet

- Woodside Sustainability Dev Fact Sheet Eng Final Web PagesDocument4 pagesWoodside Sustainability Dev Fact Sheet Eng Final Web PagesquintqasNo ratings yet

- Building PowerlinesDocument28 pagesBuilding PowerlinesquintqasNo ratings yet

- Wind Farms A Guide For CommunitiesDocument15 pagesWind Farms A Guide For CommunitiesquintqasNo ratings yet