Professional Documents

Culture Documents

Unit III

Uploaded by

ionightbotCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Unit III

Uploaded by

ionightbotCopyright:

Available Formats

Unit III

FET- Filed Effect Transistor: JFET & MOSFET

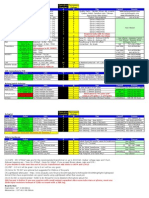

BJT FET/JFET

Three Terminal Device Three Terminal Device

It is Current Controlled Device It is Voltage Controlled Device

IC = f(IB) ID = f(VGS)

It is a Bipolar Device It is a Unipolar Device

Low Input Impedance High Input Impedance

Less temperature Stable More temperature Stable

Size is large as compared to JFET Smaller in Size

Linear Amplifier Non-Linear Amplifier

Power Consumption is High Power Consumption is Low

NPN or PNP n-channel & p-channel

VBE =0.7 V IG = 0 A

𝑽𝑮𝑺 𝟐

IC = βIB 𝑰𝑫 = 𝑰𝑫𝑺𝑺 (𝟏 − )

𝑽𝑷

Application of BJT and FET are Same, i.e. for amplification and switching

In both devices the output quantity is controlled by input parameter of the circuit

What does Field-Effect mean in the name Field Effect Transistor.

Course Instructor: Dr. M. R Mahboob

Course Code: EE223/ Analog Electronic Circuits

In case of FE transistor an electric field is develop by the charge present and this electric field

controls the conduction path of the output circuit. So, there is an effect due to electric field and

that’s why the name as Field-Effect Transistor.

n-channel JFET (Junction Field Effect Transistor)

The JFET is a three-terminal device with one terminal capable of controlling the current

between the other two. In our future discussion we will take up only n-channel as we do in

BJT discussion (only npn type BJT) and the whole discussion will be valid on p-channel too.

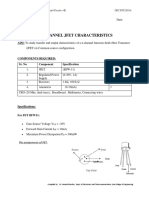

Construction of n-channel JFET

The basic construction of the n-channel JFET is shown in Fig. 3.1. Note that the major part of

the structure is the n-type material. A channel is formed between the two embedded layers of

p-type, and this channel is of n-type and that’s why the name n-channel JFET.

Fig.3.1. n-channel JFET construction

The JFET has four ohmic contacts. But the physical device has only three terminals as like

BJT.

The top of the n-type channel is connected through an ohmic contact to a terminal referred to

as the Drain (D), whereas the lower end of the same material is connected through an ohmic

contact to a terminal referred as the Source (S). The drain and the source are connected to the

ends of the n-type channel. The two p-type materials are connected together and referred as

Gate (G) terminal.

The JFET device has two p-n junctions at no-bias condition. And thus have two depletion

regions as shown in RED colour of Fig.3.1. As we know the depletion region (in a p-n junction

diode) is depleted of free charge carriers or no free charges are available. So, it will not help in

conduction.

Course Instructor: Dr. M. R Mahboob

Course Code: EE223/ Analog Electronic Circuits

However, if the width of depletion layer is increased gradually (somehow) then the width of n-

channel will also start reducing which lead to obstruction in the flow of electrons in the n-

channel.

Working of JFET:

The working of JFET can be divided for the purpose of understanding in two-part (i) VGS = 0

and (ii) VGS < 0. But for both these cases VDS > 0.

(i) VGS = 0 V, VDS some Positive Value

Fig. 3.2. JFET connected as per case (i) i.e. VGS = 0 and VDS > 0

The Gate to Source terminal is short circuited to ground for achieving VGS = 0 condition

whereas VDS is kept positive. A depletion region will be formed (as in Fig. 3.1) similar to the

Diode in no-bias condition as the voltage is still not applied at any terminals.

The instant the voltage VDD (=VDS) is applied, the electrons are drawn to the drain terminal,

establishing the conventional current ID with the defined direction of Fig. 3.2. The path of

charge flow clearly reveals that the drain and source currents are equivalent (ID = IS). Under

the conditions in Fig. 3.2, the flow of charge is relatively unstoppable and is only limited by

the resistance of the n-channel between drain and source.

However, the depletion layer width will also get affected. At the bottom of the transistor the

width of depletion region will remain same but at the top, it will increase as shown in Fig 3.2.

The reason for such a depletion region is the resistance offered by the n-channel to the flow of

current ID.

This can be understood by considering the n-channel, a combination of resistance (let’s say

four resistances of equal magnitude) connected in series as shown in Fig. 3.3. Also assume that

the Voltage VDS is 2 V. Then the voltage across the channel length will be distributed like 2V,

1.5V, 1.0V, 0.5V and 0. As the potential at the Gate terminal is 0V which means that the p-

Course Instructor: Dr. M. R Mahboob

Course Code: EE223/ Analog Electronic Circuits

type material is at zero volt, and the n-type material is at some positive potential which makes

the p-n junction reverse biased. At the top of depletion layer, a potential difference of 1.5V (as

1.5 V – 0 V) and it decreases as we move down in the n-channel as shown in Fig. 3.3. It is more

reverse biased at the top as compared to bottom region of depletion layer as shown in Fig. 3.3.

As we know, the greater the applied reverse bias, the wider is the depletion region

Fig. 3.3. Voltage (VDS = 2V) variation across the n-channel JFET

The fact that the p-n junction is reverse-biased for the length of the channel results in a Gate

current of ZERO amperes (IG = 0 A), as shown in the Fig. 3.3. The fact that IG = 0 A is an

important characteristic of the JFET.

As we applied little voltage across Drain to Source, a current ID will start to flow in the n-

channel. With the increase of VDS the current ID will also increases as per Ohm’s Law, but as

the VDS approaches to a voltage level Vp, the current ID will maintain a saturation level defined

as IDSS as shown in Fig. 3.4. It is the maximum drain current of the JFET when VGS = 0.

Fig. 3.4. ID Vs VDS curve at VGS = 0 or n-Channel JFET characteristics curve

Course Instructor: Dr. M. R Mahboob

Course Code: EE223/ Analog Electronic Circuits

The Voltage Vp is known as Pinch-off Voltage. The voltage VDS at which the two depletion

regions appear to touch each other at a point is known Pinch-off Voltage as shown in Fig. 3.5.

The pinch off stage results in reduction in n-channel width due to increased depletion region.

The reduced n-channel width will cause reduction in conduction path which lead to an increase

in resistance offered by conduction path as shown in the curve of Fig. 3.4.

Fig. 3.6. Pinch-off phenomenon at (VGS = 0 V, VDS = VP).

The more horizontal the curve, the higher the resistance, suggesting that the resistance is

approaching “infinite” ohms in the horizontal region.

The term pinch-off is little misleading as it suggests that the current ID is pinched off and drops

to 0 A whereas the current ID maintains a saturation level current (IDSS) and does not drop off

to ZERO as shown in Fig. 3.4. This is due to the existence of a very narrow channel along the

depletion region, with a current of very high density.

This can be understood as the absence of a drain current (ID) would remove the possibility of

different potential levels (i.e. 1.5V, 1.0, 0.5 V, 0V) through the n-channel material to establish

the varying levels of reverse bias along the p–n junction. The result would be a loss of the

depletion region distribution that caused the very pinch-off in the first place.

JFET as a constant current source

If VDS is increased beyond VP, it will start behaving like constant current source as revealed by

Fig. 3.4. This is due to the formation of thin channel along the length of two depletion region

due to the close encounter of two depletion regions (due to increase in VDS and thus the reverse

bias potential gets increases along the depletion region) and so the level of ID remains

essentially the same (IDSS).

If we go on increasing VDS, the current ID will not always remain equal to IDSS because the n-

channel will have the breakdown. It means the n-channel will not be able to withstand the high

potential difference across Drain and Source, this large voltage VDSmax causes high drain

current to flow through n-channel, where VDSmax is breakdown voltage of n-channel. It means

ID = IDSS holds true when VP < VDS < VDSmax.

Course Instructor: Dr. M. R Mahboob

Course Code: EE223/ Analog Electronic Circuits

The choice of notation IDSS is derived from the fact that it is the Drain-to-Source current with

a short-circuit connection from Gate to Source.

(ii) VGS < 0 V, VDS some Positive Value but less than the Case (i) voltage

The voltage VGS is the controlling voltage in JFET just as IB in BJT in CE configuration. The

prime aim of the current configuration is to obtain the saturation level (of current) even at lower

VDS as compared to previous case.

By bringing the drain current in saturation level, does not mean that the ID becomes equal to

IDSS. Because IDSS is the maximum drain current when VGS = 0. And in this case, we are not

putting VGS to zero so, that level of current cannot be achieve. The VDS in this case is less as

compared to case (i), so inorder to make the width of depletion layer same we need to put VGS

negative.

The further explanation of the JFET working is remain the same as in case (i).

But it can be noted that by applying negative bias to the Gate, the saturation level will be reach

at lower level of Drain to Source voltage (VDS)

Output or Drain characteristic of n-channel JFET

Output Characteristic Drain Characteristic

BJT JFET

IC Vs VCE ID Vs VDS

A curve between IC and VCE, at A curve between ID and VDS, at

various IB (i/p current) various VGS (i/p voltage)

The base current IB is the input current and a controlling current that controls the output current

IC in CE configuration of BJT. Similarly, the VGS is the controlling voltage that controls the

drain current (ID). In n-channel JFET VGS < 0 and p-channel JFET VGS > 0.

Let us consider we are trying to obtain the Drain Characteristic or Output Characteristic of n-

channel JFET with IDSS = 8 mA and VP = -4V.

For bringing JFET into maximum Drain current i.e. IDSS = 8 mA, VGS must put to Zero and VDS

should be greater than |VP| i.e.

[VGS = 0 and VDS ˃ |VP|]

When VDS = 0 V, then the electron present in n-channel will not be get drifted toward drain

and the current is zero. Now, if we increase VDS, ID will increase linearly and follow the Ohm’s

law upto the point ‘A’ in Fig. 3.7. If we keep on increasing the VDS, the depletion regions will

also increase and after some time it will appear that the two depletion regions touching each

other and when this happens (at point ‘B’) corresponding VGS is known as Pinch-off Voltage

(VP). At this moment the drain current ID will become constant known as IDSS because the

channel will become very narrow.

Now when VGS = -1V, (and VDS ˃ 0 V) it means that the Gate terminal is at negative potential

and so the p-type material connected to negative potential as Gate is connected to p-type

Course Instructor: Dr. M. R Mahboob

Course Code: EE223/ Analog Electronic Circuits

material. Similarly, the n-type material is connected to positive terminal as VDS is positive. So

the p-n junction is reverse biased in this case also.

If you are making VGS more and more negative, it means you are applying more negative

potential to the p-type material, and this will increase reverse biasing. When reverse biasing

increases, this implies the width of depletion layer will also increase. So the pinch off will be

achieved at lower value of VGS. It means that making VGS more and more negative will help in

achieving the pinch-off more and more earlier as the two depletion layers will appear to touch

each other at lower VDS voltage.

Fig. 3.7 Output Characteristic of n-channel JFET and its region

The above explanation is valid for VGS = -2 V or -3V. For VGS = -4V, which is equal to Pinch-

off Voltage (VP). When you have VGS = VP, there is no need to apply VDS. When VDS is equal

to zero, means that the potential difference across the n-channel is zero even in that case also

the two depletion regions will touch each other. So if you increase VDS there will be no current.

The VP is not a constant quantity rather it depends on the VGS. But in Datasheet, the

manufacturers only provide one value for pinch-off voltage. Why?

What will happen if VGS is made positive?

Region of JFET

(i) Ohmic Region: In this region the ID is directly proportional to VDS. In the region JFET

behave like a constant resistance. Thus, the n-channel JFET is acting like a linear

device. It is also known as Voltage controlled Resistor Region. In this region JFET can

be used as variable resistor. As the slope (resistor) in this region is a function of

controlling voltage VGS.

𝒓𝟎

𝒓𝒅 = (𝟏)

𝑽𝑮𝑺 𝟐

(𝟏 − 𝑽 )

𝑷

r0 → Resistance at VGS = 0 V

rd → Resistance at particular VGS

Ex: If ro = 10 kΩ (VGS = 0 V, VP = -6 V), At VGS = -3 V, resistance will be ? (40k)

➢ On decreasing VGS, the resistance JFET will increase

Course Instructor: Dr. M. R Mahboob

Course Code: EE223/ Analog Electronic Circuits

(ii) Active Region/Saturation Region/Pinch-off Region: The region starting from the

point when ID become constant and will remain constant is known as Active Region.

(iii) Cutoff Region: When VGS is equal to Pinch off Voltage (VP) then the ID become 0

Amps. The VGS required to make ID equal to zero amp is called as Gate Source Cut-off

voltage and for all the practical purposes the device is turned off.

Transfer Characteristic of n-channel JFET

The transfer Characteristic is ID verses VGS plot keeping VDS constant. Transfer curve is

between Output current (ID) and input Voltage (VGS) keeping the output voltage (VDS) constant.

It is important to observe that Drain characteristic relates two output quantity whereas Transfer

Characteristic relates Output quantity with input-controlling quantity.

In BJT the Output Current (IC) is a function of Input current (IB) which is also a controlling

current, IC = f(IB) i.e. IC = βIB. This relationship is linear as β is constant. But in case JFET

there is no linear relationship between the Output current (ID) and controlling voltage or input

voltage VGS. The relationship between ID and VGS is defined by Shockley’s Equation as:

𝑽𝑮𝑺 𝟐

𝑰𝑫 = 𝑰𝑫𝑺𝑺 (𝟏 − ) (𝟐)

𝑽𝑷

The Eq.(2) is non-linear because of the Square term. If VGS is reduced the ID will increase and

that too exponentially. There are two ways to obtain Transfer Characteristic the first is through

Eq(2) and second is by Output Characteristic or Drain Characterise Curve.

Fig. 3.8. Left Side: Transfer Characteristic Curve in Blue

SYMBOL

Comparison of BJT and JFET

Course Instructor: Dr. M. R Mahboob

Course Code: EE223/ Analog Electronic Circuits

Fig. 3.9 JFET symbols: (a) n-channel; (b) p-channel

Q: The device parameter of n-channel JFET are: Maxm Drain current (IDSS) = 10 mA and Pinch-

off Voltage (VP) = -4 V. Calculate the drain current for VGS = 0V; -1V; -4V

Q: A JFET produces a Gate current of 2nA when Gate is reverse biased with 8V. Determine

the resistance between Gate and Source.

Q: The Pinch-off voltage for n-channel JFET is 4 V, then Pinch-off occurs for VDS, when VGS

= -1 V is (a) 1V (b) 3 V (c) 4V (d) 5V

Course Instructor: Dr. M. R Mahboob

Course Code: EE223/ Analog Electronic Circuits

MOSFET

(Metal Oxide Semiconductor Field Effect Transistor)

MOSFET is another type of Field Effect Transistor. MOSFET is an active device (like BJT,

JFET) because it can amplify the signals or can control the flow of current. Passive Device

examples are Diode, Capacitor, Transformer. MOSFETs are of two types: Depletion type and

Enhancement type.

Depletion type and Enhancement type MOSFET are almost have same type of construction.

The only difference is the existence of channel between Drain and Source. Enhancement type

MOSFET do not have channels from the beginning whereas Depletion type do have.

n-channel Depletion type n-channel Enhancement type

Fig. 3.10 Construction of n-channel Depletion MOSFET n-channel Enhancement MOSFET

Construction of n-channel Depletion type MOSFET:

A slab of p -type material also known as substrate is the foundation of n-channel MOSFET.

Substrate is a material on which a device or sensor is normally constructed/fabricated. The

substrate is denoted or labelled as SS. The two n-type wells are formed on the p-type substrate.

The one n-type-well through metal contact is connected to Drain terminal and other with

Source terminal. The Drain and Source are connected through the n-channel (n-doped regions)

as shown in Fig. 3.10. The Gate terminal is also connected to a metal contact surface but

remains insulated from the n -channel. A very thin silicon dioxide (SiO2) layer is provided to

act as insulator or dielectric. The SiO2 layer is kept very thin to control the surface near the

Course Instructor: Dr. M. R Mahboob

Course Code: EE223/ Analog Electronic Circuits

Gate electrode. It means that NO direct electrical connection between the gate terminal and the

channel of a MOSFET.

It is the insulating layer of SiO2 in the MOSFET construction that accounts for the very

desirable high input impedance of the device. Because of the very high input impedance, the

Gate current (IG) is essentially 0 A for DC biased configurations. MOSFET is also known as

IGFET due to the insulating layer between the Gate and the channel.

Working of n-channel Depletion type MOSFET:

The working of n-channel Depletion type MOSFET is somewhat similar to n-channel JFET.

But there is one extra feature in D-MOFET in comparison to JFET. It will be cover in the

lecture shortly.

MOSFET is 4 terminal devices, However, the Substrate terminal (SS) is generally shorted

internally to the Source terminal. The n-channel is there from the beginning in both the D-

MOSFET as well as JFET. As the channel is already there like JFET so we can start our

discussion from VGS = 0 V. A positive voltage VDS is applied across Drain and Source terminal

as Shown in Fig. 3.11.

(i) Case I: VGS = 0 V

Fig 3.11. (a) n-channel D-MOSFET with VGS = 0, and (b) n-channel D-MOSFET with VGS = 0, and

applied VDS applied VDS1 (VDS1> VDS)

On increasing voltage VDS What will happen to current ID. As the Voltage VDS is increasing.

means we are making Drain terminal more positive. It means more electrons attracted toward

the Drain terminal so the drain current (ID) will increase. But after some time, the drain current

will become constant, after this even if you increase voltage VDS, ID will remain the same.

Let us try to understand why the current (ID) become constant. As the drain terminal becoming

more positive due to increase of voltage VDS. The positive potential at n-type material is

increasing, it means that the p-n junction is becoming more reverse bias. So the width of

depletion region will increase and due to this the n-channel will become narrow. If we go on

increasing the VDS, the channel will become very narrow and only limited amount of electron

will pass so the current ID will become constant. This effect is like JFET. If we increase VDS,

Course Instructor: Dr. M. R Mahboob

Course Code: EE223/ Analog Electronic Circuits

Pinch-off occur and in that condition, the maximum drain current will flow known as IDSS, and

thus ID will become constant which is equal to IDSS.

In case of JFET, IDSS is known as the maximum current of JFET, which it can hold, and it

occurs at VGS = 0V, but in case of D-MOSFET, the current IDSS at VGS = 0V is not the maximum

current and can have more current than IDSS when VGS made positive.

In JFET VGS ≤ 0V, because for positive value of VGS it cannot work whereas MOSFET can.

This is the extra feature of MOSFET as compared to JFET.

So the MOSFET have three cases to understand (i) VGS = 0V (ii) VGS < 0V (iii) VGS > 0V.

The case (i) has already been discussed above whereas in case (ii) VGS become negative or less

than zero which means the Gate terminal subjected to negative potential. The negative potential

will set up electric field in reverse direction. The field will push the electrons present in the n-

channel toward the p-type substrate and also attract the holes present in the p-type material of

substrate toward the Gate terminal as shown in Fig 3.12.

Fig 3.12. MOSFET electron distribution at negative V GS

There are two actions which are happening at VGS < 0V, first is the pushing of electrons from

the n-channel and second attraction of holes toward the Gate. Because of this the recombination

of electrons and holes will take place. This recombination will reduce the number of electrons

available in n-channel for conduction and thus reduces the drain current ID.

(ii) Case III: VGS > 0V

The positive potential at the Gate will draw the additional electrons from the p-type substrate,

the minority charge carrier (electrons) is there in the substrate and the collision will also occur

between the accelerating particles and a new carrier will be established, due to this drain current

ID will increase rapidly. In this scenario we must take care of the maximum drain current. The

voltage VDS must be increased with utmost care (upto safe level) because small change in VDS

will cause large change in ID.

Course Instructor: Dr. M. R Mahboob

Course Code: EE223/ Analog Electronic Circuits

Output Characteristic and Transfer characteristic of n-channel D-MOSFET.

Fig. 3.13 Drain And Transfer Characteristic of n-channel D-MOSFET

Construction & working of n-channel Enhancement type MOSFET

The construction of an enhancement-type MOSFET is quite similar to that of the D-MOSFET,

except for the absence of a channel between the drain and source terminals.

If we keep VGS = 0 V and apply a positive voltage across Drain to Source, there will be no flow

of current ID as the channel is not there as shown in Fig. 3.14.

Fig. 3.14. Absence of n-channel When VGS = 0V and VDS > 0

Non-formation of Channel result in zero drain current instead putting positive voltage VDS.

How is the n-channel formed is explain below?

Course Instructor: Dr. M. R Mahboob

Course Code: EE223/ Analog Electronic Circuits

The substrate is a p-type material having holes as majority charge carrier and electrons as

minority charge carrier.

As we apply some positive voltage across the Gate terminal (VGS = +ve value). It means that

we are making Gate terminal positive as compared to Substrate/Source terminal. Now, a

capacitor will be formed between the Gate terminal and the Substrate as two parallel plates.

The SiO2 will act as insulator between the two electrodes (Gate & Substrate). The positive

charges will accumulate over the Gate plate (as we are applying +ve voltage VGS) and negative

charges will accumulate on p-type substrate plate.

Actually, the substrate, which is p-type, is the body of the MOSFET having minority charge

carrier as electrons. Initially when VGS is low, electrons will accumulate near the surface of p-

type material. But if we increase VGS, then uncovering of negative immobile ions (negative

immobile ions have holes too) will take place because of which holes will be pushed down.

Now the surface near the SiO2 (inside p-type substrate) will become less p-type and then

become n-type due to excess charge due to negative immobile ions. This process is known as

INVERSION. In Inversion the p-type region inverted to n-type by keeping Gate terminal more

positive as compared to substrate. In this way an n-channel is formed as shown in Fig. 3.15. It

means increasing the VGS will lead to increase in channel width/depth.

Fig. 3.15. Formation of n-channel When VGS > 0 and VDS > 0

Now if we increase VGS the channel width will also increase and at a particular VGS the channel

width is sufficient to allow significant flow of current, the current will be the drain current ID,

this particular VGS is known as Threshold Voltage (VT). The voltage that results in a

significant amount of current flow from Drain to Source (ID) is known as VT.

However, if we hold VGS constant and increase the level of VDS , the drain current will

eventually reach a saturation level as occurred for the JFET and depletion-type MOSFET. The

saturation of ID is due to the pinching-off process due to the narrowing down of induced channel

at the Drain end.

For understanding the processes of pinch-off in Enhancement type MOSFET, the effect of

Voltage VDS on depletion layer is to be understood. For this purpose, the voltage VGD have to

be find out. 𝑽𝑮𝑫 = 𝑽𝑮 − 𝑽𝑫 = 𝑽𝑮𝑺 − 𝑽𝑫𝑺

Course Instructor: Dr. M. R Mahboob

Course Code: EE223/ Analog Electronic Circuits

Now, based on the voltage across VGD, three cases will be formed.

Case I: Uniform Depletion Region: VDS = 0 ⟹ Drain to Source is short circuited

𝑽𝑮𝑫 = 𝑽𝑮𝑺 − 𝑽𝑫𝑺

VDS = 0, ⟹ 𝑽𝑮𝑫 = 𝑽𝑮𝑺 − 𝟎 ⇒ 𝑽𝑮𝑫 = 𝑽𝑮𝑺

The above expression implied that the voltage across Gate to Source becomes equal to voltage

across Gate to Drain if the Drain to Source is short circuited i.e. VDS = 0. In this situation, the

potential across the two p-n junctions become equal and thus the width of depletion layer will

be uniform as shown in Fig. 3.16. The two p-n junction region are shown by Region 1 and

Region 2.

Fig. 3.16. Formation of Uniform n-channel When VDS = 0 V or VGS = VGD

Let us suppose that the VT = 1V and applied VGS = 2V, and Drain to Source is short circuited,

It implies that VGD will also become equal to 2V. If this is the situation, then the channel width

become sufficient to establish the Drain current as VGS ˃ VT. The width of established channel

will be corresponding to the Excess Voltage.

𝐸𝑥𝑐𝑒𝑠𝑠 𝑉𝑜𝑙𝑎𝑡𝑔𝑒 𝑜𝑟 𝐸𝑓𝑓𝑒𝑐𝑡𝑖𝑣𝑒 𝑉𝑜𝑙𝑎𝑡𝑔𝑒 = 𝑉𝐺𝑆 − 𝑉𝑇

The Excess Voltage determines the width of depletion region in Case I. (when 𝑽𝑮𝑫 = 𝑽𝑮𝑺 )

Case II: VDS ˃ 0, ⟹ 𝑽𝑮𝑫 (↓) = 𝑽𝑮𝑺 − 𝑽𝑫𝑺 (↑)

Again, keeping VGS fixed as in Case I for the purpose of comparison, If VDS is increased, it

implies from above equation that VGD will decrease. It means that Drain is becoming more

positive in comparison to Case I. As, the VGD ≠ VGS which implies that the depletion layer will

no longer be uniform as shown in Fig 3.17.

Let us assume now VDS = 1.5 V then 𝑽𝑮𝑫 = 𝟎. 𝟓 𝑽, earlier it was 2V when VDS = 0V in

Case I, whereas VGS is still equal to 2 V as it was fixed.

The Region 1 in Fig. 3.17 will having less positive voltage as compared to Region 2. Because

of this, the width of n-channel will reduce, and width of depletion region will increase and this

is happening because there is reduction in the attraction forces for the negative charges and due

to this width of depletion region will increase in Region 1.

Course Instructor: Dr. M. R Mahboob

Course Code: EE223/ Analog Electronic Circuits

Fig. 3.17. Formation of Non-uniform n-channel When VDS ˃ 0 V

Special Situation in Case II when VDS = VGS - VT ⟹ VGD = VT

If the Voltage across VDS is varied in such a way that above condition satisfy, then the Pinch-

off occurs. At this voltage the channel will be reduced to the point of pinch-off and a saturation

condition will be established as described earlier for the JFET and depletion-type MOSFET.

In other words, any further increase in VDS at the fixed value of VGS will not affect the saturation

level of ID until breakdown conditions are encountered.

The Voltage VGS is known as VDSsat i.e. VDSsat = VGS - VT

Output or Drain Characteristic of E-MOSFET

A plot between the Output Current ID and Output voltage VDS for various levels of control

variable or control voltage VGS which is the Input voltage. In case of E-MOSFET Threshold

voltage (VT) and constant ‘k’ is given.

Let us suppose a E-MOSFET with VT = 2 V and k = 0.278 x 10-3 A/V2. Now we need to plot

the Drain Characteristic for VGS1 = 8V; VGS2 = 7V; VGS3 = 6V; VGS4 = 5V; VGS5 = 4V, VGS6 =

3V.

We know that the channel width depends upon the excess voltage = V GS -VT. If the VDS

become equal to this excess voltage, then the pinch-off condition occur, and the current ID

become constant as shown in Fig. 3.18.

Course Instructor: Dr. M. R Mahboob

Course Code: EE223/ Analog Electronic Circuits

Fig. 3.18 Drain And Transfer Characteristic of n-channel E-MOSFET

a) Saturation region (Active Region): 𝑽𝑫𝑺 ≥ 𝑽𝑮𝑺 − 𝑽𝑻

𝐼𝐷 = 𝑘(𝑉𝐺𝑆 − 𝑉𝑇 )2

b) Ohmic Region (Triode Region): 𝑽𝑫𝑺 < 𝑽𝑮𝑺 − 𝑽𝑻

2

𝑉𝐷𝑆

𝐼𝐷 = 2𝑘 [(𝑉𝐺𝑆 − 𝑉𝑇 )𝑉𝐷𝑆 − ]

2

c) Cut-off Region: 𝑽𝑮𝑺 < 𝑽𝑻

𝐼𝐷 = 0

Q: Does the current of an E-MOSFET increases at same rate as a D-MOSFET for conduction

region?

Q: Find VT, if k = 0.4 x10-3 A/V2; ID(on) = 3.5 mA; VGS(on) = 4V

Q: Given ID = 4mA at VGS = -2V. Determine the saturation current if VP = -4V.

Course Instructor: Dr. M. R Mahboob

Course Code: EE223/ Analog Electronic Circuits

DC Analysis of FET

There are three types of FET we have discussed and namely JFET, D-MOSFET and E-

MOSFET.

The BJT DC analysis involves the DC biasing of BJT to fix the operating point or Q-point at

which BJT works. Precisely finding the ICQ and VCEQ (in case of CE Configuration). There are

two approaches or method to find or determine the Q-point. (i) Mathematical approach and (ii)

Graphical approach.

Although we had discussed both the approaches, but mainly mathematical approach has been

followed to obtain the Q-point. The mathematical approach is suitable for linear devices but in

non-linear devices (or device with non-linear characteristic curve) the mathematical approach

may increase the complexity of the solution process. So, in those situation Graphical method

make our path easy to obtain the Q-point.

Types of Biasing for FET/JFET

1) Fixed Bias Configuration

2) Self-Bias Configuration

3) Voltage Divider Configuration

4) Common Gate Configuration

Types of Biasing for FET/E-MOSFET

1) Feedback Biasing Arrangement

2) Voltage Divider Biasing Arrangement

Course Instructor: Dr. M. R Mahboob

Course Code: EE223/ Analog Electronic Circuits

E-MOSFET

Course Instructor: Dr. M. R Mahboob

Course Code: EE223/ Analog Electronic Circuits

Q: Determine ID , VGS , and VDS for the network of

Q Q

Course Instructor: Dr. M. R Mahboob

Course Code: EE223/ Analog Electronic Circuits

You might also like

- How To Read Circuit DiagramsDocument28 pagesHow To Read Circuit DiagramsMegaV100% (1)

- Power ElectronicsDocument276 pagesPower ElectronicsBikrant PoudelNo ratings yet

- Chapter 10 Field Effect Transistors PDFDocument48 pagesChapter 10 Field Effect Transistors PDFVikas PsNo ratings yet

- Easy(er) Electrical Principles for General Class Ham License (2019-2023)From EverandEasy(er) Electrical Principles for General Class Ham License (2019-2023)No ratings yet

- Unit - Vi Field Effect TransistorDocument16 pagesUnit - Vi Field Effect TransistorBhavaniPrasadNo ratings yet

- Controlled Devices FET, BJT, IGBTDocument51 pagesControlled Devices FET, BJT, IGBTHolloGramNo ratings yet

- Edc 4 UnitDocument26 pagesEdc 4 UnitAnonymous 6Ts3r7dwNo ratings yet

- MODULE 1 - FET - WatermarkDocument16 pagesMODULE 1 - FET - WatermarkAnupama MohananNo ratings yet

- Field Effect Transistors (FET) : Comparison Between BJT and FETDocument9 pagesField Effect Transistors (FET) : Comparison Between BJT and FETpranavraikar1No ratings yet

- Unit 3 Field Effect Transistor JfetDocument21 pagesUnit 3 Field Effect Transistor Jfetrakesh hudedNo ratings yet

- Bipolar Junction Transistor (BJT) Junction Field Effect Transistor (JFET)Document5 pagesBipolar Junction Transistor (BJT) Junction Field Effect Transistor (JFET)sgmdhussainNo ratings yet

- Chapter5 FET PDFDocument12 pagesChapter5 FET PDFJ VikasNo ratings yet

- The Basic Structure: Field Effect TransistorDocument10 pagesThe Basic Structure: Field Effect TransistormokhaladNo ratings yet

- Unit 4 JFETDocument13 pagesUnit 4 JFETpranjaldesai453No ratings yet

- JFET TouhidDocument32 pagesJFET TouhidA.K.M.TOUHIDUR RAHMANNo ratings yet

- Semiconductorfet, Called A Misfet) - A Common Special Case of This Type Uses An Oxide Layer As TheDocument10 pagesSemiconductorfet, Called A Misfet) - A Common Special Case of This Type Uses An Oxide Layer As TheShoumil SachanNo ratings yet

- Field Effect Transistor (FET)Document4 pagesField Effect Transistor (FET)Chalez Zengeretsi100% (1)

- Chapter ForDocument17 pagesChapter Forbelacheweshetu222No ratings yet

- Chapter 4Document16 pagesChapter 4firomsaguteta12No ratings yet

- Unit 5 - Electronic Devices - WWW - Rgpvnotes.inDocument17 pagesUnit 5 - Electronic Devices - WWW - Rgpvnotes.inprakharNo ratings yet

- Notes Module2 (FET Part) Basic Electronics 22BBEE203Document12 pagesNotes Module2 (FET Part) Basic Electronics 22BBEE203Hani MNo ratings yet

- Field Effect Transistor NotesDocument21 pagesField Effect Transistor NotessaraswatnidhiNo ratings yet

- Module 2Document51 pagesModule 2eswarsenthil2004No ratings yet

- Unit I - FETDocument19 pagesUnit I - FETJadhav BhagavatNo ratings yet

- Ece-Research Work 1Document10 pagesEce-Research Work 1Peale ObiedoNo ratings yet

- B.E. FETs and Other Components NotesDocument12 pagesB.E. FETs and Other Components NotesLaxman SalianNo ratings yet

- Electronics Chapter 4Document16 pagesElectronics Chapter 4YidnekachewNo ratings yet

- ElectronicsDocument22 pagesElectronicsVARSHITH REDDY JNo ratings yet

- Chapter 10 Field Effect TransistorsDocument48 pagesChapter 10 Field Effect TransistorsanjugaduNo ratings yet

- 2.JFET V-I Characteristics 1696413359800Document8 pages2.JFET V-I Characteristics 1696413359800ansh kumarNo ratings yet

- Chapter 4 Ele IDocument16 pagesChapter 4 Ele Ibiruk satnawNo ratings yet

- Lecture 8Document14 pagesLecture 8Altaher Bushra AdamNo ratings yet

- ECE 027 - Module 5 Field Effect TransistorDocument102 pagesECE 027 - Module 5 Field Effect TransistorMiyuki NakiriNo ratings yet

- Electronic II-1Document10 pagesElectronic II-1Isaac DanielNo ratings yet

- Observations: Experimental ValuesDocument7 pagesObservations: Experimental ValuesShibeshwar MandalNo ratings yet

- Field Effect TransistorsDocument4 pagesField Effect TransistorsdwaswaNo ratings yet

- JFETDocument25 pagesJFETsakibNo ratings yet

- IV. Field Effect Transistor CompleteDocument42 pagesIV. Field Effect Transistor Completegarlic breadNo ratings yet

- Module2b BEEDocument15 pagesModule2b BEEmd hasanNo ratings yet

- Regulation - 2018: Basic Electronics-18ELN14Document12 pagesRegulation - 2018: Basic Electronics-18ELN14DaisyQueenNo ratings yet

- Chapter 4Document15 pagesChapter 4Gizachew BalchaNo ratings yet

- 7 JFET CharacteristicsDocument22 pages7 JFET CharacteristicsAnsar AnsarNo ratings yet

- V DR - RR&DR - SR Techincal University Lab Manual: EltechDocument25 pagesV DR - RR&DR - SR Techincal University Lab Manual: EltechadiprasanthNo ratings yet

- Jfet's & Mosfet'sDocument62 pagesJfet's & Mosfet'sBabu GundlapallyNo ratings yet

- Field Effect Transisters (FET)Document22 pagesField Effect Transisters (FET)Raja PosupoNo ratings yet

- Field Effect Transistor, Ujt, SCR, Triac: Scope of The ChapterDocument8 pagesField Effect Transistor, Ujt, SCR, Triac: Scope of The ChapterAkhilesh PandeNo ratings yet

- Expt - 11: JFET CharacteristicsDocument8 pagesExpt - 11: JFET CharacteristicssamarthNo ratings yet

- Chapter 5Document31 pagesChapter 5api-394738731No ratings yet

- Field Effect TransistorDocument23 pagesField Effect TransistorkurakidNo ratings yet

- Edc - Unit 5Document37 pagesEdc - Unit 5GANGADHARA SAIPRASANNANo ratings yet

- EDC Unit 6 FETDocument30 pagesEDC Unit 6 FETmuralitmpsNo ratings yet

- JFET and MOSFET CharacteristicsDocument56 pagesJFET and MOSFET CharacteristicsHarry Chandhu100% (1)

- DEE20023 Chapter 4 JUNCTION FIELD EFFECT TRANSISTOR SESI II 20222023Document51 pagesDEE20023 Chapter 4 JUNCTION FIELD EFFECT TRANSISTOR SESI II 20222023Muhd ZarifNo ratings yet

- BEng FETDocument13 pagesBEng FETJai GaizinNo ratings yet

- Lecture 06Document21 pagesLecture 06Atika Mustari SamiNo ratings yet

- Edc-Unit4 Question&answerDocument21 pagesEdc-Unit4 Question&answerSAI JAHNAVINo ratings yet

- Regulation - 2018 Basic Electronics-18ELN14Document12 pagesRegulation - 2018 Basic Electronics-18ELN14Fairoz FairozNo ratings yet

- Expt 13 - JFET-CharaceristicsDocument8 pagesExpt 13 - JFET-CharaceristicssamarthNo ratings yet

- Analog and Digital Electronics (Subject Code: 17CS32) Lecturer NotesDocument59 pagesAnalog and Digital Electronics (Subject Code: 17CS32) Lecturer NotesKarthik v BhatNo ratings yet

- Electronics Hons C3 FET Field Effect TransistorDocument21 pagesElectronics Hons C3 FET Field Effect TransistorGawrav BaishyaNo ratings yet

- Unit 2Document69 pagesUnit 2KISHAN SHUKLANo ratings yet

- Leave DeptDocument1 pageLeave DeptionightbotNo ratings yet

- Btech Course Curriculum - 2018Document52 pagesBtech Course Curriculum - 2018ionightbotNo ratings yet

- Unit IIIDocument20 pagesUnit IIIionightbotNo ratings yet

- Zener DiodeDocument27 pagesZener DiodeionightbotNo ratings yet

- Em Lab Pranav Exp1-5Document22 pagesEm Lab Pranav Exp1-5ionightbotNo ratings yet

- BKD, Sessional 3Document13 pagesBKD, Sessional 3ionightbotNo ratings yet

- Discussion of The Importance of IGBT in Variable-Frequency DriveDocument6 pagesDiscussion of The Importance of IGBT in Variable-Frequency DriveakramNo ratings yet

- Hitachi FET AmplifiersDocument6 pagesHitachi FET AmplifiersRoldão VianaNo ratings yet

- (DATASHEET) - Proximity Schneider PDFDocument174 pages(DATASHEET) - Proximity Schneider PDFPhreakerNo ratings yet

- Test 07Document5 pagesTest 07Nihar RoyNo ratings yet

- Photoelectric Sensors: General SpecificationsDocument5 pagesPhotoelectric Sensors: General SpecificationsAnonymous AsIbqUNo ratings yet

- Prospectus 2016-17 HITEC UniversityDocument196 pagesProspectus 2016-17 HITEC UniversitySyed Adil Javed100% (2)

- DIY Club Project 1 Part 14 v03Document25 pagesDIY Club Project 1 Part 14 v03Murilo RibasNo ratings yet

- Schmersal Catalogue: Delivering Certainty Hamer - Co.nzDocument29 pagesSchmersal Catalogue: Delivering Certainty Hamer - Co.nzFelipeNo ratings yet

- Power TransistorsDocument58 pagesPower Transistorssree haritha pNo ratings yet

- STN2907 (PNP Silicon Transistor) DatasheetDocument4 pagesSTN2907 (PNP Silicon Transistor) Datasheetfraile66No ratings yet

- PS 1Document37 pagesPS 1Aatif AltafNo ratings yet

- Physics - Important Questions and Answers, Entrance Exam, Study Material and Notes For All Subject - BrainKartDocument24 pagesPhysics - Important Questions and Answers, Entrance Exam, Study Material and Notes For All Subject - BrainKartKali Thaash100% (1)

- TRM 11Document62 pagesTRM 11God Killer100% (1)

- P MEZB1 1V10 BomDocument2 pagesP MEZB1 1V10 BomRadu TaşcăNo ratings yet

- 15 A - Cryo-CMOS - Voltage - Reference - in - 28-nm - FDSOIDocument4 pages15 A - Cryo-CMOS - Voltage - Reference - in - 28-nm - FDSOIBalaramamurty SannidhiNo ratings yet

- BJT Common Emitter Characteristics: Experiment 6Document5 pagesBJT Common Emitter Characteristics: Experiment 6beesahNo ratings yet

- Roubik Gregorian-Introduction To CMOS OP-AMPs and Comparators-Wiley (1999)Document369 pagesRoubik Gregorian-Introduction To CMOS OP-AMPs and Comparators-Wiley (1999)Maanas Khurana50% (2)

- Switching Applications Solenoid Drive Applications Temperature Compensated For Audio Amplifier Output StageDocument5 pagesSwitching Applications Solenoid Drive Applications Temperature Compensated For Audio Amplifier Output StageRanfis Rojas BorgesNo ratings yet

- Omron H3cr-A TimerDocument21 pagesOmron H3cr-A TimerAditya PrajasNo ratings yet

- BC517 NPN Darlington TransistorDocument3 pagesBC517 NPN Darlington Transistorz3xa5347No ratings yet

- Ec0221 Ed Lab ManualDocument68 pagesEc0221 Ed Lab ManualGoutham ShanNo ratings yet

- NCRC Electrical (Formatted, Draft 12) - July - 16 - 2022Document110 pagesNCRC Electrical (Formatted, Draft 12) - July - 16 - 2022hashir zamanNo ratings yet

- Sharp - VOLTAGE-REGULATORDocument15 pagesSharp - VOLTAGE-REGULATORLuiz Alberto MagriNo ratings yet

- Questions On Transistor CharacteristicsDocument72 pagesQuestions On Transistor Characteristicskibrom atsbha50% (2)

- Click To Buy: Linear Systems Replaces Discontinued Intersil IT130Document1 pageClick To Buy: Linear Systems Replaces Discontinued Intersil IT130StuxnetNo ratings yet

- BJ Transistors 3 of 8Document5 pagesBJ Transistors 3 of 8haseebiftikharNo ratings yet

- Datasheet 6c Silicon Digital Transistor PDFDocument12 pagesDatasheet 6c Silicon Digital Transistor PDFmiskoyu027No ratings yet

- Pulse Circuits - Blocking OscillatorsDocument6 pagesPulse Circuits - Blocking OscillatorsNakib AhsanNo ratings yet