Professional Documents

Culture Documents

IntegratedCircuitFamilies (Doc Them)

Uploaded by

Tấn NguyễnOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

IntegratedCircuitFamilies (Doc Them)

Uploaded by

Tấn NguyễnCopyright:

Available Formats

Lecture 9

Integrated Circuit Families

9.1 Introduction

The aim of this lecture is to introduce digital logic families. Logic circuits are grouped into

families, each with their own set of design requirements. The most common logic families are:

• TTL Transistor-Transistor Logic.

• ECL Emitter-Coupled Logic.

• CMOS Complementary Metal-Oxide Semiconductor.

• BiCMOS Bipolar-CMOS logic.

With the building of digital circuits with logic ICs, then there are five initial points to be

considered:

1. Fan-out.

2. Fan-in.

3. Unused inputs.

4. Power supply.

5. Power supply decoupling.

Fan-out

This is the number of logic inputs that can be driven from the output of a logic gate. A typical

fan-out for TTL is 10 (i.e. the output of a TTL logic gate can typically drive 10 TTL logic gate

inputs). For CMOS, the limiting factor is the capacitive load connected to the gate output – in

theory, any number of CMOS inputs can be driven, although the higher the capacitive load on the

logic gate output, the longer a logic value change takes to occur.

Fan-in

This is the number of logic outputs that can be connected to a logic gate input.

Unused inputs

It is common for discrete logic ICs for one or more of the available inputs to be redundant – they

are not needed to implement the logic circuit. However, the inputs will be present in the real

circuit and these inputs must not be left unconnected (referred to as floating inputs). If inputs are

MARE: Electronics: University of Limerick 1

th

Revision 24 September 2007

left floating, then unexpected behaviour of the circuit could occur. Unused inputs must be

connected to a logic value (0 or 1).

Power supply

Although the logic function occurs by connecting the data pins of the ICs together to form the

circuit, each IC will require a suitable power supply connection. TTL levels are +5 V / 0 V logic

and the IC power supply is +5 V. Other voltage levels are possible and used.

Power supply decoupling

It is common practice to decouple the power supply on each IC within a circuit. This power

supply decoupling will effectively short out any high frequency spikes, which can occur on the

power supply lines due to high switching speeds between the voltage levels determining the logic

levels. By placing a decoupling capacitor across the power supply pins of each IC, then these

spikes can be removed. Typically, a 100 nF ceramic capacitor is used.

Figure 9.1 shows an example of a quad 2-input AND gate IC with power supply connections.

VCC / VDD

GND

Figure 9.1. Power supply connections for a digital logic IC.

The fan-in and fan-out apply within a given logic family. If there is a need to interface between

two different logic families, care must be taken in order to meet the drive requirements and

limitations of both families, within the interface circuitry.

In the digital logic circuit, a logic level (0 or 1) will be created by a voltage with variance. A logic

level will be represented by a range of voltages between a minimum value to a maximum value.

The noise margin for a logic gate, see figure 9.2, will provide an indicator as to how tolerant a

logic gate is to variations in the signal voltages creating the logic value. These variations may be

due to noise that can be added to the signal from either neighbouring signal lines through

capacitive or inductive coupling, or from outside the system. This has the potential to corrupt the

MARE: Electronics: University of Limerick 2

th

Revision 24 September 2007

signal. The figure is for an inverter where an input voltage is applied to represent an input logic

level and an output voltage monitored to represent an output logic level.

Here, two voltages are identified (Vin and Vout) which represent the input and output voltages. For

each voltage, the following are defined:

VIL Maximum input voltage, which can be interpreted as a logic 0

VIH Minimum input voltage, which can be interpreted as a logic 1

VOL Maximum output voltage when the output is a logic 0

VOH Minimum output voltage when the output is a logic 1

Two values for noise margin are identified-

NML (Noise margin for low levels) NML = VIL - VOL

NMH (Noise margin for high levels) NMH = VOH - VIH

Vin Vout

Vin Vout

VOH

NMH

VIH

Transition region

VIL NML

VOL

Figure 9.2 Noise margin

Noise margin is a static characteristic of the device In addition to the static characteristics, the

CMOS inverter exhibits dynamic characteristics. Here, the output voltage changes due to a

dynamic change in the input voltage. The dynamic characteristics will determine the maximum

MARE: Electronics: University of Limerick 3

th

Revision 24 September 2007

operating frequency of the logic gate and will be dependent on the output load conditions. The

dynamic characteristics for the inverter are shown in figure 9.3. Here, a step change at the input

(with zero rise and fall times) is applied. The voltages vary from VOL (output voltage, low value)

to VOH (output voltage, high value).

Vin

VOH

VOL time

Vout τPHL

VOH

τPLH

Propagation delay V50%

times

VOL time

Vout

τfall τrise

V90%

Rise and fall times

V10%

time

Figure 9.3. Dynamic characteristics

The propagation delay is defined as the time taken for the output signal voltage to change by

50% between its initial and final values. High-to-Low (τPHL) and Low-to-High (τPLH) delays are

defined.

The rise and fall times are defined as the time taken for the output signal voltage to change

between 10% and 90% of the difference between the initial and final values. High-to-Low (fall -

τfall) and Low-to-High (rise - τrise) times are defined.

9.2 TTL

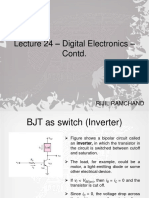

TTL (Transistor-Transistor Logic) is based on the Bipolar Junction Transistor (BJT). A family of

TTL devices is available. The basic families are identified in table 9.1.

MARE: Electronics: University of Limerick 4

th

Revision 24 September 2007

TTL Family Variant Description

74 Standard TTL

74AS Advanced Schottky

74ALS Advanced low-power Schottky

74F Fast

74H High-speed

74L Low-power

74LS Low-power Schottky

74S Schottky

LVTTL Low-voltage

Table 9.1. Selected TTL family variants

The input and output voltage levels for 74LSxx logic are shown in table 9.2.

Parameter 74LS

VOH (min) 2.7

VOL (max) 0.4

VIH (min) 2.0

VIL (max) 0.8

Table 9.2. 74LS family voltage levels

Example 74LSxx IC codes are shown in table 9.3.

Identifier Function

74LS00 Quad 2-input NAND gate

74LS02 Quad 2-input NOR gate

74LS04 Hex Inverter

74LS08 Quad 2-input AND gate

74LS32 Quad 2-input OR gate

74LS74 Dual Positive-Edge Triggered D-Type Bistable with Clear and Preset

74LS86 Quad 2-input EX-OR gate

74LS138 3-Line to 8-Line Demultiplexer

74LS157 Quad 2-Line to 1-Line Multiplexer

Table 9.3. Example 74LSxx ICs

9.3 ECL

ECL (Emitter Coupled Logic) was developed for high-speed operation and provides for faster

switching speeds than TTL. However, the power consumption of ECL logic is high.

MARE: Electronics: University of Limerick 5

th

Revision 24 September 2007

9.4 CMOS

CMOS (Complementary Metal Oxide Semiconductor) logic uses nMOS and pMOS transistors to

implement the required logic functions. CMOS was developed for low-power consumption and

CMOS logic ICs are provided with the same logic functions as TTL, but with a lower power

consumption. A family of CMOS devices is available. The basic families are identified in table

9.4.

CMOS Family Variant Description

4000 True CMOS (non-TTL levels)

74C CMOS with pin compatibility to TTL with same number

74HC Same as 74C but with improved switching speed

74HCT As with 74HC but can be connected directly to TTL

74AC Advanced CMOS

74ACT As with 74AC but can be connected directly to TTL

74AHC Advanced high-speed CMOS

74AHCT As with 74AHC but can be connected directly to TTL

74FCT Fast - CMOS - TTL inputs

LVCMOS Low-voltage CMOS

Table 9.4. Selected CMOS family variants

The input and output voltage levels for the 74HCxx logic family are shown in table 9.5.

Parameter 74HC

VOH (min) 4.44

VOL (max) 0.5

VIH (min) 3.5

VIL (max) 1.5

Table 9.5. 74HC family voltage levels

Example 74HCxx IC codes are shown in table 9.6.

Identifier Function

74HC00 Quad 2-input NAND gate

74HC02 Quad 2-input NOR gate

74HC04 Hex Inverter

74HC08 Quad 2-input AND gate

74HC32 Quad 2-input OR gate

74HC74 Dual Positive-Edge Triggered D-Type Bistable with Clear and Preset

74HC86 Quad 2-input EX-OR gate

74HC138 3-Line to 8-Line Demultiplexer

74HC157 Quad 2-Line to 1-Line Multiplexer

Table 9.6. Example 74HCxx ICs

MARE: Electronics: University of Limerick 6

th

Revision 24 September 2007

9.5 BiCMOS

BiCMOS logic uses both bipolar and CMOS transistors to implement the required logic

functions.

9.6 Conclusions

This lecture has introduced logic IC families and the basic characteristics and requirements for

building circuits with logic ICs. The basic logic technologies are Bipolar, CMOS and BiCMOS.

9.7 Further reading

Electronics Fundamentals: Circuits, Devices, and Applications, Sixth Edition, Thomas Floyd,

Prentice Hall, 2003, ISBN: 0131228846

Digital Fundamentals, Thomas Floyd, 2002, ISBN 0130942006

Electronics A Systems Approach 2nd Edition, Neil Storey, Addison-Wesley, 1998, ISBN 0-201-

17796-X

MARE: Electronics: University of Limerick 7

th

Revision 24 September 2007

You might also like

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet

- Chapter SixDocument5 pagesChapter Sixyunus memonNo ratings yet

- Digital Logic FamiliesDocument7 pagesDigital Logic FamiliesGirdhar GopalNo ratings yet

- High Speed Cmos LogicDocument12 pagesHigh Speed Cmos Logickwame83No ratings yet

- Digital Logic Families PDFDocument49 pagesDigital Logic Families PDFdineep90% (10)

- Exp1 - TTL Gate CharacteristicsDocument3 pagesExp1 - TTL Gate CharacteristicsMert DUMANNo ratings yet

- Rumpun IC LogikaDocument33 pagesRumpun IC LogikaFAZRI RENDI KURNIAWANNo ratings yet

- Logic Family Characteristics: Voltage DefinitionsDocument5 pagesLogic Family Characteristics: Voltage DefinitionsKotresh MaraliNo ratings yet

- Chapter 7 - IC Logic FamilyDocument33 pagesChapter 7 - IC Logic Familyswathich6No ratings yet

- DE ManualDocument37 pagesDE ManualKishore ReddyNo ratings yet

- Experiment No: 1: Title: Relevant TheoryDocument25 pagesExperiment No: 1: Title: Relevant TheorysonalibhagwatkarNo ratings yet

- Logic FamiliesDocument49 pagesLogic Familiesnour hijaziNo ratings yet

- Eie - Ee6301 DLC - Unit 1 NotesDocument82 pagesEie - Ee6301 DLC - Unit 1 Notesmoney_kandan2004No ratings yet

- High OH IH LOW IL OL: SS DDDocument3 pagesHigh OH IH LOW IL OL: SS DDTALLANo ratings yet

- EE 120 - Integrated Circuit FamiliesDocument15 pagesEE 120 - Integrated Circuit FamiliesAids SumaldeNo ratings yet

- Logic FamiliesDocument55 pagesLogic Familieslvsaru0% (1)

- Digital Electronics - Contd.: Rijil RamchandDocument24 pagesDigital Electronics - Contd.: Rijil RamchandAshna JoseNo ratings yet

- Logic FamiliesDocument55 pagesLogic FamiliesVishal BarotNo ratings yet

- DSD LogicFamiliesDocument32 pagesDSD LogicFamiliesibiiuoujNo ratings yet

- Exp No. 1Document11 pagesExp No. 1Arron BillNo ratings yet

- 74VHC541 Octal Buffer/Line Driver With 3-STATE Outputs: General DescriptionDocument7 pages74VHC541 Octal Buffer/Line Driver With 3-STATE Outputs: General Descriptionprdp_666No ratings yet

- Sonali Manual - 2nd August 2007Document78 pagesSonali Manual - 2nd August 2007sonalibhagwatkarNo ratings yet

- T2 2 LogicFamilyChar PDFDocument5 pagesT2 2 LogicFamilyChar PDFS M Shamim শামীমNo ratings yet

- Understanding Voltage Controlled Oscillators - DigiKeyDocument8 pagesUnderstanding Voltage Controlled Oscillators - DigiKeygezahegnNo ratings yet

- An 313Document8 pagesAn 313gurupalmurNo ratings yet

- Chương 4 - Official - E 2Document137 pagesChương 4 - Official - E 2Huy HoangNo ratings yet

- Chương 4 - Official - EDocument86 pagesChương 4 - Official - ENăng ĐứcNo ratings yet

- IC Logic Families: Wen-Hung Liao, PH.DDocument40 pagesIC Logic Families: Wen-Hung Liao, PH.DUmi SatiyahNo ratings yet

- Del Lab ManualDocument84 pagesDel Lab ManualRohit ChaharNo ratings yet

- Logic Gate Families: Learning ObjectivesDocument23 pagesLogic Gate Families: Learning Objectiveskalyan100% (1)

- Unit 4 Logic FamiliesDocument10 pagesUnit 4 Logic FamiliesJagat SinghNo ratings yet

- DLD Lab 01Document6 pagesDLD Lab 01fakhar_fastNo ratings yet

- Chapter 8Document85 pagesChapter 8edward solomonNo ratings yet

- Logic FamilyDocument51 pagesLogic FamilyTobey AustriaNo ratings yet

- Logic FamiliesDocument55 pagesLogic FamiliesVikram NagalgaonkarNo ratings yet

- Chapter 11Document89 pagesChapter 11lvsaruNo ratings yet

- Aacd99 BookDocument29 pagesAacd99 BookMahmoud HassanNo ratings yet

- Lecture 12 Interfacing Short Unit 4 PDFDocument15 pagesLecture 12 Interfacing Short Unit 4 PDFqawaNo ratings yet

- Chapter05 FinalDocument55 pagesChapter05 FinalMuhammed I'zwanNo ratings yet

- Digital Logic CircuitsDocument20 pagesDigital Logic Circuitssreekanthreddy peramNo ratings yet

- IC Logic Families: Wen-Hung Liao, PH.DDocument40 pagesIC Logic Families: Wen-Hung Liao, PH.Dvenkateshpandu11No ratings yet

- Glue Logic Family SelectionDocument6 pagesGlue Logic Family Selectionapi-3762100100% (1)

- ECL Emitter-Coupled Logic PDFDocument8 pagesECL Emitter-Coupled Logic PDFsunilkmch505682No ratings yet

- Logic Families and Their Characteristics CharacteristicsDocument26 pagesLogic Families and Their Characteristics CharacteristicsanunilaNo ratings yet

- Subj:Digital Design: R K TiwaryDocument31 pagesSubj:Digital Design: R K Tiwaryrktiwary256034No ratings yet

- Digital Integrated Circuits: Introduction To TTLDocument19 pagesDigital Integrated Circuits: Introduction To TTLpranav_naikNo ratings yet

- 74VHC273 29251Document15 pages74VHC273 29251Alfredo rodriguez gomezNo ratings yet

- IC Logic FamiliesDocument5 pagesIC Logic FamiliesAdarsha BhattaraiNo ratings yet

- Digital Electronics: Arslan Qamar Malik LecturerDocument165 pagesDigital Electronics: Arslan Qamar Malik LecturerSohail HabibNo ratings yet

- Lecture 09-IIDocument16 pagesLecture 09-IIzaidNo ratings yet

- Digital Electronics Course MaterialDocument54 pagesDigital Electronics Course MaterialMuhammad SalisNo ratings yet

- Unit 3Document66 pagesUnit 3Venky VellankiNo ratings yet

- Prepared By: Ankur ChangelaDocument28 pagesPrepared By: Ankur ChangelaHANSANo ratings yet

- Chap. 8 Integrated-Circuit Logic Families: Digital IC Technology Has Advanced RapidlyDocument45 pagesChap. 8 Integrated-Circuit Logic Families: Digital IC Technology Has Advanced RapidlyAdimoolam MalayalathanNo ratings yet

- SDIC 11marks (Q & A) (Unit 2)Document10 pagesSDIC 11marks (Q & A) (Unit 2)Ganapathy RamadossNo ratings yet

- Digital Logic FamiliesDocument26 pagesDigital Logic FamiliessatheeshNo ratings yet

- Data Sheet: 74HC/HCT240Document7 pagesData Sheet: 74HC/HCT240ALFREDO MORALESNo ratings yet

- Digital Electronics LAB ManualDocument61 pagesDigital Electronics LAB ManualKiranmai KonduruNo ratings yet

- Programming Fundamentals 2 Chapter 3:pointer: Miss:Hanan HardamDocument14 pagesProgramming Fundamentals 2 Chapter 3:pointer: Miss:Hanan HardampushpanjaliNo ratings yet

- 18-Width and Resistance Calculation of PMOS and NMOS in CMOS Logic-03!02!2022 (03-Feb-2022) Material - I - 03!02!2022 - 12a. - Width - Calculation - ofDocument8 pages18-Width and Resistance Calculation of PMOS and NMOS in CMOS Logic-03!02!2022 (03-Feb-2022) Material - I - 03!02!2022 - 12a. - Width - Calculation - ofAniket RanjanNo ratings yet

- PPL Unit-2-Mcqs-SheetDocument20 pagesPPL Unit-2-Mcqs-SheetYogesh SisodiaNo ratings yet

- Mosfet As A Switch: G G V GDocument34 pagesMosfet As A Switch: G G V GswaeroNo ratings yet

- LMA) ဝင္းထက္ဝင္း PICDocument207 pagesLMA) ဝင္းထက္ဝင္း PICThan LwinNo ratings yet

- Library Classes - Wrapper ClassDocument13 pagesLibrary Classes - Wrapper ClassNamrataNo ratings yet

- 34-Design of Synchronous Counters-24!03!2023Document17 pages34-Design of Synchronous Counters-24!03!2023Back upNo ratings yet

- Gerbang Logika DasarDocument30 pagesGerbang Logika DasarSoly Deo Glorya HutagalungNo ratings yet

- Lec13 FolDocument38 pagesLec13 FolParth MehtaNo ratings yet

- Predicate Logic: QuantifierDocument9 pagesPredicate Logic: QuantifierSoldsNo ratings yet

- Half Adder Is A Combinational Logic Circuit With Two Inputs and Two Outputs. It Is A Basic Building Block For Addition of Two Single Bit NumbersDocument27 pagesHalf Adder Is A Combinational Logic Circuit With Two Inputs and Two Outputs. It Is A Basic Building Block For Addition of Two Single Bit NumbersShahrukh TanekhanNo ratings yet

- Logic Gates (Word Problems)Document18 pagesLogic Gates (Word Problems)masterphlex21No ratings yet

- Digital Electronics and Logic Design LabDocument13 pagesDigital Electronics and Logic Design LabVijulNo ratings yet

- Unit 3 Fuzzy SystemsDocument6 pagesUnit 3 Fuzzy SystemsRegved PandeNo ratings yet

- Chapter 5 Synchronous Sequential CircuitDocument73 pagesChapter 5 Synchronous Sequential CircuitBirukNo ratings yet

- 5 Java Data TypesDocument5 pages5 Java Data TypesPrerna GourNo ratings yet

- 5 Fuzzy LogicDocument8 pages5 Fuzzy LogicAmmar AlkindyNo ratings yet

- DefuzzificationDocument55 pagesDefuzzificationAatmaj SalunkeNo ratings yet

- Java Variables and Data Types With EXAMPLEDocument8 pagesJava Variables and Data Types With EXAMPLEyiheyis alemuNo ratings yet

- Chapter 1: Digital Design ReviewDocument26 pagesChapter 1: Digital Design ReviewVinh ĐứcNo ratings yet

- Lab Report 2Document10 pagesLab Report 2Bappy HossenNo ratings yet

- Digital Techniques VIVA ANSWERS 3rd SEMDocument6 pagesDigital Techniques VIVA ANSWERS 3rd SEMOSA MEMBERNo ratings yet

- Solution - Ass #2-ch 2 - s2016Document3 pagesSolution - Ass #2-ch 2 - s2016Abigail EngleNo ratings yet

- Discrete Structures For Computer Science (DSCS) : BITS PilaniDocument41 pagesDiscrete Structures For Computer Science (DSCS) : BITS PilaniYuva Teja AdariNo ratings yet

- Lab Report: Submitted ToDocument12 pagesLab Report: Submitted ToMd. Al Amin 201-15-3479100% (1)

- 2021 Lecture08 FirstOrderLogic PDFDocument97 pages2021 Lecture08 FirstOrderLogic PDFMinh ChâuNo ratings yet

- Karnaugh Maps K Map CompressDocument17 pagesKarnaugh Maps K Map CompressKevin PurbaNo ratings yet

- Programming II (Object Oriented Programming) : Dr. Nader MahmoudDocument49 pagesProgramming II (Object Oriented Programming) : Dr. Nader MahmoudShehab magdyNo ratings yet

- DLC SyllabusDocument1 pageDLC SyllabusPandyselvi BalasubramanianNo ratings yet