Professional Documents

Culture Documents

Fdb86363 - F085: N-Channel Powertrench Mosfet

Uploaded by

Nobreak ServiceOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Fdb86363 - F085: N-Channel Powertrench Mosfet

Uploaded by

Nobreak ServiceCopyright:

Available Formats

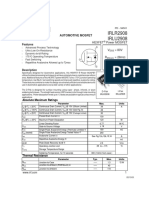

FDB86363_F085 N-Channel PowerTrench® MOSFET

June 2014

FDB86363_F085

N-Channel PowerTrench® MOSFET

D D

80 V, 110 A, 2.4 mΩ

Features

Typical RDS(on) = 2.0 mΩ at VGS = 10V, ID = 80 A

Typical Qg(tot) = 131 nC at VGS = 10V, ID = 80 A G

UIS Capability G S

RoHS Compliant TO-263 S

Qualified to AEC Q101 FDB SERIES

Applications

For current package drawing, please refer to the Fairchild

Automotive Engine Control website at www.fairchildsemi.com/packaging

PowerTrain Management

Solenoid and Motor Drivers

Integrated Starter/Alternator

Primary Switch for 12V Systems

MOSFET Maximum Ratings TJ = 25°C unless otherwise noted.

Symbol Parameter Ratings Units

VDSS Drain-to-Source Voltage 80 V

VGS Gate-to-Source Voltage ±20 V

Drain Current - Continuous (VGS=10) (Note 1) TC = 25°C 110

ID A

Pulsed Drain Current TC = 25°C See Figure 4

EAS Single Pulse Avalanche Energy (Note 2) 512 mJ

Power Dissipation 300 W

PD

Derate Above 25oC 2.0 W/oC

oC

TJ, TSTG Operating and Storage Temperature -55 to + 175

oC/W

RθJC Thermal Resistance, Junction to Case 0.5

oC/W

RθJA Maximum Thermal Resistance, Junction to Ambient (Note 3) 43

Notes:

1: Current is limited by bondwire configuration.

2: Starting TJ = 25°C, L = 0.25mH, IAS = 64A, VDD = 80V during inductor charging and VDD = 0V during time in avalanche.

3: RθJA is the sum of the junction-to-case and case-to-ambient thermal resistance, where the case thermal reference is defined as the solder

mounting surface of the drain pins. RθJC is guaranteed by design, while RθJAis determined by the board design. The maximum rating

presented here is based on mounting on a 1 in2 pad of 2oz copper.

Package Marking and Ordering Information

Device Marking Device Package Reel Size Tape Width Quantity

FDB86363 FDB86363_F085 D2-PAK(TO-263) 330mm 24mm 800 units

©2014 Fairchild Semiconductor Corporation 1 www.fairchildsemi.com

FDB86363_F085 Rev. C2

FDB86363_F085 N-Channel PowerTrench® MOSFET

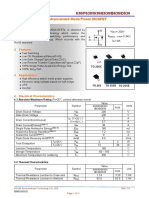

Electrical Characteristics TJ = 25°C unless otherwise noted.

Symbol Parameter Test Conditions Min. Typ. Max. Units

Off Characteristics

BVDSS Drain-to-Source Breakdown Voltage ID = 250μA, VGS = 0V 80 - - V

VDS = 80V, TJ = 25oC - - 1 μA

IDSS Drain-to-Source Leakage Current

VGS = 0V TJ = 175oC (Note 4) - - 1 mA

IGSS Gate-to-Source Leakage Current VGS = ±20V - - ±100 nA

On Characteristics

VGS(th) Gate to Source Threshold Voltage VGS = VDS, ID = 250μA 2.0 3.0 4.0 V

ID = 80A, TJ = 25oC - 2.0 2.4 mΩ

RDS(on) Drain to Source On Resistance

VGS= 10V TJ = 175oC (Note 4) - 3.8 4.3 mΩ

Dynamic Characteristics

Ciss Input Capacitance - 10000 - pF

VDS = 40V, VGS = 0V,

Coss Output Capacitance - 1400 - pF

f = 1MHz

Crss Reverse Transfer Capacitance - 95 - pF

Rg Gate Resistance f = 1MHz - 3.3 - Ω

Qg(ToT) Total Gate Charge at 10V VGS = 0 to 10V VDD = 64V - 131 150 nC

Qg(th) Threshold Gate Charge VGS = 0 to 2V ID = 80A - 18 21 nC

Qgs Gate-to-Source Gate Charge - 47 - nC

Qgd Gate-to-Drain “Miller“ Charge - 24 - nC

Switching Characteristics

ton Turn-On Time - - 231 ns

td(on) Turn-On Delay - 38 - ns

tr Rise Time VDD = 40V, ID = 80A, - 129 - ns

td(off) Turn-Off Delay VGS = 10V, RGEN = 6Ω - 64 - ns

tf Fall Time - 40 - ns

toff Turn-Off Time - - 135 ns

Drain-Source Diode Characteristics

ISD =80A, VGS = 0V - - 1.25 V

VSD Source-to-Drain Diode Voltage

ISD = 40A, VGS = 0V - - 1.2 V

trr Reverse-Recovery Time IF = 80A, dISD/dt = 100A/μs, - 88 101 ns

Qrr Reverse-Recovery Charge VDD=64V - 129 157 nC

Note:

4: The maximum value is specified by design at TJ = 175°C. Product is not tested to this condition in production.

FDB86363_F085 Rev. C2 2 www.fairchildsemi.com

FDB86363_F085 N-Channel PowerTrench® MOSFET

Typical Characteristics

1.2 300

POWER DISSIPATION MULTIPLIER

CURRENT LIMITED VGS = 10V

1.0 250 BY PACKAGE

ID, DRAIN CURRENT (A)

CURRENT LIMITED

BY SILICON

0.8 200

0.6 150

0.4 100

0.2 50

0.0 0

0 25 50 75 100 125 150 175 25 50 75 100 125 150 175 200

TC, CASE TEMPERATURE(oC) TC, CASE TEMPERATURE(oC)

Figure 1. Normalized Power Dissipation vs. Case Figure 2. Maximum Continuous Drain Current vs.

Temperature Case Temperature

2

DUTY CYCLE - DESCENDING ORDER

1

NORMALIZED THERMAL

D = 0.50

IMPEDANCE, ZθJC

0.20

0.10 PDM

0.05

0.02

0.1 0.01 t1

t2

NOTES:

DUTY FACTOR: D = t1/t2

SINGLE PULSE PEAK TJ = PDM x ZθJA x RθJA + TC

0.01

-5 -4 -3 -2 -1 0 1

10 10 10 10 10 10 10

t, RECTANGULAR PULSE DURATION(s)

Figure 3. Normalized Maximum Transient Thermal Impedance

10000

VGS = 10V

1000

IDM, PEAK CURRENT (A)

100

TC = 25oC

FOR TEMPERATURES

ABOVE 25oC DERATE PEAK

10 CURRENT AS FOLLOWS:

I = I2 175 - TC

150

SINGLE PULSE

1

-5 -4 -3 -2 -1 0 1

10 10 10 10 10 10 10

t, RECTANGULAR PULSE DURATION(s)

Figure 4. Peak Current Capability

FDB86363_F085 Rev. C2 3 www.fairchildsemi.com

FDB86363_F085 N-Channel PowerTrench® MOSFET

Typical Characteristics

2000 1000

If R = 0

1000 tAV = (L)(IAS)/(1.3*RATED BVDSS - VDD)

IAS, AVALANCHE CURRENT (A)

If R ≠ 0

ID, DRAIN CURRENT (A)

tAV = (L/R)ln[(IAS*R)/(1.3*RATED BVDSS - VDD) +1]

100 100

100us STARTING TJ = 25oC

10

OPERATION IN THIS

AREA MAY BE 10

LIMITED BY rDS(on) 1ms

1 STARTING TJ = 150oC

SINGLE PULSE 10ms

TJ = MAX RATED

100ms

TC = 25oC

0.1 1

0.001 0.01 0.1 1 10 100 1000

1 10 100 200 tAV, TIME IN AVALANCHE (ms)

VDS, DRAIN TO SOURCE VOLTAGE (V)

NOTE: Refer to Fairchild Application Notes AN7514 and AN7515

Figure 5. Forward Bias Safe Operating Area Figure 6. Unclamped Inductive Switching

Capability

300 300

PULSE DURATION = 80μs

IS, REVERSE DRAIN CURRENT (A)

DUTY CYCLE = 0.5% MAX 100 VGS = 0 V

250

VDD = 5V

ID, DRAIN CURRENT (A)

200 10

TJ = 175 oC

TJ = 175oC TJ = 25 oC

150

TJ = 25oC 1

100

TJ = -55oC

0.1

50

0 0.01

2 3 4 5 6 7 0.0 0.2 0.4 0.6 0.8 1.0 1.2

VGS, GATE TO SOURCE VOLTAGE (V) VSD, BODY DIODE FORWARD VOLTAGE (V)

Figure 7. Transfer Characteristics Figure 8. Forward Diode Characteristics

300 300

250

ID, DRAIN CURRENT (A)

ID, DRAIN CURRENT (A)

VGS 250 VGS

15V Top 15V Top

10V 10V

200 8V 200 8V 5.5V

7V 7V

6V 6V

150 5.5V 150 5V 5.5V

5V Bottom 5V Bottom

100 100

5V

50 80μs PULSE WIDTH 50 80μs PULSE WIDTH

Tj=25oC Tj=175oC

0 0

0 1 2 3 4 5 0 1 2 3 4 5

VDS, DRAIN TO SOURCE VOLTAGE (V) VDS, DRAIN TO SOURCE VOLTAGE (V)

Figure 9. Saturation Characteristics Figure 10. Saturation Characteristics

FDB86363_F085 Rev. C2 4 www.fairchildsemi.com

FDB86363_F085 N-Channel PowerTrench® MOSFET

Typical Characteristics

30 2.0

DRAIN TO SOURCE ON-RESISTANCE

ID = 80A PULSE DURATION = 80μs PULSE DURATION = 80μs

DUTY CYCLE = 0.5% MAX DUTY CYCLE = 0.5% MAX

rDS(on), DRAIN TO SOURCE

25

ON-RESISTANCE (mΩ)

1.6

20

NORMALIZED

TJ = 175oC TJ = 25oC

15 1.2

10

0.8

ID = 80A

5

VGS = 10V

0 0.4

2 4 6 8 10 -80 -40 0 40 80 120 160 200

VGS, GATE TO SOURCE VOLTAGE (V) TJ, JUNCTION TEMPERATURE(oC)

Figure 11. RDSON vs. Gate Voltage Figure 12. Normalized RDSON vs. Junction

Temperature

1.5 1.10

VGS = VDS ID = 5mA

NORMALIZED DRAIN TO SOURCE

ID = 250μA

1.2

THRESHOLD VOLTAGE

BREAKDOWN VOLTAGE

1.05

NORMALIZED GATE

0.9

1.00

0.6

0.95

0.3

0.0 0.90

-80 -40 0 40 80 120 160 200 -80 -40 0 40 80 120 160 200

TJ, JUNCTION TEMPERATURE(oC) TJ, JUNCTION TEMPERATURE (oC)

Figure 13. Normalized Gate Threshold Voltage vs. Figure 14. Normalized Drain to Source

Temperature Breakdown Voltage vs. Junction Temperature

100000 10

VGS, GATE TO SOURCE VOLTAGE(V)

ID = 80A

VDD = 32V

Ciss

CAPACITANCE (pF)

8

10000

VDD = 40V VDD = 48V

Coss 6

1000

4

100 Crss

2

f = 1MHz

VGS = 0V

10 0

0.1 1 10 100 0 30 60 90 120 150

VDS, DRAIN TO SOURCE VOLTAGE (V) Qg, GATE CHARGE(nC)

Figure 15. Capacitance vs. Drain to Source Figure 16. Gate Charge vs. Gate to Source

Voltage Voltage

FDB86363_F085 Rev. C2 5 www.fairchildsemi.com

TRADEMARKS

The following includes registered and unregistered trademarks and service marks, owned by Fairchild Semiconductor and/or its global subsidiaries, and is not

intended to be an exhaustive list of all such trademarks.

AccuPower™ F-PFS™ ®*

AX-CAP®* FRFET® ® tm

BitSiC™ Global Power Resource SM PowerTrench ®

TinyBoost®

Build it Now™ GreenBridge™ PowerXS™

TinyBuck®

CorePLUS™ Green FPS™ Programmable Active Droop™

® TinyCalc™

CorePOWER™ Green FPS™ e-Series™ QFET

TinyLogic®

CROSSVOLT™ Gmax™ QS™

TINYOPTO™

CTL™ GTO™ Quiet Series™

TinyPower™

Current Transfer Logic™ IntelliMAX™ RapidConfigure™

TinyPWM™

DEUXPEED® ISOPLANAR™ ™ TinyWire™

Dual Cool™ Marking Small Speakers Sound Louder

TranSiC™

EcoSPARK® and Better™ Saving our world, 1mW/W/kW at a time™

TriFault Detect™

EfficentMax™ MegaBuck™ SignalWise™

TRUECURRENT®*

ESBC™ MICROCOUPLER™ SmartMax™

μSerDes™

® MicroFET™ SMART START™

MicroPak™ Solutions for Your Success™

Fairchild ® MicroPak2™ SPM®

Fairchild Semiconductor ® MillerDrive™ STEALTH™ UHC®

FACT Quiet Series™ MotionMax™ SuperFET® Ultra FRFET™

FACT® mWSaver® SuperSOT™-3 UniFET™

FAST ® OptoHiT™ SuperSOT™-6 VCX™

®

FastvCore™ OPTOLOGIC SuperSOT™-8 VisualMax™

® ®

FETBench™ OPTOPLANAR SupreMOS VoltagePlus™

FPS™ SyncFET™ XS™

Sync-Lock™ 仙童 ™

*Trademarks of System General Corporation, used under license by Fairchild Semiconductor.

DISCLAIMER

FAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE

RELIABILITY, FUNCTION, OR DESIGN. FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY

PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS.

THESE SPECIFICATIONS DO NOT EXPAND THE TERMS OF FAIRCHILD’S WORLDWIDE TERMS AND CONDITIONS, SPECIFICALLY THE WARRANTY

THEREIN, WHICH COVERS THESE PRODUCTS.

LIFE SUPPORT POLICY

FAIRCHILD’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE

EXPRESS WRITTEN APPROVAL OF FAIRCHILD SEMICONDUCTOR CORPORATION.

As used here in:

1. Life support devices or systems are devices or systems which, (a) are 2. A critical component in any component of a life support, device, or

intended for surgical implant into the body or (b) support or sustain life, system whose failure to perform can be reasonably expected to cause

and (c) whose failure to perform when properly used in accordance with the failure of the life support device or system, or to affect its safety or

instructions for use provided in the labeling, can be reasonably effectiveness.

expected to result in a significant injury of the user.

ANTI-COUNTERFEITING POLICY

Fairchild Semiconductor Corporation’s Anti-Counterfeiting Policy. Fairchild’s Anti-Counterfeiting Policy is also stated on our external website,

www.Fairchildsemi.com, under Sales Support.

Counterfeiting of semiconductor parts is a growing problem in the industry. All manufactures of semiconductor products are experiencing counterfeiting of their

parts. Customers who inadvertently purchase counterfeit parts experience many problems such as loss of brand reputation, substandard performance, failed

application, and increased cost of production and manufacturing delays. Fairchild is taking strong measures to protect ourselves and our customers from the

proliferation of counterfeit parts. Fairchild strongly encourages customers to purchase Fairchild parts either directly from Fairchild or from Authorized Fairchild

Distributors who are listed by country on our web page cited above. Products customers buy either from Fairchild directly or from Authorized Fairchild

Distributors are genuine parts, have full traceability, meet Fairchild’s quality standards for handing and storage and provide access to Fairchild’s full range of

up-to-date technical and product information. Fairchild and our Authorized Distributors will stand behind all warranties and will appropriately address and

warranty issues that may arise. Fairchild will not provide any warranty coverage or other assistance for parts bought from Unauthorized Sources. Fairchild is

committed to combat this global problem and encourage our customers to do their part in stopping this practice by buying direct or from authorized distributors.

PRODUCT STATUS DEFINITIONS

Definition of Terms

Datasheet Identification Product Status Definition

Datasheet contains the design specifications for product development. Specifications

Advance Information Formative / In Design may change in any manner without notice.

Datasheet contains preliminary data; supplementary data will be published at a later

Preliminary First Production date. Fairchild Semiconductor reserves the right to make changes at any time without

notice to improve design.

Datasheet contains final specifications. Fairchild Semiconductor reserves the right to

No Identification Needed Full Production

make changes at any time without notice to improve the design.

Datasheet contains specifications on a product that is discontinued by Fairchild

Obsolete Not In Production

Semiconductor. The datasheet is for reference information only.

Rev. I68

FDB86363_F085 Rev. C2 6 www.fairchildsemi.com

You might also like

- Fdd9407L - F085: N-Channel Logic Level Powertrench MosfetDocument7 pagesFdd9407L - F085: N-Channel Logic Level Powertrench Mosfetonis1 onis1No ratings yet

- Huf76633S3St - F085: N-Channel Logic Level Ultrafet Power MosfetDocument7 pagesHuf76633S3St - F085: N-Channel Logic Level Ultrafet Power MosfetJose cuelloNo ratings yet

- FDP8443Document7 pagesFDP8443Semut criminalsNo ratings yet

- Truesemi-TSD5N65M C382376Document10 pagesTruesemi-TSD5N65M C382376carlos riveraNo ratings yet

- 100N10 EtcDocument5 pages100N10 EtcJm TechNo ratings yet

- N-Channel Low QG Mosfet 30V, 100A, 3.3m: MOS-TECH Semiconductor Co.,LTDDocument9 pagesN-Channel Low QG Mosfet 30V, 100A, 3.3m: MOS-TECH Semiconductor Co.,LTDAnonymous p1ig0zX6p0No ratings yet

- Fdb2532 - F085: N-Channel Powertrench Mosfet 150V, 79A, 16MDocument11 pagesFdb2532 - F085: N-Channel Powertrench Mosfet 150V, 79A, 16MSukandar TeaNo ratings yet

- Irf 634 BDocument8 pagesIrf 634 BAhmed ShagidullinNo ratings yet

- B 812 Cfa 38Document8 pagesB 812 Cfa 38Sajid AliNo ratings yet

- RTW90N20D/RTA90N20D 200V N-Channel MOSFET: Features General DescriptionDocument10 pagesRTW90N20D/RTA90N20D 200V N-Channel MOSFET: Features General DescriptionRaghunandan SubramanianNo ratings yet

- Fdp038An06A0 / Fdi038An06A0: N-Channel Powertrench MosfetDocument12 pagesFdp038An06A0 / Fdi038An06A0: N-Channel Powertrench Mosfetdani pedroNo ratings yet

- Stp40Nf10L: N-Channel 100V - 0.028 - 40A To-220 Low Gate Charge Stripfet™ Power MosfetDocument12 pagesStp40Nf10L: N-Channel 100V - 0.028 - 40A To-220 Low Gate Charge Stripfet™ Power MosfetKhairi SaidNo ratings yet

- Fds8880 N-Channel Powertrench: MosfetDocument12 pagesFds8880 N-Channel Powertrench: MosfetDavid J. Pinto ApazaNo ratings yet

- Unisonic Technologies Co., LTD: 15A, 700V N-CHANNEL Power MosfetDocument6 pagesUnisonic Technologies Co., LTD: 15A, 700V N-CHANNEL Power MosfetDavid alejandro VergaraNo ratings yet

- Features 10N65 650V N-Channel MOSFET: TO-220F PackageDocument7 pagesFeatures 10N65 650V N-Channel MOSFET: TO-220F PackageMindSet MarcosNo ratings yet

- 20N50EDocument8 pages20N50EFernando SimãoNo ratings yet

- NCE8295A: Enhancement Mode Power MOSFETDocument7 pagesNCE8295A: Enhancement Mode Power MOSFETDarknezzNo ratings yet

- 8 N 80Document5 pages8 N 80pravin jadavNo ratings yet

- Data SheetDocument12 pagesData SheetGigih AtmajaNo ratings yet

- Unisonic Technologies Co., LTD: 10A, 650V N-CHANNEL Power MosfetDocument6 pagesUnisonic Technologies Co., LTD: 10A, 650V N-CHANNEL Power MosfetJhonson Shut DownNo ratings yet

- Unisonic Technologies Co., LTD: 5.5A, 400V, 1.0 OHM, N-Channel Power MosfetDocument6 pagesUnisonic Technologies Co., LTD: 5.5A, 400V, 1.0 OHM, N-Channel Power MosfetCahemlNo ratings yet

- FKD3004 FETekDocument4 pagesFKD3004 FETekpapainoelmorreuNo ratings yet

- P YYBAGGlzi CAGQg IABd EWcg 9 MW I206Document7 pagesP YYBAGGlzi CAGQg IABd EWcg 9 MW I206intemenmenNo ratings yet

- Irhlf77214 250V Radhard N MosfetDocument9 pagesIrhlf77214 250V Radhard N MosfetarsebiscuitsNo ratings yet

- IRFF110 JANTX2N6782 Hexfet Transistors JANTXV2N6782 THRU-HOLE (TO-205AF) REF:MIL-PRF-19500/556 100V, N-CHANNELDocument7 pagesIRFF110 JANTX2N6782 Hexfet Transistors JANTXV2N6782 THRU-HOLE (TO-205AF) REF:MIL-PRF-19500/556 100V, N-CHANNELJerson SebastianNo ratings yet

- Unisonic Technologies Co., LTD: 15A, 300V N-CHANNEL Power MosfetDocument6 pagesUnisonic Technologies Co., LTD: 15A, 300V N-CHANNEL Power MosfetaboaltaemrrNo ratings yet

- AOT8N50/AOTF8N50: General Description Product SummaryDocument6 pagesAOT8N50/AOTF8N50: General Description Product Summaryalmia tronicsNo ratings yet

- UF3C065040K3S Data SheetDocument11 pagesUF3C065040K3S Data Sheetsultaniwahid240No ratings yet

- ssp7n60b sss7n60b PDFDocument11 pagesssp7n60b sss7n60b PDFNerio FerrerNo ratings yet

- IRLR2908 IRLU2908: Automotive MosfetDocument11 pagesIRLR2908 IRLU2908: Automotive MosfetAnhVũNo ratings yet

- Stp80Pf55: P-Channel 55V - 0.016 - 80A To-220 Stripfet Ii Power MosfetDocument7 pagesStp80Pf55: P-Channel 55V - 0.016 - 80A To-220 Stripfet Ii Power MosfetRadoslav RadoslavovNo ratings yet

- IRF820Document8 pagesIRF820ЫманалыNo ratings yet

- Irf840 PDFDocument8 pagesIrf840 PDFAnonymous AssOOhqigNo ratings yet

- IRF840Document8 pagesIRF840Apc CamNo ratings yet

- 600V 10A N-Channel MOSFETDocument7 pages600V 10A N-Channel MOSFETVuksanov ZarkoNo ratings yet

- Datasheet PDFDocument10 pagesDatasheet PDFShikamaru MendozaNo ratings yet

- 100V N-Channel Mosfets: General DescriptionDocument5 pages100V N-Channel Mosfets: General DescriptionMariusNo ratings yet

- Enhancement Mode Power MOSFET: NCE N-ChannelDocument7 pagesEnhancement Mode Power MOSFET: NCE N-ChannelErroz RosadiNo ratings yet

- Unisonic Technologies Co., LTD: 800V N-Channel Power MosfetDocument6 pagesUnisonic Technologies Co., LTD: 800V N-Channel Power MosfetEisenhower Garcia LealNo ratings yet

- AOT8N80L/AOTF8N80: General Description Product SummaryDocument6 pagesAOT8N80L/AOTF8N80: General Description Product SummaryCristobalzqNo ratings yet

- NVHL025N065SC1 D-3326403Document9 pagesNVHL025N065SC1 D-3326403Andrey VulfovichNo ratings yet

- TSF65R300S1 TruesemiDocument9 pagesTSF65R300S1 Truesemimisael1001No ratings yet

- Irfr3505Pbf Irfu3505Pbf: FeaturesDocument11 pagesIrfr3505Pbf Irfu3505Pbf: FeaturesAzizullah AlizayNo ratings yet

- MTP3055V Power MOSFET 12 Amps, 60 Volts: N Channel TO 220Document7 pagesMTP3055V Power MOSFET 12 Amps, 60 Volts: N Channel TO 220Hectór DavidNo ratings yet

- N-Channel Enhancement-Mode Silicon Gate: Semiconductor Technical DataDocument8 pagesN-Channel Enhancement-Mode Silicon Gate: Semiconductor Technical DataErroz RosadiNo ratings yet

- Uufggf 5 UDocument7 pagesUufggf 5 UYousef KassimNo ratings yet

- SSP7N60B/SSS7N60B: 600V N-Channel MOSFETDocument12 pagesSSP7N60B/SSS7N60B: 600V N-Channel MOSFETValdenor CostaNo ratings yet

- IRLR2905Z IRLU2905Z: Automotive MosfetDocument11 pagesIRLR2905Z IRLU2905Z: Automotive MosfetnaughtybigboyNo ratings yet

- Irliz34Npbf: V 55V R 0.035 I 22ADocument9 pagesIrliz34Npbf: V 55V R 0.035 I 22Ayu liuNo ratings yet

- Hyg042n10ns1p Hyg042n10ns1bDocument10 pagesHyg042n10ns1p Hyg042n10ns1brennybenitezNo ratings yet

- TPC8064-H: DescriptionDocument5 pagesTPC8064-H: DescriptionBari ShobariNo ratings yet

- STP40NF10 STB40NF10 - STB40NF10-1Document12 pagesSTP40NF10 STB40NF10 - STB40NF10-1Anca SterianNo ratings yet

- Nce 8295 AkDocument7 pagesNce 8295 Akandre kressnerNo ratings yet

- Mosfet S A0002809502 1Document8 pagesMosfet S A0002809502 1Ree-anne SabanalNo ratings yet

- A03400ADocument5 pagesA03400AxigorkordNo ratings yet

- Irfl4105Pbf: V 55V R 0.045 I 3.7A DescriptionDocument10 pagesIrfl4105Pbf: V 55V R 0.045 I 3.7A DescriptionPool Vila AdautoNo ratings yet

- PD - 90330F: "IRF450 HEXFET Transistor DatasheetDocument7 pagesPD - 90330F: "IRF450 HEXFET Transistor DatasheetAnonymous BanTcoNo ratings yet

- Datasheet F630Document11 pagesDatasheet F630Lâm Bá NhãNo ratings yet

- NCE0218 Pb Free 18A 200V N-Channel Power MOSFETDocument7 pagesNCE0218 Pb Free 18A 200V N-Channel Power MOSFETRichard MachadoNo ratings yet

- Semiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsFrom EverandSemiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsNo ratings yet

- Manual de Serviço AOC 212vaDocument60 pagesManual de Serviço AOC 212vaNobreak ServiceNo ratings yet

- CM-336/337 Color Video Monitor Service ManualDocument53 pagesCM-336/337 Color Video Monitor Service ManualNobreak ServiceNo ratings yet

- 187 sdl3300-10000Document31 pages187 sdl3300-10000Nobreak ServiceNo ratings yet

- Master Hp-Ul: User ManualDocument83 pagesMaster Hp-Ul: User Manualperformer 237No ratings yet

- Technical Data: On-Line UPS-systemDocument9 pagesTechnical Data: On-Line UPS-systempaivinha21No ratings yet

- Teaching The Internet of Things Iot Using Universally Available Raspberry Pi and Arduino PlatformsDocument11 pagesTeaching The Internet of Things Iot Using Universally Available Raspberry Pi and Arduino PlatformsVictoriaNo ratings yet

- Partner Competency - E Pumps & SolutionDocument57 pagesPartner Competency - E Pumps & SolutionAhmed KotbNo ratings yet

- ESG V3 SyllabusDocument12 pagesESG V3 SyllabusAaronNo ratings yet

- GL Poseidon User ManualDocument256 pagesGL Poseidon User ManualIrina MaltopolNo ratings yet

- Method Statement For Fuel System (Diesel Supply System For Generator)Document16 pagesMethod Statement For Fuel System (Diesel Supply System For Generator)BAVA M.H100% (1)

- Ficha Tecnica SpikaDocument2 pagesFicha Tecnica SpikaJosé Luis RubioNo ratings yet

- BD645, BD647, BD649, BD651 NPN Silicon Power DarlingtonsDocument4 pagesBD645, BD647, BD649, BD651 NPN Silicon Power DarlingtonsErasmo Franco SNo ratings yet

- MCE 244 Course OutlineDocument1 pageMCE 244 Course OutlineKaren DavisNo ratings yet

- 2010 IMCO CatalogDocument170 pages2010 IMCO Cataloggeav25653855No ratings yet

- My ResumeDocument2 pagesMy ResumeSathanandhNo ratings yet

- Sample Securitiser: Pressure Facility Re-InventedDocument4 pagesSample Securitiser: Pressure Facility Re-InventedMiguelNo ratings yet

- MINI R56 N12 Valve Stem Seal ReplacementDocument9 pagesMINI R56 N12 Valve Stem Seal ReplacementJohn DoeNo ratings yet

- Experiment No. 2 Introduction To Combinational Circuits: Group Name: Group 7 Group Leader: JOSE DOROSAN Group MemberDocument11 pagesExperiment No. 2 Introduction To Combinational Circuits: Group Name: Group 7 Group Leader: JOSE DOROSAN Group MemberJoy PeconcilloNo ratings yet

- Statement of QualificationsDocument1 pageStatement of Qualificationsrf12345No ratings yet

- Eng Solutions RCBDocument8 pagesEng Solutions RCBgalo1005No ratings yet

- 17fin8593 C Us NCR Selfserv 26 DsDocument2 pages17fin8593 C Us NCR Selfserv 26 DsJose MarcosNo ratings yet

- HERRAMIENTA DE LLENADO - AutoFill PDFDocument15 pagesHERRAMIENTA DE LLENADO - AutoFill PDFluis alberto franco rodriguezNo ratings yet

- Pakistan Exams Cie o A Reg Form Oct09Document13 pagesPakistan Exams Cie o A Reg Form Oct09shamsulzamanNo ratings yet

- Hydraulic ConductivityDocument8 pagesHydraulic ConductivityJill AndersonNo ratings yet

- D/S Dokmoka LoringthepiDocument1 pageD/S Dokmoka LoringthepiManupriya KapleshNo ratings yet

- Tailor Welded BlanksDocument52 pagesTailor Welded BlanksYuvaraj YuvarajNo ratings yet

- Full Download Law and Ethics For The Health Professions 6th Edition Judson Harrison Test Bank PDF Full ChapterDocument20 pagesFull Download Law and Ethics For The Health Professions 6th Edition Judson Harrison Test Bank PDF Full Chapterhorriblebaculite0ly6t100% (14)

- Error Correction ModelDocument37 pagesError Correction ModelRollins JohnNo ratings yet

- CropWat 4 Windows calculates crop water requirementsDocument2 pagesCropWat 4 Windows calculates crop water requirementsadam_pengeranNo ratings yet

- STS Assignment1Document3 pagesSTS Assignment1Cagabcab Canibel Melany0% (1)

- Humour and IdentityDocument12 pagesHumour and IdentityLyann MartinezNo ratings yet

- Road of The Beast Combo DisciplinsDocument2 pagesRoad of The Beast Combo DisciplinsMiha DuhNo ratings yet

- Chapter 3 PPTDocument41 pagesChapter 3 PPTidNo ratings yet

- The 5 Stages of the Design ProcessDocument5 pagesThe 5 Stages of the Design ProcessDacia BarrettNo ratings yet