0% found this document useful (0 votes)

191 views30 pagesDigital Circuit Design Basics

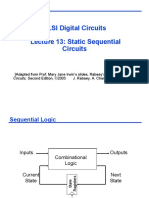

This document discusses static sequential circuits and timing metrics. It describes how sequential logic uses registers to store the current state and how that state is used to determine the next state. The timing constraints for sequential logic are discussed, including setup time, propagation delay, and hold time. The document contrasts static and dynamic storage and describes latches and flip-flops. Positive and negative edge-triggered latches and master-slave flip-flops are explained.

Uploaded by

SHOBHIT SHARMACopyright

© © All Rights Reserved

We take content rights seriously. If you suspect this is your content, claim it here.

Available Formats

Download as PPT, PDF, TXT or read online on Scribd

0% found this document useful (0 votes)

191 views30 pagesDigital Circuit Design Basics

This document discusses static sequential circuits and timing metrics. It describes how sequential logic uses registers to store the current state and how that state is used to determine the next state. The timing constraints for sequential logic are discussed, including setup time, propagation delay, and hold time. The document contrasts static and dynamic storage and describes latches and flip-flops. Positive and negative edge-triggered latches and master-slave flip-flops are explained.

Uploaded by

SHOBHIT SHARMACopyright

© © All Rights Reserved

We take content rights seriously. If you suspect this is your content, claim it here.

Available Formats

Download as PPT, PDF, TXT or read online on Scribd