Professional Documents

Culture Documents

Trilithic Data Sheet Bts 781 GP: 1 1.1 Features

Uploaded by

Виктор СабовOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Trilithic Data Sheet Bts 781 GP: 1 1.1 Features

Uploaded by

Виктор СабовCopyright:

Available Formats

TrilithIC BTS 781 GP

Data Sheet

1 Overview

1.1 Features

• Quad D-MOS switch

• Free configurable as bridge or quad-switch

• Optimized for DC motor management applications

• Low RDS ON: 26 mΩ high-side switch, 14 mΩ low-side

switch (typical values @ 25 °C) P-TO263-15-1

• Maximum peak current: typ. 42 A @ 25 °C=

• Very low quiescent current: typ. 4 µA @ 25 °C=

• Small outline, thermal optimized PowerPak

• Load and GND-short-circuit-protection

• Operates up to 40 V

• Status flag for over temperature

• Open load detection in Off-mode

• Overtemperature shut down with hysteresis

• Internal clamp diodes

• Isolated sources for external current sensing

• Under-voltage detection with hysteresis

Type Ordering Code Package

BTS 781 GP Q67006-A9526 P-TO263-15-1

1.2 Description

The BTS 781 GP is part of the TrilithIC family containing three dies in one package:

One double high-side switch and two low-side switches. The drains of these three

vertical DMOS chips are mounted on separated leadframes. The sources are connected

to individual pins, so the BTS 781 GP can be used in H-bridge- as well as in any other

configuration. The double high-side is manufactured in SMART SIPMOS® technology

which combines low RDS ON vertical DMOS power stages with CMOS control circuit. The

high-side switch is fully protected and contains the control and diagnosis circuit. To

achieve low RDS ON and fast switching performance, the low-side switches are

manufactured in S-FET 2 logic level technology. The equivalent standard product is the

SPD30N06S2L-13.

Data Sheet 1 2002-06-28

BTS 781 GP

1.3 Pin Configuration

(top view)

Molding

Compound

NC 1

Heat-Slug 1

SL1 2

18 DL1

IL1 3

NC 4

IH1 5

Heat-Slug 2

ST1 6

SH1 7

DHVS 8 17 DHVS

GND 9

IH2 10

ST2 11

SH2 12

Heat-Slug 3

SL2 13

16 DL2

NC 14

IL2 15

Figure 1

Data Sheet 2 2002-06-28

BTS 781 GP

1.4 Pin Definitions and Functions

Pin No. Symbol Function

1 NC Not connected

2 SL1 Source of low-side switch 1

3 IL1 Analog input of low-side switch 1

4 NC Not connected

5 IH1 Digital input of high-side switch 1

6 ST1 Status of high-side switch 1; open Drain output

7 SH1 Source of high-side switch 1

8 DHVS Drain of high-side switches and power supply voltage

9 GND Ground of high-side switches

10 IH2 Digital input of high-side switch 2

11 ST2 Status of high-side switch 2; open Drain output

12 SH2 Source of high-side switch 2

13 SL2 Source of low-side switch 2

14 NC Not connected

15 IL2 Analog input of low-side switch 2

16 DL2 Drain of low-side switch 2

Heat-Slug 3

17 DHVS Drain of high-side switches and power supply voltage

Heat-Slug 2

18 DL1 Drain of low-side switch 1

Heat-Slug 1

Pins written in bold type need power wiring.

Data Sheet 3 2002-06-28

BTS 781 GP

1.5 Functional Block Diagram

DHVS

6

8, 17

ST1

11 Diagnosis Biasing and Protection

ST2

5

IH1 Driver

IN OUT

0 0 L L

0 1 L H RO1 RO2 12

10

1 0 H L SH2

IH2 1 1 H H

16

DL2

9

GND

7

SH1

18

DL1

3

IL1

15

IL2

2 13

SL1 SL2

Figure 2

Block Diagram

Data Sheet 4 2002-06-28

BTS 781 GP

1.6 Circuit Description

Input Circuit

The control inputs IH1,2 consist of TTL/CMOS compatible Schmitt-Triggers with

hysteresis. Buffer amplifiers are driven by these stages and convert the logic signal into

the necessary form for driving the power output stages. The inputs are protected by ESD

clamp-diodes.

The inputs IL1 and IL2 are connected to the gates of the standard N-channel vertical

power-MOS-FETs.

Output Stages

The output stages consist of a low RDS ON Power-MOS H-bridge. In H-bridge

configuration, the D-MOS body diodes can be used for freewheeling when commutating

inductive loads. If the high-side switches are used as single switches, positive and

negative voltage spikes which occur when driving inductive loads are limited by

integrated power clamp diodes.

Short Circuit Protection

The outputs are protected against

– output short circuit to ground

– overload (load short circuit).

An internal OP-amp controls the Drain-Source-voltage by comparing the DS-voltage-

drop with an internal reference voltage. Above this trippoint the OP-Amp reduces the

output current depending on the junction temperature and the drop voltage.

In the case of overloaded high-side switches the status output is set to low.

Overtemperature Protection

The high-side switches incorporate an overtemperature protection circuit with hysteresis

which switches off the output transistors and sets the status output to low.

Undervoltage-Lockout (UVLO)

When VS reaches the switch-on voltage VUVON the IC becomes active with a hysteresis.

The high-side output transistors are switched off if the supply voltage VS drops below the

switch off value VUVOFF.

Open Load Detection

Open load is detected by voltage measurement in off state. If the output voltage exceeds

a specified level the error flag is set with a delay.

Data Sheet 5 2002-06-28

BTS 781 GP

Status Flag

The two status flag outputs are an open drain output with Zener-diode which require a

pull-up resistor, c.f. the application circuit on page 15. ST1 and ST2 provide separate

diagnosis for each high-side switch. Various errors as listed in the table “Diagnosis” are

detected by switching the open drain output ST1/2 to low. Forward current in the

integrated body diode of the highside switch may cause undefined voltage levels at the

corresponding status output. The open load detection can be used to detect a short to

Vs as long as both lowside switches are off and ROL is disconnected from 5V by

BCR192W.

2 Truthtable and Diagnosis (valid only for the High-Side-Switches)

Flag IH1 IH2 SH1 SH2 ST1 ST2 Remarks

Inputs Outputs

0 0 L L 1 1 stand-by mode

Normal operation; 0 1 L H 1 1 switch2 active

identical with functional truth table 1 0 H L 1 1 switch1 active

1 1 H H 1 1 both switches

active

Open load at high-side switch 1 0 X Z X 0 1 detected

1 X H X 1 1

Open load at high-side switch 2 X 0 X Z 1 0 detected

X 1 X H 1 1

Overtemperature high-side switch1 0 X L X 1 1

1 X L X 0 1 detected

Overtemperature high-side switch2 X 0 X L 1 1

X 1 X L 1 0 detected

Overtemperature both high-side 0 0 L L 1 1

switches X 1 L L 1 0 detected

1 X L L 0 1 detected

Undervoltage X X L L 1 1 not detected

Note: * multiple simultaneous errors are not shown in this table

Inputs: Outputs: Status:

0 = Logic LOW Z = Output in tristate condition 1 = No error

1 = Logic HIGH L = Output in sink condition 0 = Error

X = don’t care H = Output in source condition

X = Voltage level undefined

Data Sheet 6 2002-06-28

BTS 781 GP

3 Electrical Characteristics

3.1 Absolute Maximum Ratings

– 40 °C < Tj < 150 °C

Parameter Symbol Limit Values Unit Remarks

min. max.

High-Side-Switches (Pins DHVS, IH1,2 and SH1,2)

Supply voltage VS – 0.3 42 V –

Supply voltage for full short VS(SCP) 28 V –

circuit protection

HS-drain current IS – 10 * A TC = 125°C; DC

HS-input current IIH –5 5 mA Pin IH1 and IH2

HS-input voltage VIH – 10 16 V Pin IH1 and IH2

Note: * internally limited

Status Output ST (Pins ST1 and ST2)

Status pull up voltage VST – 0.3 5.4 V –

Status Output current IST –5 5 mA Pin ST1 or ST2

Low-Side-Switches (Pins DL1,2, IL1,2 and SL1,2)

Drain- source break down VDSL 55 – V VIL = 0 V; ID ≤ 1 mA

voltage

LS-drain current IDL –20 20 A TC = 125°C; DC

LS-drain current IDL – 25 A tp < 100 ms; ν < 0.1

TC = 85°C – 100 A tp < 1 ms; ν < 0.1

LS-input voltage VIL – 20 20 V Pin IL1 and IL2

Temperatures

Junction temperature Tj – 40 150 °C –

Storage temperature Tstg – 55 150 °C –

Data Sheet 7 2002-06-28

BTS 781 GP

3.1 Absolute Maximum Ratings (cont’d)

– 40 °C < Tj < 150 °C

Parameter Symbol Limit Values Unit Remarks

min. max.

Thermal Resistances (one HS-LS-Path active)

LS-junction case RthjC L – 0.6 K/W

HS-junction case RthjC H – 0.75 K/W

Junction ambient Rthja – 35 K/W device soldered to

Rthja = Tj(HS)/(P(HS)+P(LS)) reference PCB with

6 cm2 cooling area

ESD Protection (Human Body Model acc. MIL STD 883D, method 3015.7 and EOS/

ESD assn. standard S5.1 - 1993)

Input LS-Switch VESD 0.5 kV

Input HS-Switch VESD 1 kV

Status HS-Switch VESD 2 kV

Output LS and HS-Switch VESD 4 kV all other pins connected

to Ground

Note: Maximum ratings are absolute ratings; exceeding any one of these values may

cause irreversible damage to the integrated circuit.

3.2 Operating Range

– 40 °C < Tj < 150 °C

Parameter Symbol Limit Values Unit Remarks

min. max.

Supply voltage VS VUVOFF 42 V After VS rising

above VUVON

Input voltages HS VIH – 0.3 15 V –

Input voltages LS VIL – 0.3 20 V –

Status output current IST 0 2 mA –

Junction temperature TjHS – 40 150 °C –

Note: In the operating range the functions given in the circuit description are fulfilled.

Data Sheet 8 2002-06-28

BTS 781 GP

3.3 Electrical Characteristics

ISH1 = ISH2 = ISL1 = ISL2 = 0 A; – 40 °C < Tj < 150 °C; 8 V < VS < 18 V

unless otherwise specified

Parameter Symb Limit Values Unit Test Condition

ol min. typ. max.

Current Consumption HS-switch

Quiescent current IS Q – 4 9 µA IH1 = IH2 = 0 V

Tj = 85 °C

– – 20 µA IH1 = IH2 = 0 V

Supply current IS – 2.5 4.5 mA IH1 or IH2 = 5 V

– 5 9 mA IH1 and IH2 = 5 V

Leakage current of ISH LK – – 7 µA VIH = VSH = 0 V

highside switch Tj = 85 °C

Leakage current through ILKCL = – 2.2 10 mA IFH =5 A

logic GND in free IFH + ISH

wheeling condition

Current Consumption LS-switch

Input current IIL – 10 100 nA VIL = 20 V

VDSL = 0 V

Leakage current of IDL LK – – 12 µA VIL = 0 V

lowside switch VDSL = 40 V

Tj = 85 °C

Under Voltage Lockout (UVLO) HS-switch

Switch-ON voltage VUVON – – 5 V VS increasing

Switch-OFF voltage VUVOFF 1.8 – 4.5 V VS decreasing

Switch ON/OFF VUVHY – 1 – V VUVON – VUVOFF

hysteresis

Data Sheet 9 2002-06-28

BTS 781 GP

3.3 Electrical Characteristics (cont’d)

ISH1 = ISH2 = ISL1 = ISL2 = 0 A; – 40 °C < Tj < 150 °C; 8 V < VS < 18 V

unless otherwise specified

Parameter Symb Limit Values Unit Test Condition

ol min. typ. max.

Output stages

Inverse diode of high- VFH – 0.8 1.2 V IFH = 5 A

side switch; Forward-

voltage

Inverse diode of lowside VFL – 0.8 1.2 V IFL = 5 A

switch; Forward-voltage

Static drain-source RDS ON H – 26 35 mΩ ISH = 5 A

on-resistance of highside Tj = 25 °C

switch

Static drain-source RDS ON L – 14 17 mΩ ISL = 5 A;

on-resistance of lowside VIL = 5 V

switch Tj = 25 °C

Static path on-resistance RDS ON – – 100 mΩ RDS ON H + RDS ON L

ISH = 5 A;

Short Circuit of highside switch to GND

Initial peak SC current ISCP H 35 48 65 A Tj = – 40 °C

Initial peak SC current ISCP H 30 42 54 A Tj = + 25 °C

Initial peak SC current ISCP H 25 32 42 A Tj = + 150 °C

Note: Peak SC current is significantly lower at VS > 18V

Short Circuit of highside switch to VS

Output pull-down-resistor RO 7 14 42 kΩ VDSL = 3 V

Data Sheet 10 2002-06-28

BTS 781 GP

3.3 Electrical Characteristics (cont’d)

ISH1 = ISH2 = ISL1 = ISL2 = 0 A; – 40 °C < Tj < 150 °C; 8 V < VS < 18 V

unless otherwise specified

Parameter Symb Limit Values Unit Test Condition

ol min. typ. max.

Thermal Shutdown

Thermal shutdown Tj SD 155 180 190 °C –

junction temperature

Thermal switch-on Tj SO 150 170 180 °C –

junction temperature

Temperature hysteresis ∆T – 10 – °C ∆T = TjSD – TjSO

Status Flag Output ST of highside switch

Low output voltage VST L – 0.2 0.6 V IST = 1.6 mA

Leakage current IST LK – – 5 µA VST = 5 V

Zener-limit-voltage VST Z 5.4 – V IST = 1.6 mA

Status change after td(SToffo+) – – 20 µs

positive input slope with

open load

Status change after td(SToffo-) – – 700 µs

negative input slope with

open load

Status change after td(STofft+) – 1.6 10 µs RST = 47 kΩ

positive input slope with

overtemperature

Status change after td(STofft-) – 14 100 µs RST = 47 kΩ

negative input slope with

overtemperature

Note: times are guaranteed by design

Open load detection in Off condition

Open load detection VOUT(OL) 2 3 4 V

voltage

Data Sheet 11 2002-06-28

BTS 781 GP

3.3 Electrical Characteristics (cont’d)

ISH1 = ISH2 = ISL1 = ISL2 = 0 A; – 40 °C < Tj < 150 °C; 8 V < VS < 18 V

unless otherwise specified

Parameter Symb Limit Values Unit Test Condition

ol min. typ. max.

Switching times of highside switch

Turn-ON-time; tON – 100 220 µs RLoad = 12 Ω

to 90% VSH VS = 12 V

Turn-OFF-time; tOFF – 120 250 µs RLoad = 12 Ω

to 10% VSH VS = 12 V

Slew rate on 10 to 30% dV/ – 0.5 1.1 V/µs RLoad = 12 Ω

VSH dtON VS = 12 V

Slew rate off 70 to 40% -dV/ – 0.7 1.3 V/µs RLoad = 12 Ω

VSH dtOFF VS = 12 V

Note: switching times are guaranteed by design

Switching times of low-side switch

Turn-ON delay time; td_ON_L – 40 ns resistive load

VIL = 5V; RGate= 16Ω ISL = 10 A; VS = 12 V

Switch-ON time; tON_L – 170 ns resistive load

VIL= 5V; RGate = 16Ω ISL = 10 A; VS = 12 V

Switch-OFF delay time; td_OFF_L – 100 ns resistive load

VIL= 5V; RGate = 16Ω ISL = 10 A; VS = 12 V

Switch-OFF time; tOFF_L – 200 ns resistive load

VIL= 5V; RGate = 16Ω ISL = 10 A; VS = 12 V

Input to source charge; QIS – 4.5 6 nC ISL = 10 A; VS = 40 V

Input to drain charge; QID – 16 24 nC ISL = 10 A; VS = 40 V

Input charge total; QI – 55 69 nC ISL = 10 A; VS = 40 V

VIL = 0 to 10 V

Input plateau voltage; V(plateau) – 2.6 – V ISL = 10 A; VS = 40 V

Note: switching times and input charges are guaranteed by design

Data Sheet 12 2002-06-28

BTS 781 GP

3.3 Electrical Characteristics (cont’d)

ISH1 = ISH2 = ISL1 = ISL2 = 0 A; – 40 °C < Tj < 150 °C; 8 V < VS < 18 V

unless otherwise specified

Parameter Symb Limit Values Unit Test Condition

ol min. typ. max.

Control Inputs of highside switches IH 1, 2

H-input voltage VIH High – – 2.5 V –

L-input voltage VIH Low 1 – – V –

Input voltage hysterese VIH HY – 0.5 – V –

H-input current IIH High 5 30 60 µA VIH = 5 V

L-input current IIH Low 5 14 25 µA VIH = 0.4 V

Input series resistance RI 2.7 4 6 kΩ –

Zener limit voltage VIH Z 5.4 – – V IIH = 1.6 mA

Control Inputs IL1, 2

Gate-threshold-voltage VIL th – 1.9 2.6 V Tj = – 40 °C

IDL = 1 mA – 1.7 – Tj = + 25 °C

0.8 1.1 – Tj = + 150 °C

Note: The listed characteristics are ensured over the operating range of the integrated

circuit. Typical characteristics specify mean values expected over the production

spread. If not otherwise specified, typical characteristics apply at TA = 25 °C and

VS = 12 V.

Data Sheet 13 2002-06-28

BTS 781 GP

VS

IS

CS CL

470nF 100µF

IFH1,2

IST LK1 DHVS

IST1 ST1 6

8, 17

VDSH2 VDSH1

IST LK2 -VFH2 -VFH1

IST2 ST2 11

Diagnosis Biasing and Protection

VST1

VSTL1

IIH1

VST2 IH1 5 Gate

VSTZ1

Driver

VSTL2

RO1 RO2 12 SH2 ISH2

VSTZ2 IIH1

IH2 10 Gate

VIH1 DL2 IDL2

Driver 16

GND 6 IDL LK 2 VUVON

VIH2

SH1 ISH1 VUVOFF

IGND 7

ILKCL IDL1

DL1

18

IDL LK 1

IIL1

IL1 3

VIL1 IIL2 IL2 15

VIL th 1

VIL2 2 13 VDSL1 VDSL2

VIL th 2 SL1 SL2 -VFL1 -VFL2

ISCP L 1 ISCP L 2

ISL1 ISL2

Figure 3

Test Circuit

HS-Source-Current Named during Short Named during Leakage-

Circuit Cond.

ISH1,2 ISCP H IDL LK

Data Sheet 14 2002-06-28

BTS 781 GP

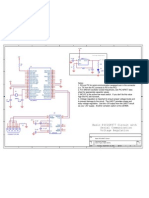

Watchdog

Reset TLE I

VS=12V

4278G

Q

RQ

Ω

100 kΩ D

RQ CQ CD D01 CS

Ω

100 kΩ 22µF 47nF Z39 10µF

WD R VCC DHVS

ST1

BCR192W

RS 6 8, 17

Can be replaced

Ω

10 kΩ by diode when

Short to Vs

to µC detection is not

RS ST2 11 needed

Diagnosis Biasing and Protection

Ω

10 kΩ ROL

560Ohm

optional for

IH1 5

Gate open load

Driver in off

RO1 RO2 12 SH2

IH2 10 Gate

Driver DL2

16

GND 9

µP M

7

SH1

DL1

18

IL1 3

IL2 15

2 13

GND SL1 SL2

Figure 4

Application Circuit

Data Sheet 15 2002-06-28

BTS 781 GP

4 Package Outlines

P-TO263-15-1

(Plastic Transistor Single

21.6 ±0.2

8.3 X2, 1) 4.4

5.56 ±0.15 1.27 ±0.1

1±0.2 8.18 ±0.15

B

4.8 X1, 1) 0.1

A 0.05

1±0.3

1) 2.4

9.25 ±0.2

7.65

(15)

2.7 ±0.3

4.7 ±0.5

14 x 1.4 0...0.15 0.5 ±0.1

0.8 ±0.1

8˚ MAX.

0.25 M A B 0.1 B

1)

Typical

Metal surface min. X1 = 3.57, X2 = 7.03, Y = 6.9

All metal surfaces tin plated, except area of cut.

Footprint

Footprint

21.6

0.8 8.4

9.5

16

0.4 1

Sorts of Packing

Package outlines for tubes, trays etc. are contained in our

Data Book “Package Information”.

SMD = Surface Mounted Device Dimensions in mm

Data Sheet 16 2002-06-28

BTS 781 GP

Published by

Infineon Technologies AG,

Bereichs Kommunikation

St.-Martin-Strasse 53,

D-81541 München

© Infineon Technologies AG 1999

All Rights Reserved.

Attention please!

The information herein is given to describe certain components and shall not be considered as warranted

characteristics.

Terms of delivery and rights to technical change reserved.

We hereby disclaim any and all warranties, including but not limited to warranties of non-infringement, regarding

circuits, descriptions and charts stated herein.

Infineon Technologies is an approved CECC manufacturer.

Information

For further information on technology, delivery terms and conditions and prices please contact your nearest

Infineon Technologies Office in Germany or our Infineon Technologies Representatives worldwide (see address

list).

Warnings

Due to technical requirements components may contain dangerous substances. For information on the types in

question please contact your nearest Infineon Technologies Office.

Infineon Technologies Components may only be used in life-support devices or systems with the express written

approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the

failure of that life-support device or system, or to affect the safety or effectiveness of that device or system. Life

support devices or systems are intended to be implanted in the human body, or to support and/or maintain and

sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other

persons may be endangered.

Data Sheet 17 2002-06-28

You might also like

- Power Supply Projects: A Collection of Innovative and Practical Design ProjectsFrom EverandPower Supply Projects: A Collection of Innovative and Practical Design ProjectsRating: 3 out of 5 stars3/5 (2)

- Diode, Transistor & Fet Circuits Manual: Newnes Circuits Manual SeriesFrom EverandDiode, Transistor & Fet Circuits Manual: Newnes Circuits Manual SeriesRating: 4.5 out of 5 stars4.5/5 (7)

- Trilithic Data Sheet Bts 7740 G: 1 1.1 FeaturesDocument17 pagesTrilithic Data Sheet Bts 7740 G: 1 1.1 FeaturesKrocodileNo ratings yet

- 7 A H-Bridge For DC-Motor Applications TLE 7209-2R: Final DatasheetDocument32 pages7 A H-Bridge For DC-Motor Applications TLE 7209-2R: Final DatasheetMecaSoftwareNo ratings yet

- 7 A H-Bridge For DC-Motor Applications 30348: Preliminary DatasheetDocument4 pages7 A H-Bridge For DC-Motor Applications 30348: Preliminary DatasheetallisonNo ratings yet

- BUK9MHH-65PNN PhilipsSemiconductorsDocument16 pagesBUK9MHH-65PNN PhilipsSemiconductorsKotaobormota DanilovichNo ratings yet

- TPS5125Document21 pagesTPS5125Shaun Dwyer Van HeerdenNo ratings yet

- TLE7209 R InfineonDocument16 pagesTLE7209 R Infineonmobil benerNo ratings yet

- 1 Tle5206 2 - 1Document23 pages1 Tle5206 2 - 1Fran CastanoNo ratings yet

- Multi-Voltage Processor Power Supply TLE 6361 G: Data SheetDocument57 pagesMulti-Voltage Processor Power Supply TLE 6361 G: Data SheetСергецNo ratings yet

- Tle 62326 Low Side SwitchDocument19 pagesTle 62326 Low Side SwitchDiego CaceresNo ratings yet

- System Basis Chip T L E 6 2 6 6 G: Integrated LS CAN, LDO and LS - HS SwitchesDocument50 pagesSystem Basis Chip T L E 6 2 6 6 G: Integrated LS CAN, LDO and LS - HS Switchescork_ieNo ratings yet

- Tle5205 2Document23 pagesTle5205 2Richard MachadoNo ratings yet

- BOMDocument1 pageBOMpriyankaNo ratings yet

- Tle 7263eDocument62 pagesTle 7263eCarlos PenagosNo ratings yet

- Data SheetDocument16 pagesData Sheetcarrei JohnNo ratings yet

- L6234 3 Fazlı Motor SürücüDocument10 pagesL6234 3 Fazlı Motor SürücüEngin UzunNo ratings yet

- Smart Octal Low-Side Switch: LogicDocument17 pagesSmart Octal Low-Side Switch: Logicjuan echeverryNo ratings yet

- CP-1000 - Chapter 07 - Codes and Circuit Diagrams 1.0Document20 pagesCP-1000 - Chapter 07 - Codes and Circuit Diagrams 1.0IMNo ratings yet

- Fds6986S: Dual Notebook Power Supply N-Channel Powertrench SyncfetDocument10 pagesFds6986S: Dual Notebook Power Supply N-Channel Powertrench Syncfetdayne81sNo ratings yet

- PDTC114T Series: 1. Product ProfileDocument11 pagesPDTC114T Series: 1. Product ProfileNicolas SixNo ratings yet

- Ic Dual Channel - FDS6982-79262Document10 pagesIc Dual Channel - FDS6982-79262BryanJermyHendrikNo ratings yet

- RT8015 2A 2MHz Synchronous Step-Down RegulatorDocument15 pagesRT8015 2A 2MHz Synchronous Step-Down RegulatorPedrolaura BethencourtNo ratings yet

- D D D D D D D D: TL16C552A, TL16C552AM Dual Asynchronous Communications Element With FifoDocument38 pagesD D D D D D D D: TL16C552A, TL16C552AM Dual Asynchronous Communications Element With FifoArturo PicolinNo ratings yet

- D D D D D D D D: TL16C552A, TL16C552AM Dual Asynchronous Communications Element With FifoDocument39 pagesD D D D D D D D: TL16C552A, TL16C552AM Dual Asynchronous Communications Element With Fifoapi-3825669No ratings yet

- STR 2 P 3 LLH 6Document12 pagesSTR 2 P 3 LLH 6GERMANNo ratings yet

- Datasheet MAX17020Document34 pagesDatasheet MAX17020lucslNo ratings yet

- Datasheet SN3218Document12 pagesDatasheet SN3218Daniel SilvaNo ratings yet

- Automotive 2ch 45 mΩ High-Side Switch with Variable OCD and OCD Mask FunctionDocument37 pagesAutomotive 2ch 45 mΩ High-Side Switch with Variable OCD and OCD Mask FunctionfsdgdgNo ratings yet

- S5851a eDocument28 pagesS5851a ekunalkundanam1046No ratings yet

- Pdtc114ee, Pdtc114em, Pdtc114et, Pdtc114eu NXPDocument17 pagesPdtc114ee, Pdtc114em, Pdtc114et, Pdtc114eu NXPTrieeNo ratings yet

- Control LED Drive Circuit: FeaturesDocument14 pagesControl LED Drive Circuit: FeaturesJacksonVelozNo ratings yet

- Infineon Tle7230r Ds v03 04 enDocument15 pagesInfineon Tle7230r Ds v03 04 enياسين الطنفوريNo ratings yet

- Description Features: PT6967 LED Driver ICDocument22 pagesDescription Features: PT6967 LED Driver ICDhivya NNo ratings yet

- 74LS290Document7 pages74LS290jaja558No ratings yet

- Ne5521 Sa5521 2Document11 pagesNe5521 Sa5521 2José AdelinoNo ratings yet

- AP2142/ AP2152: 0.5A Dual Channel Current-Limited Power SwitchDocument17 pagesAP2142/ AP2152: 0.5A Dual Channel Current-Limited Power SwitchNguyen HuanNo ratings yet

- 2-Phase Stepper-Motor Driver Bipolar-IC TLE4729G: FeaturesDocument29 pages2-Phase Stepper-Motor Driver Bipolar-IC TLE4729G: FeaturesNgoc AnNo ratings yet

- PDTA124E Series: 1. Product ProfileDocument18 pagesPDTA124E Series: 1. Product ProfiletodorloncarskiNo ratings yet

- TM1638 enDocument18 pagesTM1638 enfotakis michaelNo ratings yet

- PDTA114E Series: 1. Product ProfileDocument17 pagesPDTA114E Series: 1. Product ProfileGian MontillaNo ratings yet

- Magnetic Field Sensors for Automotive and Industrial ApplicationsDocument16 pagesMagnetic Field Sensors for Automotive and Industrial Applicationskishan1234No ratings yet

- Chapter 3 ELECTRONICS: Edition: 156Document47 pagesChapter 3 ELECTRONICS: Edition: 156Bagas dwi PrasetyoNo ratings yet

- Laser-guided door opener circuit overviewDocument9 pagesLaser-guided door opener circuit overviewsekhar469No ratings yet

- Ps 125 SMDocument7 pagesPs 125 SMGabNo ratings yet

- Dual Low Drop Voltage Regulator TLE 7469: FeaturesDocument22 pagesDual Low Drop Voltage Regulator TLE 7469: FeaturesPabloLabruneNo ratings yet

- 5A, 36V, 500Khz Step-Down Converter: General Description FeaturesDocument14 pages5A, 36V, 500Khz Step-Down Converter: General Description FeaturesHitesh GambhavaNo ratings yet

- DatasheetDocument16 pagesDatasheetAndres GuerreroNo ratings yet

- TCD2918BFG Web Datasheet en 20190108-2508346Document30 pagesTCD2918BFG Web Datasheet en 20190108-2508346shakirNo ratings yet

- MC2101 TM1628 PDFDocument22 pagesMC2101 TM1628 PDFPol ErnNo ratings yet

- Basic 16f877Document1 pageBasic 16f877api-27535945100% (1)

- Panel Board SchematicsDocument5 pagesPanel Board SchematicskevinalleinNo ratings yet

- DS1232LPDocument7 pagesDS1232LPtestzopNo ratings yet

- DatasheetDocument12 pagesDatasheetWAN MOZESNo ratings yet

- Levitation LightDocument1 pageLevitation LightHamza_AK100% (1)

- Smart Octal Low-Side Switch: Features Product SummaryDocument16 pagesSmart Octal Low-Side Switch: Features Product SummaryAriel MercochaNo ratings yet

- Usb Boost Optional U5 Lp6252Document8 pagesUsb Boost Optional U5 Lp6252Sergio SeelingNo ratings yet

- Fundamentals of Electronics 1: Electronic Components and Elementary FunctionsFrom EverandFundamentals of Electronics 1: Electronic Components and Elementary FunctionsNo ratings yet

- Solar Tracking Ebook On Sun Tracking Hardware & SoftwareDocument542 pagesSolar Tracking Ebook On Sun Tracking Hardware & Softwaregerroprinsloo100% (4)

- Elevation-Encoder With Posital Inclinometer ACS-360-1-S101-VE2-AWDocument4 pagesElevation-Encoder With Posital Inclinometer ACS-360-1-S101-VE2-AWВиктор СабовNo ratings yet

- Elevation-Encoder With Posital Inclinometer ACS-360-1-S101-VE2-AWDocument4 pagesElevation-Encoder With Posital Inclinometer ACS-360-1-S101-VE2-AWВиктор СабовNo ratings yet

- SunTrackerCircuit3 BBDocument1 pageSunTrackerCircuit3 BBВиктор СабовNo ratings yet

- Manual Speedcontrol PDFDocument2 pagesManual Speedcontrol PDFВиктор СабовNo ratings yet

- Manual SpeedcontrolDocument2 pagesManual SpeedcontrolВиктор СабовNo ratings yet

- NE555Document14 pagesNE555api-3720161100% (1)

- Trilithic Data Sheet Bts 781 GP: 1 1.1 FeaturesDocument17 pagesTrilithic Data Sheet Bts 781 GP: 1 1.1 FeaturesВиктор СабовNo ratings yet

- BTS 723Document15 pagesBTS 723Виктор СабовNo ratings yet

- IRF740AS/L: Smps MosfetDocument10 pagesIRF740AS/L: Smps MosfetВиктор СабовNo ratings yet

- IRF540 IRF540FI: N - Channel Enhancement Mode Power Mos TransistorsDocument9 pagesIRF540 IRF540FI: N - Channel Enhancement Mode Power Mos TransistorsВиктор СабовNo ratings yet

- Trejler Ebs eDocument43 pagesTrejler Ebs eВиктор СабовNo ratings yet

- BTS 723Document15 pagesBTS 723Виктор СабовNo ratings yet

- Trejler Ebs eDocument43 pagesTrejler Ebs eВиктор СабовNo ratings yet

- Andrew Burrows Diagram Equipment Code ListDocument149 pagesAndrew Burrows Diagram Equipment Code ListВиктор Сабов100% (1)

- 450 Dxi Wiring Numbers PDFDocument32 pages450 Dxi Wiring Numbers PDFvaleriy100% (4)

- 16s181 Ahelical Teetha PDFDocument11 pages16s181 Ahelical Teetha PDFعبدالغني القباطيNo ratings yet

- Electrics DAF XF CF Euro 4, 5Document199 pagesElectrics DAF XF CF Euro 4, 5Carolina100% (12)

- Eurocargo SCR InstructionDocument229 pagesEurocargo SCR InstructionВиктор Сабов100% (1)

- A 900-MHz 1.25-dB Noise-Figure Differential-Output LNA With 12.5 DB MW FoMDocument4 pagesA 900-MHz 1.25-dB Noise-Figure Differential-Output LNA With 12.5 DB MW FoMJyotirmay SarkarNo ratings yet

- NZ2016SH (32k) - e - NSC5026D 3.3V +100ppmDocument2 pagesNZ2016SH (32k) - e - NSC5026D 3.3V +100ppmDumarronNo ratings yet

- Digital Electronics Ec 1201Document34 pagesDigital Electronics Ec 1201ainugiri100% (1)

- 8-Bit Microcontroller With 8K Bytes In-System Programmable Flash Atmega48/V Atmega88/V Atmega168/V PreliminaryDocument33 pages8-Bit Microcontroller With 8K Bytes In-System Programmable Flash Atmega48/V Atmega88/V Atmega168/V PreliminaryRubén Pérez ArmasNo ratings yet

- EC 8392 Digital ElectronicsDocument46 pagesEC 8392 Digital Electronicspadmaa1No ratings yet

- IGBT Design ConsiderationsDocument2 pagesIGBT Design ConsiderationsabcNo ratings yet

- Analog Devices - MT-016Document6 pagesAnalog Devices - MT-016ModyKing99No ratings yet

- LTLS E3 ModulatorDocument20 pagesLTLS E3 ModulatorGenesis Rosario100% (1)

- An5346 Stm32g4 Adc Use Tips and Recommendations StmicroelectronicsDocument15 pagesAn5346 Stm32g4 Adc Use Tips and Recommendations StmicroelectronicsPaulo PecegueiroNo ratings yet

- M29F800DT M29F800DB: 8 Mbit (1Mb x8 or 512Kb x16, Boot Block) 5V Supply Flash MemoryDocument40 pagesM29F800DT M29F800DB: 8 Mbit (1Mb x8 or 512Kb x16, Boot Block) 5V Supply Flash MemoryAn as akrasNo ratings yet

- Intro To BJT Small SignalDocument35 pagesIntro To BJT Small Signaldaserock83100% (1)

- ELX304 Ref ExamDocument13 pagesELX304 Ref ExamNadeesha Bandara0% (1)

- LIC EEE-Multiple Choice Questions 2017Document11 pagesLIC EEE-Multiple Choice Questions 2017jagan40% (5)

- 208747-Article Text-801929-1-10-20200119Document6 pages208747-Article Text-801929-1-10-20200119OlegNo ratings yet

- Pin Description and Signals of 8085 MicroprocessorDocument9 pagesPin Description and Signals of 8085 MicroprocessorKripanand JhaNo ratings yet

- Building A Processor From ScratchDocument8 pagesBuilding A Processor From Scratchnew accNo ratings yet

- RX63N, RX631 Group: Application NoteDocument40 pagesRX63N, RX631 Group: Application NoteCharoon SuriyawichitwongNo ratings yet

- EE303 Digital System - 2010Fall Registers and Counters LectureDocument50 pagesEE303 Digital System - 2010Fall Registers and Counters LectureXun WangNo ratings yet

- TL331B, TL391B and TL331 Single Comparators: 1 Features 3 DescriptionDocument27 pagesTL331B, TL391B and TL331 Single Comparators: 1 Features 3 DescriptionJohn Jaque CaleNo ratings yet

- Oscillators - EDC PDFDocument21 pagesOscillators - EDC PDFanjanaNo ratings yet

- Baluns by W7KVIDocument54 pagesBaluns by W7KVIechobot1No ratings yet

- Cryptobank ICO: Shortwave Antenna Ampli ErDocument2 pagesCryptobank ICO: Shortwave Antenna Ampli ErFernando MartinNo ratings yet

- High performance BIT3713 PWM controller datasheetDocument11 pagesHigh performance BIT3713 PWM controller datasheetRodolfo CarruyoNo ratings yet

- Final Report Safety Guard BlindDocument32 pagesFinal Report Safety Guard BlindAshutosh Dabas100% (3)

- Application Note AN-1071: Class D Audio Amplifier BasicsDocument14 pagesApplication Note AN-1071: Class D Audio Amplifier BasicsAndrea FasatoNo ratings yet

- Linear Integrated Circuits Question BankDocument17 pagesLinear Integrated Circuits Question BankDeepak SantNo ratings yet

- Features Description: 12-Bit, Multiplying D/A ConverterDocument8 pagesFeatures Description: 12-Bit, Multiplying D/A ConverterGabriel RacovskyNo ratings yet

- 11 - Class D Amplifiers - 2006 - Audio Power Amplifier Design HandbookDocument9 pages11 - Class D Amplifiers - 2006 - Audio Power Amplifier Design HandbookNaveen KandiahNo ratings yet

- DLD 7 StudentDocument6 pagesDLD 7 StudentAminul IslamNo ratings yet

- Final PresentationDocument21 pagesFinal PresentationGustifa fauzanNo ratings yet