Professional Documents

Culture Documents

Output Stages 1

Uploaded by

Pk KumarCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Output Stages 1

Uploaded by

Pk KumarCopyright:

Available Formats

Output Stages 1

Aloke Dutta/EE/IIT Kanpur 1

Requirements:

* Sufficient drive current/power transfer to load

* Low output distortion

* Ideal voltage source: Thevenin equivalent V0 with R 0 → 0

* Voltage gain A v independent of load (ideally unity)

* No phase shift between input and output

* Low Standby Power (while not driving any load)

* High Power Conversion Efficiency

average power delivered to load

average power drawn from supply

* Should not degrade frequency response

Aloke Dutta/EE/IIT Kanpur 2

BJT output stages preferred due to their large current

handling capability

Classification:

Depends on the conduction angle ()

angle over the complete cycle (360) for which

the output transistors are on

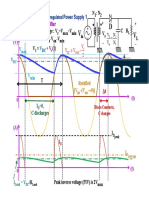

* Class A: = 360 and max 25% (large standby power)

* Class B: slightly less than 180 and max 78.5%

* Class AB: = 180 and max 78.5%

* Class C: 180 - Used in RF applications

We shall be discussing only about Class B and Class AB

Aloke Dutta/EE/IIT Kanpur 3

Class B:

Uses complementary set of output transistors

(npn and pnp, NMOS and PMOS)

One takes care of the positive half cycle, while

the other takes care of the negative half cycle

slightly less than 180 for each

Both ouput devices never on simultaneously

Zero Standby Power − significant advantage

Also known as Push-Pull stage

Aloke Dutta/EE/IIT Kanpur 4

During positive half cycle, the stage pushes current

through load, while during negative half cycle, the

stage pulls current away from the load

Very high max of 78.5%

However, there is a big limitation, known as Crossover

Distortion occuring during zero crossings of signal

This is because for a BJT/MOS Class B stage, we need a

voltage at least equal to V /VTN (VTP ) for the output stage

transistors to turn on

This is also known as Deadband Distortion

Aloke Dutta/EE/IIT Kanpur 5

Class AB:

Eliminates crossover distortion by prebiasing the

output transistors, so that they remain at the verge

of conduction in the standby state

exactly equal to 180

max slightly less than 78.5% due to a small amount

of standby power

Extremely popular and most widely used

Aloke Dutta/EE/IIT Kanpur 6

VCC

Class B Push-Pull Output Stage:

Q1

BJT Implementation: Vi V0

Also known as Complementary Output Stage

Q2 RL

Uses dual symmetric power supply (VCC -VEE )

Typical values used: 3 V, 5 V, 12 V, 15 V VEE

Q-point: Vi = V0 = 0 VBE1 = VEB2 = 0

Both Q1 and Q 2 cutoff Zero standby power

As Vi beyond zero, VBE1 and VEB2

Note: VBE1 + VEB2 = 0 (always)

Q1 moves towards turning on and Q2 is pushed

deeper into cutoff

Aloke Dutta/EE/IIT Kanpur 7

However, Vi has to become at least equal to V for

Q1 to conduct (based on the simple model of diode)

Till then, V0 remains zero

Once Vi becomes greater than V , Q1 turns on, supplies

current to the load (R L ), and V0 starts to increase

Similarly, As Vi below zero, VBE1 and VEB2

Q2 moves towards turning on and Q1 is pushed

deeper into cutoff

Again, Vi has to become at least equal to − V for

Q 2 to conduct

Aloke Dutta/EE/IIT Kanpur 8

Once Vi becomes less than − V , Q 2 turns on,

pulls current away from the load (R L ), and V0

starts to decrease (note that V0 is negative

under this condition)

That's the origin of the name Push-Pull

Note: Each output transistor remains on for

half the cycle

Voltage Transfer Characteristic (VTC):

Plot of V0 versus Vi

Note the deadband (V0 = 0) between − V and V

Aloke Dutta/EE/IIT Kanpur 9

V0

[VCC – VCE1(sat)]

Q1 saturated

Q1, Q2 off Q1 on

Q2 off

slope ~ 1

–V

[VEE + VEC2(sat) – VEB2]

0

[VCC – VCE1(sat) + VBE1] Vi

V

slope ~ 1

Q2 on

Q1 off

Q2 saturated

[VEE + VEC2(sat)]

Aloke Dutta/EE/IIT Kanpur 10

For positive Vi above V , V0 increases almost linearly

with Vi with a slope slightly less than unity and no

phase shift, since it is a CC stage

As V0 , VCE1 , and Q starts to move towards saturation

Positive V0,max = VCC − VCE1(sat )

However, for this to happen, Vi has to be greater than

VCC ( there is an extra drop of VBE1 )

This point will never be reached

The characteristic for negative Vi can be similarly

understood

Aloke Dutta/EE/IIT Kanpur 11

Crossover Distortion:

Vi, V0

VM Crossover

(Deadband)

Vi V0

Distortion

V

0

t

–V

Aloke Dutta/EE/IIT Kanpur 12

Quantified by (refer to the diagram)

−1 V

Given by: = sin

M

V

VM : Amplitude of the input signal

Appears four times over a complete cycle

Quantified by a term known as the Total Crossover

Distortion (TCD), expressed in percent:

2

TCD = 100%

Problem becomes more acute as VM

For VM < V , no output (V0 = 0 always)

Aloke Dutta/EE/IIT Kanpur 13

MOS Implementation:

VDD

Working principle absolutely

VSS

similar to BJT implementation

M1

Only exception that V Vi V0

replaced by VTN and VTP

M2

Q-point: Vi = V0 = 0 RL

Note that both devices VDD

suffer from body effect VSS

VTN and VTP function of V0

VTC significantly nonlinear

Output shows more distortion

Aloke Dutta/EE/IIT Kanpur 14

Output can swing all the way between VDD and VSS

However, as V0 during the positive half cycle, VDS1

M1 may enter linear region

Similar situation will occur during the negative half

cycle, and M 2 may enter linear region

This produces additional distortion in the output

Added to the fact that MOS devices are inherently

much poorer than their BJT counterparts in terms of

current carrying ability, makes this stage quite a poor

choice (needs very large W/L ratio)

Aloke Dutta/EE/IIT Kanpur 15

Class AB Push -Pull Output Stage:

Note: In a Class B stage, crossover distortion arises

due to the fact that the transistors are absolutely cold

in the standby state, i.e., dead off

If somehow they can be prebiased , such that they are

very close to the turn-on state, but not quite there,

then a slight swing of input either way would make

one of these transistors turn on and either supply

current to the load or pull current away from load

This is the whole idea behind a Class AB stage

Obvious fallout: Dissipation of standby power

Aloke Dutta/EE/IIT Kanpur 16

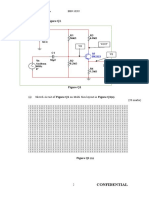

Note the additional circuitry VCC

in terms of IQ -Q3 -Q 4

Q3 and Q 4 are diode-connected IQ

This combination facilitates +

Q1

creation of a DC bias VBIAS Q3 I0

V0

between the bases of Q1 and Q 2 VBIAS

Consider idling condition with Q4

RL

Vi

–

R L open-circuited (I0 = 0) Q2

Neglecting base currents of Q1 -Q 2 , VEE

I BIAS flows through Q3 -Q 4 , and

develops a voltage drop:

Aloke Dutta/EE/IIT Kanpur 17

IQ2

VBIAS = VBE3 + VBE4 = VT ln

I I

S3 S4

IQ , IS3 , and IS4 chosen in such a way that VBIAS 2V

Note: VBIAS is also equal to (VBE1 + VEB2 )

Thus, Q1 -Q 2 remain at the verge of conduction,

carrying a standby (or idling) current IStandby

Causes standby (or idling) power dissipation

Noting that

IStandby

2

VBIAS = VBE1 + VEB2 = VT ln

I I

S1 S2

Aloke Dutta/EE/IIT Kanpur 18

and equating the two equations for VBIAS:

IS1IS2

Istandby = IQ

IS3 IS4

Q1 -Q 2 has to supply/sink large current to/from load

Hence, their BE junction areas are made large

Large IS

IS of Q1 -Q 2 is typically 10 times or more than that of Q3 -Q 4

IStandby is at least 10 times or more that of IQ

Adds to power overhead of the circuit

There are better versions of the circuit available,

which we would explore in the chapter on op-amps

Aloke Dutta/EE/IIT Kanpur 19

Another Option:

Use VBE -multiplier circuit VCC

R2

VBIAS = VBE3 1 + IQ

R1

Q1

Values of R1 and R 2 chosen +

R2

such that VBIAS 2V V0

Q3 VBIAS

(We have come across a similar

R1 RL

problem in the mid-sem exam) Vi

–

Q2

Since the resistors appear as a

VEE

ratio, this circuit has excellent

thermal tracking behavior

Aloke Dutta/EE/IIT Kanpur 20

You might also like

- Multivibrator BonDocument14 pagesMultivibrator BontchoudacyNo ratings yet

- Mod 3 PDFDocument22 pagesMod 3 PDFcynthiaNo ratings yet

- Power AmplifierDocument37 pagesPower AmplifierSristick100% (6)

- Ch5 - AmplifiersDocument149 pagesCh5 - AmplifiersRaghav AroraNo ratings yet

- Ch7 Power Amp PDFDocument41 pagesCh7 Power Amp PDFy shuangNo ratings yet

- Multi VibratorsDocument11 pagesMulti VibratorsPallavi Kr K RNo ratings yet

- Lecture 3-Logic Families Unit 2Document27 pagesLecture 3-Logic Families Unit 2q898awaNo ratings yet

- Introduction To Op-AmpDocument75 pagesIntroduction To Op-AmpAkshayNo ratings yet

- Differential Amplifier AnalysisDocument20 pagesDifferential Amplifier AnalysisAngelicaNo ratings yet

- Abert AinoDocument12 pagesAbert AinoAINOMUGISHA ABERTNo ratings yet

- Chapter 7 Multi Vibrators and Wave Shaping CircuitsDocument8 pagesChapter 7 Multi Vibrators and Wave Shaping CircuitsJibril JundiNo ratings yet

- Circuits and Electronics Chapter 3 and NotesDocument49 pagesCircuits and Electronics Chapter 3 and NotesDr. S. DasNo ratings yet

- CONTRACT - JAP006-D73 132/11kV PALM, JUMEIRAH S/S (4 Nos) 11Kv Switchgear VT CalculationDocument6 pagesCONTRACT - JAP006-D73 132/11kV PALM, JUMEIRAH S/S (4 Nos) 11Kv Switchgear VT CalculationmadhavanNo ratings yet

- Lecture 18-20 - Ideal Zener Diodes and BJTDocument27 pagesLecture 18-20 - Ideal Zener Diodes and BJTCHAITANYA KRISHNA CHAUHANNo ratings yet

- Chapter 8Document34 pagesChapter 8Abhinav GuptaNo ratings yet

- Multivibrators: A Multivibrator Is Used To Implement Simple Two-State Three TypesDocument15 pagesMultivibrators: A Multivibrator Is Used To Implement Simple Two-State Three TypesVenkata Rao NekkantiNo ratings yet

- Lecture # 4 (Power Transistors)Document31 pagesLecture # 4 (Power Transistors)Garuda khanNo ratings yet

- Lecture # 4: Power TransistorsDocument31 pagesLecture # 4: Power TransistorsShehroz BaigNo ratings yet

- DTL Gate Logic Family OverviewDocument9 pagesDTL Gate Logic Family Overviewعہۣۗثہۣۗمہۣۗان الہۣۗضہۣۗاحہۣۗيNo ratings yet

- CH 9 - Op-Amp - Part IIDocument53 pagesCH 9 - Op-Amp - Part IIYatish SharmaNo ratings yet

- Datasheet lm124Document4 pagesDatasheet lm124Valdark Valente MdlNo ratings yet

- LM324 PDFDocument4 pagesLM324 PDFCarolina IskandarNo ratings yet

- BJT Differential AmplifierDocument4 pagesBJT Differential Amplifierdominggo100% (4)

- Electronics Circuit Analysis Notes PDFDocument40 pagesElectronics Circuit Analysis Notes PDFAditya ThakkarNo ratings yet

- 15 Power Amplifier Class B ABDocument16 pages15 Power Amplifier Class B ABAnonymous 5kvqS5LNo ratings yet

- L060 Push Pull (2UP)Document10 pagesL060 Push Pull (2UP)srikanthkmsNo ratings yet

- L12 PNP DC Analysis, Voltage Transfer Characteristic, BJT Biasing 1Document18 pagesL12 PNP DC Analysis, Voltage Transfer Characteristic, BJT Biasing 1MANI SINGHNo ratings yet

- BJT Biasing Circuits and Self Bias ConfigurationDocument14 pagesBJT Biasing Circuits and Self Bias ConfigurationSiddhant AbhishekNo ratings yet

- Eec 225Document15 pagesEec 225Ezekiel Iyamu100% (1)

- Confidential: Refer To Figure Q1Document3 pagesConfidential: Refer To Figure Q1Zhamir ZhakwanNo ratings yet

- Electronics Ch13 PDFDocument18 pagesElectronics Ch13 PDFAbdullah MuzammilNo ratings yet

- Multistage AmplifiersDocument22 pagesMultistage AmplifiersParvinder SinghNo ratings yet

- Ac and DC Biasing-Bjts and Fet: Learning ObjectivesDocument24 pagesAc and DC Biasing-Bjts and Fet: Learning ObjectiveskalyanNo ratings yet

- BJT Small Sig-2Document77 pagesBJT Small Sig-2Abdullah ShahNo ratings yet

- Electronics Thyristors PDFDocument32 pagesElectronics Thyristors PDFمنتظر احمد حبيترNo ratings yet

- Power Eectronics Lab Manual#09Document6 pagesPower Eectronics Lab Manual#09Muhammad Salman ShahidNo ratings yet

- Timing Circuits: Waveform Shaping CircuitDocument7 pagesTiming Circuits: Waveform Shaping CircuitAbdulrahman NasserNo ratings yet

- Generate Square Waves with Op-Amp Relaxation OscillatorDocument2 pagesGenerate Square Waves with Op-Amp Relaxation OscillatorPrathyusha YedlaNo ratings yet

- L10 BJT Applications and BiasingDocument23 pagesL10 BJT Applications and BiasingpojanopeNo ratings yet

- EECE 310 Sample BJT ProblemsDocument8 pagesEECE 310 Sample BJT ProblemsALi AlawiehNo ratings yet

- Load Line and Q-PointDocument3 pagesLoad Line and Q-PointRavi Kanth M NNo ratings yet

- L-3 (DK) (Pe) ( (Ee) Nptel) 9Document5 pagesL-3 (DK) (Pe) ( (Ee) Nptel) 9GagneNo ratings yet

- To Study The Operation of UJT As A Pulse Generation CircuitDocument5 pagesTo Study The Operation of UJT As A Pulse Generation CircuitkashishlalaNo ratings yet

- BJT Multistage Amplifier StagesDocument9 pagesBJT Multistage Amplifier StagesYue KaiNo ratings yet

- RECTIFIERS AND FILTERS CIRCUIT DIAGRAMDocument21 pagesRECTIFIERS AND FILTERS CIRCUIT DIAGRAMveenau 1No ratings yet

- Electronic Devices and Circuits (Lab) : Experiment No. 13: BJT Transistor As A SwitchDocument9 pagesElectronic Devices and Circuits (Lab) : Experiment No. 13: BJT Transistor As A SwitchPrince SamNo ratings yet

- EEL 7300 - Chapter V - Relaxation Oscillators and Timers 2020-1 - VisualsDocument19 pagesEEL 7300 - Chapter V - Relaxation Oscillators and Timers 2020-1 - VisualsVanderson Xavier vandilolNo ratings yet

- Chapter 6Document8 pagesChapter 6Gizachew BalchaNo ratings yet

- The Bootstrapped Switch A Circuit For All SeasonsDocument4 pagesThe Bootstrapped Switch A Circuit For All Seasons于富昇No ratings yet

- 04 Power SCD 2Document82 pages04 Power SCD 2riajulNo ratings yet

- Electronic Circuit AnalysisDocument23 pagesElectronic Circuit AnalysisAnonymous uspYoqENo ratings yet

- PUC EEE-311 Class-5Document14 pagesPUC EEE-311 Class-5Supreme FfNo ratings yet

- Homewrok 1 BJTDocument2 pagesHomewrok 1 BJTersahinmert63No ratings yet

- Op-Amp Internal CircuitDocument13 pagesOp-Amp Internal CircuitNazeer HussainNo ratings yet

- Clippers NJHGDocument25 pagesClippers NJHGIjaz TalibNo ratings yet

- Lab 2 - Design Simulation and Testing of Full Wave Centre Tapped TransformerDocument8 pagesLab 2 - Design Simulation and Testing of Full Wave Centre Tapped TransformerruduitududtNo ratings yet

- 30 - Properties of STM With Constant ADocument2 pages30 - Properties of STM With Constant APk KumarNo ratings yet

- 29 - Properties of STMDocument3 pages29 - Properties of STMPk KumarNo ratings yet

- 23 - Examples For Matrix FunctionsDocument2 pages23 - Examples For Matrix FunctionsPk KumarNo ratings yet

- 31 - Examples On State Transition MatrixDocument2 pages31 - Examples On State Transition MatrixPk KumarNo ratings yet

- 20 - Minimal PolynomialDocument1 page20 - Minimal PolynomialPk KumarNo ratings yet

- 21 - Cayley Hamilton TheoremDocument1 page21 - Cayley Hamilton TheoremPk KumarNo ratings yet

- ESC201 UDas Lec12 Step and Freq Response of RLCDocument7 pagesESC201 UDas Lec12 Step and Freq Response of RLCPk KumarNo ratings yet

- 33 - Solution To State Space RepresentationDocument1 page33 - Solution To State Space RepresentationPk KumarNo ratings yet

- 27 - State Space Representation To Transfer FunctionDocument1 page27 - State Space Representation To Transfer FunctionPk KumarNo ratings yet

- ESC201 UDas Lec16class Diodes - SupplyDocument6 pagesESC201 UDas Lec16class Diodes - SupplyaamnNo ratings yet

- 22 - Function of A As A PolynomialDocument1 page22 - Function of A As A PolynomialPk KumarNo ratings yet

- 18 - Generalized EigenvectorsDocument3 pages18 - Generalized EigenvectorsPk KumarNo ratings yet

- ESC201 UDas Lec5 CKT Eqv PDFDocument8 pagesESC201 UDas Lec5 CKT Eqv PDFraj sahuNo ratings yet

- RLC_series_parallel_responseDocument7 pagesRLC_series_parallel_responsePk KumarNo ratings yet

- ESC201 UDas Lec17 Bridge Supply - BJTDocument5 pagesESC201 UDas Lec17 Bridge Supply - BJTPk KumarNo ratings yet

- ESC201 UDas Lec16class Diodes - SupplyDocument6 pagesESC201 UDas Lec16class Diodes - SupplyaamnNo ratings yet

- ESc201 Diodes Act Like SwitchesDocument9 pagesESc201 Diodes Act Like SwitchesPk KumarNo ratings yet

- ESC201 UDas Lec10 Steady State RLC PDFDocument10 pagesESC201 UDas Lec10 Steady State RLC PDFraj sahuNo ratings yet

- ESc201A Miniquiz1 Soln PDFDocument2 pagesESc201A Miniquiz1 Soln PDFPk KumarNo ratings yet

- ESC201 UDas Lec4 Ckts AnalysisDocument9 pagesESC201 UDas Lec4 Ckts Analysisraj sahuNo ratings yet

- ESc201 Lecture on Diode Applications and Equivalent Circuit ModelsDocument5 pagesESc201 Lecture on Diode Applications and Equivalent Circuit ModelsPk KumarNo ratings yet

- ESC201 UDas Lec30 Digital Addition PDFDocument8 pagesESC201 UDas Lec30 Digital Addition PDFPk KumarNo ratings yet

- ESC201 UDas Lec8 Time Vary Sinusoid PDFDocument7 pagesESC201 UDas Lec8 Time Vary Sinusoid PDFraj sahuNo ratings yet

- ESc201A Homework 2 Solutions and Power DissipationDocument9 pagesESc201A Homework 2 Solutions and Power DissipationPk KumarNo ratings yet

- Lecture 12: 31 Jan 2017 OverviewDocument2 pagesLecture 12: 31 Jan 2017 OverviewPk KumarNo ratings yet

- Lecture 13: 02 Feb 2017Document3 pagesLecture 13: 02 Feb 2017Pk KumarNo ratings yet

- ESc201A HA5 Soln 06 - 09 19Document6 pagesESc201A HA5 Soln 06 - 09 19Pk KumarNo ratings yet

- ESC201 UDas Lec1 IntroDocument16 pagesESC201 UDas Lec1 IntroPk KumarNo ratings yet

- ESc201A HA8soln 21 - 10 19Document8 pagesESc201A HA8soln 21 - 10 19Pk KumarNo ratings yet

- V V V V V V V V: Esc201A Home Assignment 3 Aug. 19, 2019Document9 pagesV V V V V V V V: Esc201A Home Assignment 3 Aug. 19, 2019Pk KumarNo ratings yet

- 3 Phase Voltage Drop and Fault Current CalculatorDocument1 page3 Phase Voltage Drop and Fault Current CalculatorArnold SapantaNo ratings yet

- Brochure Batterie Lithium, BYD, Premium LVS HVS Et HVMDocument4 pagesBrochure Batterie Lithium, BYD, Premium LVS HVS Et HVMSINES France100% (1)

- A Novel Approach of Sensorized Gloves For Paralyzed Person.Document16 pagesA Novel Approach of Sensorized Gloves For Paralyzed Person.Pranik K NikoseNo ratings yet

- Impact of Impurities, Interface Traps and Contacts On MoS2 MOSFETs - Modelling and ExperimentsDocument4 pagesImpact of Impurities, Interface Traps and Contacts On MoS2 MOSFETs - Modelling and ExperimentsdebanjanfinNo ratings yet

- Lab Manual: Embedded System Lab Lab Code: 18ECL66 Semester: VIDocument43 pagesLab Manual: Embedded System Lab Lab Code: 18ECL66 Semester: VIrakesh hiremathNo ratings yet

- Comfort Sensor Using Fuzzy Logic and ArduinoDocument1 pageComfort Sensor Using Fuzzy Logic and ArduinoAlfredo MartinezNo ratings yet

- Clock Domain CrossingDocument15 pagesClock Domain CrossingMukesh PandaNo ratings yet

- Presentation of Kaifeng Shengda Water Meter Co.,Ltd - 2Document37 pagesPresentation of Kaifeng Shengda Water Meter Co.,Ltd - 2imata konjoNo ratings yet

- Automatic Voltage Regulator (Avr) : General Description Technical SpecificationDocument4 pagesAutomatic Voltage Regulator (Avr) : General Description Technical SpecificationsabujNo ratings yet

- PLC Introduction: Programmable Logic Controller BasicsDocument3 pagesPLC Introduction: Programmable Logic Controller Basicssreekanthtg007No ratings yet

- Basic LCD TV Trouble Shooting Guide by Bud MartinDocument9 pagesBasic LCD TV Trouble Shooting Guide by Bud MartinJustin WilliamsNo ratings yet

- Crane's PLCDocument15 pagesCrane's PLCElectrifying GuyNo ratings yet

- CSA Approval - GasAlertMicroClipSeries1730355 - 1Document3 pagesCSA Approval - GasAlertMicroClipSeries1730355 - 1Edgar ValverdeNo ratings yet

- Pec Answers 601 To 700Document8 pagesPec Answers 601 To 700RICHARD BARGONo ratings yet

- MTL5018 AcDocument1 pageMTL5018 AcJagadesh C S NadarNo ratings yet

- GPS 15xH/15xL Technical Specifications: 190-00266-03 Revision A December 2009Document40 pagesGPS 15xH/15xL Technical Specifications: 190-00266-03 Revision A December 2009raoultrifan7560No ratings yet

- CT Model ImbDocument13 pagesCT Model ImbpugaliaanuragNo ratings yet

- HJ602Document2 pagesHJ602Salih Halil SonmezNo ratings yet

- Umbrella Tool Changer - Set Parameter 257 - Spindle Orientation OffsetDocument3 pagesUmbrella Tool Changer - Set Parameter 257 - Spindle Orientation Offset2aicnNo ratings yet

- Reference Power Systems Protection Handbook PDFDocument196 pagesReference Power Systems Protection Handbook PDFJavier Condori Quilla100% (1)

- Expt 1 DC Machine Using SimulinkDocument10 pagesExpt 1 DC Machine Using SimulinkGG wpNo ratings yet

- Manual Multi-Amp CB-832 - UgDocument29 pagesManual Multi-Amp CB-832 - UgMauricio Bonilla100% (1)

- Battery Tester Circuit Schematic - EEWeb CommunityDocument8 pagesBattery Tester Circuit Schematic - EEWeb Communitybnc1No ratings yet

- AXIOM Luminos TF With Mobile Flat Detector: Answers For LifeDocument20 pagesAXIOM Luminos TF With Mobile Flat Detector: Answers For Lifeuriel vazquezNo ratings yet

- I To P and P To E ConvertorsDocument121 pagesI To P and P To E ConvertorsBhautik DaxiniNo ratings yet

- Sunnyvale/Saint Petersburg Kilowatt-Plus HF AmplifierDocument7 pagesSunnyvale/Saint Petersburg Kilowatt-Plus HF Amplifierdavid reyes100% (1)

- Obituary of James Martin Lafferty, pioneer in vacuum scienceDocument2 pagesObituary of James Martin Lafferty, pioneer in vacuum scienceGeorge AcostaNo ratings yet

- Media Specsheets Jaquet T400Document4 pagesMedia Specsheets Jaquet T400Pavel MelnikovNo ratings yet

- Fault CodeDocument10 pagesFault CodeAmir Reza100% (1)

- InfiniSolar V II-3P-6KW-9KW-15KWDocument1 pageInfiniSolar V II-3P-6KW-9KW-15KWHusam Apoud100% (1)