Professional Documents

Culture Documents

EE290C - Spring 2011 RX FIR Equalizers: - Currently Not Very Popular - Why?

Uploaded by

Fahmida Pervin BrishtyOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

EE290C - Spring 2011 RX FIR Equalizers: - Currently Not Very Popular - Why?

Uploaded by

Fahmida Pervin BrishtyCopyright:

Available Formats

RX FIR Equalizers

EE290C – Spring 2011 • Currently not very popular – why?

Lecture 8: Equalization: FIR II and DFE

Elad Alon

Dept. of EECS

EE290C Lecture 8 4

VM TX + Equalization Coefficient Shuffling Architecture

• First implementation (K.-L. J. Wong, JSSC 2004): • Lee, Razavi, CICC 2001

EE290C Lecture 8 2 EE290C Lecture 8 5

Constant Current VM TX Design Shuffling Implementation

• D. Dettloff, ISSCC 2010 • Can shuffle digital tap coefficients or analog

inputs

EE290C Lecture 8 3 EE290C Lecture 8 6

Interleaving A Reminder

• Often combined with tap shuffling

• Ex: J. Jaussi, ISSCC 2004

EE290C Lecture 8 7 EE290C Lecture 8 10

DFE: Implementation Self-Loading

• Creates bandwidth 0.6

RX_in C = 20fF

limit 0.5 L

C = 40fF

• No matter how 0.4 L

C = 80fF

much power you L

m

0.3

G

spend 0.2

0.1

• DFE has increased 0

• Design driven by feedback latency constraint “self-loading” due 0 0.2 0.4 0.6

GBW/(ω /γ )

0.8 1

T

• New summer output needs to settle (at comparator to taps…

input) within one bit time

EE290C Lecture 8 8 EE290C Lecture 8 11

DFE Summer Design DFE Summer Design

• Key constraint:

tdig_fb + tana_settle = Tbit

• Need some Nτ of

settling:

τsum = (Tbit – tdig_fb)/Nτ

• Typically want ~4τ for ~98% settling

EE290C Lecture 8 9 EE290C Lecture 8 12

Maximum Cancelled ISI Split Summation

!0Gb/s DFE

0.05 • B. Leibowitz, ISSCC 2007

tdig = 30ps

0.04 tdig = 40ps

tdig = 50ps

0.03

m

G

0.02

0.01

0

0 2 4 6 8 10

M

DFE

• There is a maximum MDFE you can achieve

• Don’t forget that every tap has to handle worst-

case possible ISI

• Implies max. number of taps (in given tech.)

EE290C Lecture 8 13 EE290C Lecture 8 16

TX FIR RX DFE Duality All CML Design

• Can use same techniques we talked about in TX • H. Wang, VLSI 2009

for RX DFE • Over 20Gb/s in 65nm CMOS

• But still need to watch out for digital power…

Vin

d0

clk

0 – Imax/2

z-1

d0

d1 d1

0 – Imax/2 d2

z-1

d1

d2

0 – Imax/4 d2

EE290C Lecture 8 14 EE290C Lecture 8 17

Closing the First Tap Loop Unrolling

• K. Parhi, ISCAS 1990

+1+α +α d n | d n −1 = 1

+1-α

+α xn d n −1

dClk D Q

-α

-1+α

-α

d n | d n −1 = 0

-1-α dClk

EE290C Lecture 8 15 EE290C Lecture 8 18

Extended Loop Unrolling Practical DFE Design Issues

EE290C Lecture 8 19 EE290C Lecture 8 22

LE + DFE Practical DFE Design Issues

EE290C Lecture 8 20 EE290C Lecture 8 23

Practical DFE Design Issues

EE290C Lecture 8 21

You might also like

- Spec-Do 28Document20 pagesSpec-Do 28李小华No ratings yet

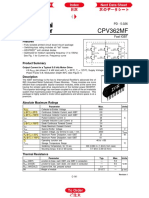

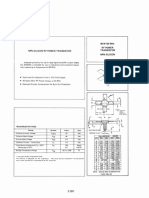

- CPV 363 MFDocument9 pagesCPV 363 MFSergio MuriloNo ratings yet

- ECE 385 Lab 3 - Digital Systems Lab IntroductionDocument17 pagesECE 385 Lab 3 - Digital Systems Lab IntroductionMichael QiuNo ratings yet

- hmc580st89Document6 pageshmc580st89payam79bNo ratings yet

- ELEC4602 Microelectronics Design and Technology: ObjectiveDocument4 pagesELEC4602 Microelectronics Design and Technology: ObjectiveMuhammad RohfadliNo ratings yet

- B1568 - PNP Power Transistor ( 80V, 4A) (D1933 NPN)Document4 pagesB1568 - PNP Power Transistor ( 80V, 4A) (D1933 NPN)LangllyNo ratings yet

- Comparison TablesDocument1 pageComparison TablesPanos MarkoNo ratings yet

- 1504 RG174 EngDocument2 pages1504 RG174 EngMANAN BELANINo ratings yet

- Cryogenic Operation of A 24 GHZ Mmic Sige HBT Medium Power AmplifierDocument6 pagesCryogenic Operation of A 24 GHZ Mmic Sige HBT Medium Power AmplifierMinou BenkNo ratings yet

- EPE6119GDocument1 pageEPE6119Gmmdabase8617No ratings yet

- 000-1-ST2001Document6 pages000-1-ST2001robson lopes bezerraNo ratings yet

- Applying Fast Recovery Diodes - 5SYA 2064Document12 pagesApplying Fast Recovery Diodes - 5SYA 2064Sumeet TrivediNo ratings yet

- DatasheetDocument8 pagesDatasheetVACHAN KUMAR 17BEE1151No ratings yet

- Impact of The Source/drain Implants On Threshold Voltage Matching in Deep Sub-Micron CMOS TechnologiesDocument16 pagesImpact of The Source/drain Implants On Threshold Voltage Matching in Deep Sub-Micron CMOS Technologiesdick freebirdNo ratings yet

- For Power Amplification (50V, 3A) : TransistorsDocument2 pagesFor Power Amplification (50V, 3A) : TransistorsGilberto MartínezNo ratings yet

- C5060 RohmDocument4 pagesC5060 RohmletrasaosceusNo ratings yet

- Infineon-PCIM 2019 Combining The Benefits of SiC T-MOSFET and Si IGBT-Editorials-v01 00-ENDocument6 pagesInfineon-PCIM 2019 Combining The Benefits of SiC T-MOSFET and Si IGBT-Editorials-v01 00-ENMV Research & Development TRSNo ratings yet

- ADXL202/ADXL210: F C (X, Y) F CDocument1 pageADXL202/ADXL210: F C (X, Y) F CmhasansharifiNo ratings yet

- MC74VHCT374A Octal D-Type Flip-Flop With 3-State Output: SOIC 20WB Suffix DW CASE 751DDocument7 pagesMC74VHCT374A Octal D-Type Flip-Flop With 3-State Output: SOIC 20WB Suffix DW CASE 751DPanagiotis PanagosNo ratings yet

- MC74VHCT374A Octal D-Type Flip-Flop With 3-State Output: SOIC 20WB Suffix DW CASE 751DDocument7 pagesMC74VHCT374A Octal D-Type Flip-Flop With 3-State Output: SOIC 20WB Suffix DW CASE 751DStuxnetNo ratings yet

- TLP701 Datasheet en 20190925Document8 pagesTLP701 Datasheet en 20190925Max WalkerNo ratings yet

- 2N5849 (SILICON) : NPN Silicon RF Power Transistor RF Power Transistor NPN SiliconDocument4 pages2N5849 (SILICON) : NPN Silicon RF Power Transistor RF Power Transistor NPN SiliconSir Héctor FiordalisoNo ratings yet

- Cu20029ecpb W1JDocument17 pagesCu20029ecpb W1JBeenish MirzaNo ratings yet

- Cascadable Silicon Bipolar MMIC Amplifier: Technical DataDocument4 pagesCascadable Silicon Bipolar MMIC Amplifier: Technical DataAfzal ImamNo ratings yet

- 2SC5858Document6 pages2SC5858LgDvdNo ratings yet

- Silicon Transistor: Data SheetDocument5 pagesSilicon Transistor: Data SheetAbolfazl Yousef ZamanianNo ratings yet

- Tamed Frequency Modulation (TFM) in The IEEE 802.16.1 UplinkDocument22 pagesTamed Frequency Modulation (TFM) in The IEEE 802.16.1 UplinkyedikurniawanNo ratings yet

- Multicomp BD679 DatasheetDocument4 pagesMulticomp BD679 DatasheetJoel Antonio Lopez LopezNo ratings yet

- AIC Project PDFDocument6 pagesAIC Project PDFuam22No ratings yet

- CPV363MF IGBT module delivers 7.65 ARMS per phaseDocument9 pagesCPV363MF IGBT module delivers 7.65 ARMS per phasefolyóirat RádiótechnikaNo ratings yet

- Fdp52N20 / Fdpf52N20T: UnifetDocument10 pagesFdp52N20 / Fdpf52N20T: UnifetJoão de barroNo ratings yet

- Cascadable Silicon Bipolar MMIC Amplifiers: Technical DataDocument4 pagesCascadable Silicon Bipolar MMIC Amplifiers: Technical DataGabriel RacovskyNo ratings yet

- Toshiba - 2SC2705-O (TE6, F, M) - 464345Document6 pagesToshiba - 2SC2705-O (TE6, F, M) - 464345Kirlian KitzingerNo ratings yet

- Value Stream Map For Microsoft Excel Version 1Document8 pagesValue Stream Map For Microsoft Excel Version 1Olaf Perez CastilloNo ratings yet

- Asymmetrical IGBT Design For Three-Level NPC1 Converter in A Bi-Directional Power Conversion SystemDocument7 pagesAsymmetrical IGBT Design For Three-Level NPC1 Converter in A Bi-Directional Power Conversion SystemARINDA DENISENo ratings yet

- Features Description: CMOS Octal Latching Bus DriverDocument7 pagesFeatures Description: CMOS Octal Latching Bus DriverLuciano Benjamín Recalde CarballoNo ratings yet

- 02-10DDocument1 page02-10DzakreaNo ratings yet

- TLP250 Datasheet en 20190617Document7 pagesTLP250 Datasheet en 20190617Zoran ProkicNo ratings yet

- TLP293 4 Datasheet en 20190520-1916320Document13 pagesTLP293 4 Datasheet en 20190520-1916320moacirmenezes51No ratings yet

- Industrial Inverters Inverter For Air Conditioners IGBT/Power MOS FET Gate DriveDocument8 pagesIndustrial Inverters Inverter For Air Conditioners IGBT/Power MOS FET Gate DrivejoeNo ratings yet

- ECEN620: Network Theory - Broadband Circuit Design Lecture 1 IntroductionDocument18 pagesECEN620: Network Theory - Broadband Circuit Design Lecture 1 IntroductionPeygamberinizi SikiyimNo ratings yet

- CPV 364 M 4 KDocument11 pagesCPV 364 M 4 KlalihifiNo ratings yet

- Isolated DC-DC ConverterDocument4 pagesIsolated DC-DC ConverterUge AjjaNo ratings yet

- High-Performance IPD For Battery Chargers MIP2F: × SeriesDocument2 pagesHigh-Performance IPD For Battery Chargers MIP2F: × SeriesWar diyahNo ratings yet

- XF9 (Auxiliary Contact For Nb1, Nbh8, Nb1L, Nb3Le, Nbh8Le) : Standard IEC/EN 60947-5-1Document2 pagesXF9 (Auxiliary Contact For Nb1, Nbh8, Nb1L, Nb3Le, Nbh8Le) : Standard IEC/EN 60947-5-1Cristian MarchisNo ratings yet

- Strobe Flash Applications Audio Power Amplifier ApplicationsDocument4 pagesStrobe Flash Applications Audio Power Amplifier ApplicationsJuan KalinicosNo ratings yet

- High-Voltage Switching Transistor (Camera Strobes and Telephone, Power Supply) ( 400V, 0.1A)Document4 pagesHigh-Voltage Switching Transistor (Camera Strobes and Telephone, Power Supply) ( 400V, 0.1A)Reinaldo OliveiraNo ratings yet

- TLP551 Datasheet en 20190624Document7 pagesTLP551 Datasheet en 20190624jose antonio iglesias infantesNo ratings yet

- BLY89Document12 pagesBLY89sonyscribeNo ratings yet

- NPN Transistors TO-92 Electrical SpecsDocument4 pagesNPN Transistors TO-92 Electrical SpecsagssugaNo ratings yet

- Transistor NPN C945Document4 pagesTransistor NPN C945everton souzaNo ratings yet

- C945 PDFDocument4 pagesC945 PDFHenrique Ferreira GonferNo ratings yet

- PSCAD Essential Tutorials - Getting Started and Basic FeaturesDocument5 pagesPSCAD Essential Tutorials - Getting Started and Basic FeaturesGabriel Vinicios Moreira FernandesNo ratings yet

- 2450LP15B050Document2 pages2450LP15B050Venkatesh ANo ratings yet

- 2SC4793 PDFDocument3 pages2SC4793 PDFSyaiful RahmanNo ratings yet

- Slua 158Document4 pagesSlua 158Hossein DavijaniNo ratings yet

- Code - Aster: TPLS102 - Thick Beam in Plane Constraints - Linear Temperature Variation According To The WidthDocument8 pagesCode - Aster: TPLS102 - Thick Beam in Plane Constraints - Linear Temperature Variation According To The WidthStefano MilaniNo ratings yet

- Code - Aster: TTNL302 - Infinite Wall Subjected To A Constant Flow With Variable PropertiesDocument14 pagesCode - Aster: TTNL302 - Infinite Wall Subjected To A Constant Flow With Variable PropertiesStefano MilaniNo ratings yet

- EE290C - Spring 2011 Reference Jitter TF: Lecture 12: Timing: Noise and JitterDocument3 pagesEE290C - Spring 2011 Reference Jitter TF: Lecture 12: Timing: Noise and JitterFahmida Pervin BrishtyNo ratings yet

- Lecture11 PLL DLL Components 6upDocument3 pagesLecture11 PLL DLL Components 6upFahmida Pervin BrishtyNo ratings yet

- EE290C - Spring 2011 A Warning : Lecture 10: Timing: PLL/DLL BasicsDocument2 pagesEE290C - Spring 2011 A Warning : Lecture 10: Timing: PLL/DLL BasicsFahmida Pervin BrishtyNo ratings yet

- Lecture11 PLL DLL Components 6upDocument3 pagesLecture11 PLL DLL Components 6upFahmida Pervin BrishtyNo ratings yet

- EE290C - Spring 2011 A Warning : Lecture 10: Timing: PLL/DLL BasicsDocument2 pagesEE290C - Spring 2011 A Warning : Lecture 10: Timing: PLL/DLL BasicsFahmida Pervin BrishtyNo ratings yet

- Lecture06 Perf Analysis 6upDocument5 pagesLecture06 Perf Analysis 6upFahmida Pervin BrishtyNo ratings yet

- EE290C - Spring 2011: - Several Issues To Watch Out ForDocument2 pagesEE290C - Spring 2011: - Several Issues To Watch Out ForFahmida Pervin BrishtyNo ratings yet

- Why ISI MattersDocument5 pagesWhy ISI MattersFahmida Pervin BrishtyNo ratings yet

- EE290C - Spring 2011 CTLE Adaptation Block DiagramDocument3 pagesEE290C - Spring 2011 CTLE Adaptation Block DiagramFahmida Pervin BrishtyNo ratings yet

- Lecture03 Basic TX RX 6upDocument6 pagesLecture03 Basic TX RX 6upFahmida Pervin BrishtyNo ratings yet

- Lecture02 Link Over Environ 6upDocument5 pagesLecture02 Link Over Environ 6upFahmida Pervin BrishtyNo ratings yet

- EE290C - Spring 2011 Course Prerequisites: High-Speed Electrical Interface Circuit Design Lecture 1: IntroductionDocument4 pagesEE290C - Spring 2011 Course Prerequisites: High-Speed Electrical Interface Circuit Design Lecture 1: IntroductionFahmida Pervin BrishtyNo ratings yet

- Lecture04 Timing Basics 6upDocument4 pagesLecture04 Timing Basics 6upFahmida Pervin BrishtyNo ratings yet

- Why ISI MattersDocument5 pagesWhy ISI MattersFahmida Pervin BrishtyNo ratings yet

- Solutions and Stoichiometry Worksheet (Sept, 17, 2021)Document2 pagesSolutions and Stoichiometry Worksheet (Sept, 17, 2021)Ahmed AlmossaweNo ratings yet

- Huzaifa Majeed (Fa18-Bee-025) Assignment 4Document4 pagesHuzaifa Majeed (Fa18-Bee-025) Assignment 4Israr Ul HassanNo ratings yet

- Jadual Waktu SPM 2010Document2 pagesJadual Waktu SPM 2010sallehGNo ratings yet

- Metaphors in Kapampangan: Mike Pangilinan and Hiroaki KitanoDocument7 pagesMetaphors in Kapampangan: Mike Pangilinan and Hiroaki KitanoThe DigilakansNo ratings yet

- Lesson 3 Erikson Introduction To The Erik Erikson's Stage Theory of DevelopmentDocument7 pagesLesson 3 Erikson Introduction To The Erik Erikson's Stage Theory of DevelopmentRein Pama SorianoNo ratings yet

- Thematic Teaching in Basic EducationDocument13 pagesThematic Teaching in Basic EducationCyryhl Gutlay100% (1)

- Elements of Arts Lesson PlanDocument9 pagesElements of Arts Lesson PlanMicahCastro100% (3)

- Ad 304Document1 pageAd 304srinimehaNo ratings yet

- Understanding Schmitt TriggersDocument4 pagesUnderstanding Schmitt TriggersfernandofortunaNo ratings yet

- SWOT Analysis PaperDocument10 pagesSWOT Analysis Paperrushilmanchanda07No ratings yet

- LS Lpli SMS El V1.8Document2 pagesLS Lpli SMS El V1.8adelgcNo ratings yet

- Cec 208 Lecture Notes 1Document9 pagesCec 208 Lecture Notes 1Zaid Habibu100% (1)

- Planning Commentary OfficialDocument7 pagesPlanning Commentary Officialapi-550981792No ratings yet

- Experimental Study of Ammonia Removal From Water by Modified Direct Contact Membrane DistillationDocument6 pagesExperimental Study of Ammonia Removal From Water by Modified Direct Contact Membrane DistillationlixiaoluhjNo ratings yet

- Checklist For Welding and NDE SectionDocument2 pagesChecklist For Welding and NDE SectionMuhammadShabbirNo ratings yet

- GRADE:10: Page 1 of 13Document13 pagesGRADE:10: Page 1 of 13Pujan PatelNo ratings yet

- SPM List of Physics ExperimentsDocument3 pagesSPM List of Physics ExperimentsAnythingAlsoCanLah57% (7)

- Norman Steenrod and William G. Chinn - First Concepts of Topology: The Geometry of Mappings of Segments, Curves, Circles, and DisksDocument170 pagesNorman Steenrod and William G. Chinn - First Concepts of Topology: The Geometry of Mappings of Segments, Curves, Circles, and DisksMi LiaNo ratings yet

- CSE2005 Lab Assessment-2: OS Process and Thread ManagementDocument29 pagesCSE2005 Lab Assessment-2: OS Process and Thread ManagementTanumay GoswamiNo ratings yet

- A Detailed Lesson Plan in EDUC 6ADocument10 pagesA Detailed Lesson Plan in EDUC 6ARyan Jay Gaviola CalahatNo ratings yet

- Fs1 Complete Learning Episodes 1Document126 pagesFs1 Complete Learning Episodes 1REDELYN M. CANCINONo ratings yet

- Effects of Kahramanmaras Earthquakes in South of Turkey On Livestock ActivitiesDocument10 pagesEffects of Kahramanmaras Earthquakes in South of Turkey On Livestock ActivitiesIJAR JOURNALNo ratings yet

- ThermodynamicasDocument21 pagesThermodynamicasTom Psy100% (1)

- Caracteristicas Del Conocimiento Cientifico CreencDocument20 pagesCaracteristicas Del Conocimiento Cientifico CreencLiana PichardoNo ratings yet

- How to Write a Resume for a Job ApplicationDocument4 pagesHow to Write a Resume for a Job ApplicationPhuong Dang AnhNo ratings yet

- Westergaard Method For Rigid PavementDocument18 pagesWestergaard Method For Rigid PavementAnonymous MklNL77No ratings yet

- Module 3 - Regression and Correlation Analysis SummaryDocument54 pagesModule 3 - Regression and Correlation Analysis SummaryAirra Mhae IlaganNo ratings yet

- Syllabus of Eeb162Document2 pagesSyllabus of Eeb162Dr. Tirupathiraju KanumuriNo ratings yet

- System Dynamics IntroductionDocument8 pagesSystem Dynamics IntroductionDavid Abraham Jiménez MartínezNo ratings yet

- Thermal Expansion of Iridium at High TemperaturesDocument5 pagesThermal Expansion of Iridium at High TemperaturesAntonio CamaranoNo ratings yet