Professional Documents

Culture Documents

Lecture03 Basic TX RX 6up

Uploaded by

Fahmida Pervin BrishtyOriginal Description:

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Lecture03 Basic TX RX 6up

Uploaded by

Fahmida Pervin BrishtyCopyright:

Available Formats

Administrative

EE290C – Spring 2011 • Elad will be out of town this Thurs.

• Make-up lecture will be held on Mon. 1-31 1:30-3:00pm

in 127 Dwinelle

Lecture 3: Basic Transmitters and Receivers • Office hours on Thurs. cancelled – available over

Elad Alon

Dept. of EECS

EE290C Lecture 3 2

Plain Old Inverters – Why Not? Outline

• Signaling Basics • RX Circuit Design

• Single-ended vs. differential • Comparator review

• “Current-mode” vs. • Deserialization

“Voltage-mode” signaling options

• Termination

• TX Circuit Design

• Z control

• CML, VM drivers

• Power vs. swing

• Serialization options

EE290C Lecture 3 3 EE290C Lecture 3 4

Single-Ended Signaling So Why Even Mention This?

rcvr

din xmtr

ref dout

Cd Cr

• RX: comparing against a shared reference

• Reference may be implicit (i.e., ground/supply)

• Mismatch between shared and individual lines

• TX: generates large variations on power supply

• SSO – simultaneous switching outputs

• No XTALK immunity

EE290C Lecture 3 5 EE290C Lecture 3 6

Classic Debate “Voltage-Mode” vs. ”Current-Mode”

• “Differential must be twice as fast as single-

ended in order to win”

• Reality more complicated

• E.g., power supply to signaling pin ratio higher in S.E.

• Short “answer” • Transmission line has both voltage and current…

• Differential a lot easier to build and get right the first • Terminology unfortunately heavily overloaded

time

• Whether or not Zo of driver is high

• Can make S.E. work – but often a lot more painful

• How Zo of driver is set

• What sets output swing

EE290C Lecture 3 7 EE290C Lecture 3 8

“Voltage-Mode” vs. ”Current-Mode” Another View

“Low Impedance” “High Impedance”

VS

Ended

Single

- +

d

VS/2 ref -

shared

Differential

+ -

- d

d

• RX opposite of TX

• Signal integrity implications?

EE290C Lecture 3 9 EE290C Lecture 3 10

Why Terminate? External vs. Internal Termination

• Internal: makes package L, pad C part of T-line

• External: chip/package become a stub

• If want on-die term need to control its value…

EE290C Lecture 3 11 EE290C Lecture 3 12

Untrimmed Poly Termination Ri, Ci, and Pad Complexity

1.00

Rs L

• Main issue is variation: +/-20% at one temperature 0.80

Normalized amplitude

LI

• But Gd C 0.60

CI

• It’s relatively linear RI

0.40

"low_CL"

• ESD robust 0.20 "1_drop"

"2_drop"

"4_drop"

• Low parasitics…

"8_drop"

Ci, Ri 0.00

1e+008 1e+009

typically dominate Freq (Hz)

• LPF at pad can dominate overall channel

• Example: 500fF ESD, 500fF driver, 500fF wire

• Bandwidth ~4GHz with double-terminated link

• Even worse in busses (or if add big series R)…

EE290C Lecture 3 13 EE290C Lecture 3 14

Active Terminations AC vs. DC Termination

• With diff. can terminate to

complement

• High Z Æ lower power RAC Rx

• See more shortly

• TX sets common-mode VCM

• Can be inconvenient RCM

• May need wide CM range

RAC Rx

• AC-coupled + AC-term

• Places some requirements on RCM

data though VCM

EE290C Lecture 3 15 EE290C Lecture 3 16

TX Design: Series vs. Parallel Termination Alphabet Soup

• LVDS, CML

• GTL, GTL+, RSL, …

• VM, CM

• HCM, LCM

• All same basic principles

• Look at two representative circuits to understand

some of the more fundamental tradeoffs

EE290C Lecture 3 17 EE290C Lecture 3 18

CML TX + RX Term Side Note: Pre-Driver

VD D VDD

50Ω 50Ω

Zo = 50Ω

Tx Rx

Zo = 50Ω

Io = - 21m A

Dou ble-term inated

on-ch ip

EE290C Lecture 3 19 EE290C Lecture 3 20

CML Power Consumption Differential VM TX + RX

• Main motivation: can reduce power for same

swing/supply

EE290C Lecture 3 21 EE290C Lecture 3 22

Simplified Model And Power Bad News: Extra Complexity

• Driver impedance (termination) now set totally

by devices

• Some sort of impedance control is critical

• “High-swing” driver:

EE290C Lecture 3 23 EE290C Lecture 3 24

Low-Swing VM Driver Impedance Control

• Old standards often required large swings

(>1V diff. p2p)

• More modern designs use much lower swings

(~200-400mV diff. p2p) to save power

• Low-swing VM driver:

EE290C Lecture 3 25 EE290C Lecture 3 26

Another Approach Serialization: Input vs. Output

• On-chip clocks often slower than off-chip data-

rates

• Need to take a set of parallel on-chip data and serialize it

• Can serialize either at input of TX or at final output

EE290C Lecture 3 27 EE290C Lecture 3 28

Serialization: Input vs. Output Basic TX Final Notes

• Input ser. requires on-chip circuitry to run at full • Usually need many peripheral controls

line rate • Zo, edge-rate, etc.

• May lead to high power consumption

• In older technologies (0.35um) was hard to support high-

freq. clocks • Keep tuning out of the high-speed signal path

D0 D1 D2 • P(High-speed, low res. + low-speed, high-res.) <<

• Output ser. noved burden data(ck0) P(high-speed, high-res.)

clock(ck3)

at pad RTERM

• At the time was highest BW RTERM out_b

ck3 out

• Limit in both designs: edge rate x8

• Either for the clock or for the data

d0 d0

EE290C Lecture 3 29 EE290C Lecture 3 30

Basic TX Final Notes Basic RX

• Lots of research focused on reduced signaling • Simplest: RX is just a comparator @ fbit

power • (Clocking later)

• I.e., power spent by actual final driver

• Key things to watch out for:

• Watch out for “overhead” (pre-drivers) • High sensitivity (low noise, low offset/hysteresis)

• Especially with emerging low-swing designs, • Common-mode input range

overhead can actually dominate • Supply/common-mode rejection

• Psig (400mV diff. p2p): • Max. clock rate

• Pdigital (100 min. sized inverters @ 10GHz): • Power consumption

EE290C Lecture 3 31 EE290C Lecture 3 32

Typical Design StrongArm Review

EE290C Lecture 3 33 EE290C Lecture 3 34

Higher Speeds

EE290C Lecture 3 35

You might also like

- 09 DIRA Software - Administrator's Guide - InstallationDocument16 pages09 DIRA Software - Administrator's Guide - InstallationwellsuNo ratings yet

- Cyber Security Small Business Guide (NCSC)Document16 pagesCyber Security Small Business Guide (NCSC)ivanpmnNo ratings yet

- Power Transformer Fundamentals: Design and ManufacturingDocument52 pagesPower Transformer Fundamentals: Design and Manufacturingjuliancansen100% (1)

- Moshell For Msrbs Du&BbDocument394 pagesMoshell For Msrbs Du&BbAnonymous XZnkpMec100% (2)

- ACVG TheoryDocument49 pagesACVG TheorynuvanNo ratings yet

- Signal Integrity:: Applied Electromagnetics and Professional PracticeDocument16 pagesSignal Integrity:: Applied Electromagnetics and Professional PracticeKashif HassanNo ratings yet

- 457 Opamp 1 424Document28 pages457 Opamp 1 424v4vktryNo ratings yet

- Nmos Inverter: Resistive LoadDocument9 pagesNmos Inverter: Resistive LoadVidhya DsNo ratings yet

- New ECE 4101Document81 pagesNew ECE 4101Joy MeNo ratings yet

- EMI and Layout FundamentalsDocument38 pagesEMI and Layout Fundamentalsapi-3719969100% (1)

- Buck - Converters For Portable ApplicationDocument70 pagesBuck - Converters For Portable ApplicationanandNo ratings yet

- Ders - 05 - Transformers2 26 04 2013 16 15 29 2335744815 PDFDocument14 pagesDers - 05 - Transformers2 26 04 2013 16 15 29 2335744815 PDFBUĞRA UYĞURNo ratings yet

- Introduction To Hall Effect Position SensingDocument11 pagesIntroduction To Hall Effect Position SensingJose Ramón Orenes ClementeNo ratings yet

- Power Semiconductor DiodesDocument22 pagesPower Semiconductor Diodesazkasheikh19No ratings yet

- PE Chap 5. DCDC ConverterDocument87 pagesPE Chap 5. DCDC ConverterThành Trần BáNo ratings yet

- Basics of Electrical SwitchesDocument3 pagesBasics of Electrical SwitchesHsein WangNo ratings yet

- EE103 Lecture14 BGF 30 Dec 2022 Mod3 UploadDocument12 pagesEE103 Lecture14 BGF 30 Dec 2022 Mod3 UploadRaunak MukherjeeNo ratings yet

- Penta Lite Elliptical CC: Narrow Beam Module For Edge Lighting Sign BoxDocument2 pagesPenta Lite Elliptical CC: Narrow Beam Module For Edge Lighting Sign BoxDhykaAndhykaNo ratings yet

- Analyze Transistor Biasing Circuits - Load Lines (FET - MOSFET)Document19 pagesAnalyze Transistor Biasing Circuits - Load Lines (FET - MOSFET)KishenNo ratings yet

- Chap1c - BJT Small Signal Modelling (v1.2)Document65 pagesChap1c - BJT Small Signal Modelling (v1.2)Al AidenNo ratings yet

- Avi 5Document11 pagesAvi 5santosh07591A2128No ratings yet

- Electrical Diagrams - InstructionsDocument15 pagesElectrical Diagrams - InstructionsFrancisco Meza GonzalezNo ratings yet

- Power Electronics Power Electronics: Course: BookDocument16 pagesPower Electronics Power Electronics: Course: BooksufiiiiyanNo ratings yet

- Lecture 9-13 - DCDCDocument74 pagesLecture 9-13 - DCDCĐạt Nguyễn XuânNo ratings yet

- EPC2059 - Enhancement Mode Power Transistor: V, 170 V R, 9 mΩ I, 24 ADocument6 pagesEPC2059 - Enhancement Mode Power Transistor: V, 170 V R, 9 mΩ I, 24 AЕвгений ИвановNo ratings yet

- PV & PV-hybrid Design, VT 2021: Advanced Inverter TechnologiesDocument43 pagesPV & PV-hybrid Design, VT 2021: Advanced Inverter TechnologiesPablo Omar Luz PedemonteNo ratings yet

- MD5-HD14-2X 3X en Tcd210126ad 20230116 Inst WDocument1 pageMD5-HD14-2X 3X en Tcd210126ad 20230116 Inst WKun nNo ratings yet

- High Voltage Gain Buck-Boost DC-DC Converter Based On Three-State Switching Cell AnnotatedDocument8 pagesHigh Voltage Gain Buck-Boost DC-DC Converter Based On Three-State Switching Cell AnnotatedIgor hammomNo ratings yet

- FDD5N50Document8 pagesFDD5N50primero marnezNo ratings yet

- 03 Ece621 F17 TXDocument58 pages03 Ece621 F17 TXAhmed MaGdyNo ratings yet

- Eele461 Module 07Document8 pagesEele461 Module 07zhiqian wangNo ratings yet

- DatasheetDocument4 pagesDatasheetSaikumarNo ratings yet

- Managing LVDS InterfacesDocument11 pagesManaging LVDS InterfacesLgjiiNo ratings yet

- EECS 151/251A Fall 2017 Digital Design and Integrated CircuitsDocument45 pagesEECS 151/251A Fall 2017 Digital Design and Integrated CircuitsindranilhNo ratings yet

- FQP6N50C: 500V N-Channel MOSFETDocument8 pagesFQP6N50C: 500V N-Channel MOSFETHenry ToroNo ratings yet

- Type TA Class 10: Thermal Overload RelaysDocument18 pagesType TA Class 10: Thermal Overload RelaysKwong Hwo TiangNo ratings yet

- Bien Doi DC-DC Ly ThuyetDocument82 pagesBien Doi DC-DC Ly ThuyetCỏ DươngNo ratings yet

- Syllabus Transformers (EE 1000) : DC MachinesDocument14 pagesSyllabus Transformers (EE 1000) : DC MachinesKuroko TetsuyaNo ratings yet

- System ModelingDocument64 pagesSystem ModelingShuvo ShahedNo ratings yet

- Voltage Source Parallel Resonant Class E InverterDocument10 pagesVoltage Source Parallel Resonant Class E InverterHari Krishnan k kNo ratings yet

- Unr 3.3-8 D5Document4 pagesUnr 3.3-8 D5Cheng Yi TsaiNo ratings yet

- The Topics That We Will Covered in This Class Is:: - Earthing Switch OperationDocument6 pagesThe Topics That We Will Covered in This Class Is:: - Earthing Switch OperationMd. RakibNo ratings yet

- Edc 3 Field Effect TransistorDocument8 pagesEdc 3 Field Effect Transistorsherwincalma189No ratings yet

- 02 - Sect 7 5 The Canonical Model - Sect7 5Document14 pages02 - Sect 7 5 The Canonical Model - Sect7 5Ananatha KarthikNo ratings yet

- Chapter 1 IntroductionDocument18 pagesChapter 1 IntroductionCửu Nguyễn ViếtNo ratings yet

- Transistor ModellingDocument48 pagesTransistor Modellingkathreen mae fabianaNo ratings yet

- Power Electronics Power Electronics: Course: BookDocument19 pagesPower Electronics Power Electronics: Course: BooksufiiiiyanNo ratings yet

- Datasheet FDP7N50Document10 pagesDatasheet FDP7N50Anonymous fAL3CNtUiNo ratings yet

- Labs Will Start at 2:30 PM Every Tuesday: EE210 Slide 1Document10 pagesLabs Will Start at 2:30 PM Every Tuesday: EE210 Slide 1Sallie JohnsonNo ratings yet

- AlksfasdfDocument8 pagesAlksfasdfdlsgdf fgpohfNo ratings yet

- Magna: BUZ900 BUZ901Document4 pagesMagna: BUZ900 BUZ901rory957No ratings yet

- 1.1 Introduction To Power Processing!Document16 pages1.1 Introduction To Power Processing!Jahangeer SoomroNo ratings yet

- 2.transistor ModellingDocument31 pages2.transistor ModellingRohit KumarNo ratings yet

- 2 - Analog Signal ProcessingDocument22 pages2 - Analog Signal ProcessingTuanHungNo ratings yet

- TC6215 N-And P-Channel Enhancement-Mode Dual MOSFET: Features General DescriptionDocument5 pagesTC6215 N-And P-Channel Enhancement-Mode Dual MOSFET: Features General DescriptionfelipekillerNo ratings yet

- Fuji Power Mos-Fet Julio 25 Del 2022 01Document11 pagesFuji Power Mos-Fet Julio 25 Del 2022 01HENRY MEZANo ratings yet

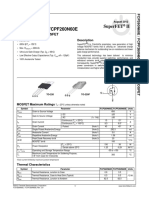

- Superfet Ii Fcp260N60E / Fcpf260N60E: 600V N-Channel MosfetDocument10 pagesSuperfet Ii Fcp260N60E / Fcpf260N60E: 600V N-Channel MosfetAlexandros BobNo ratings yet

- Datasheet MOSFET - 2N7000 - Supertex IIIDocument6 pagesDatasheet MOSFET - 2N7000 - Supertex IIICristian Daniel BerettaNo ratings yet

- MJD340 (NPN), MJD350 (PNP) High Voltage Power Transistors: DPAK For Surface Mount ApplicationsDocument8 pagesMJD340 (NPN), MJD350 (PNP) High Voltage Power Transistors: DPAK For Surface Mount Applicationshalil ibrahim soysalNo ratings yet

- Module-I Power Semiconductor Devices: Prepared by Jeena John Asst. Prof. in Eee Soe, CusatDocument50 pagesModule-I Power Semiconductor Devices: Prepared by Jeena John Asst. Prof. in Eee Soe, CusatJEENA JOHNNo ratings yet

- Ob 2223 HCDocument11 pagesOb 2223 HCRivaldyNo ratings yet

- 6.Opamp-ParametersDocument21 pages6.Opamp-ParametersGiáp TrầnNo ratings yet

- EE290C - Spring 2011 A Warning : Lecture 10: Timing: PLL/DLL BasicsDocument2 pagesEE290C - Spring 2011 A Warning : Lecture 10: Timing: PLL/DLL BasicsFahmida Pervin BrishtyNo ratings yet

- EE290C - Spring 2011 RX FIR Equalizers: - Currently Not Very Popular - Why?Document4 pagesEE290C - Spring 2011 RX FIR Equalizers: - Currently Not Very Popular - Why?Fahmida Pervin BrishtyNo ratings yet

- Lecture06 Perf Analysis 6upDocument5 pagesLecture06 Perf Analysis 6upFahmida Pervin BrishtyNo ratings yet

- EE290C - Spring 2011 CTLE Adaptation Block DiagramDocument3 pagesEE290C - Spring 2011 CTLE Adaptation Block DiagramFahmida Pervin BrishtyNo ratings yet

- Lecture05 Equalization Tech 6upDocument5 pagesLecture05 Equalization Tech 6upFahmida Pervin BrishtyNo ratings yet

- EE290C - Spring 2011: - Several Issues To Watch Out ForDocument2 pagesEE290C - Spring 2011: - Several Issues To Watch Out ForFahmida Pervin BrishtyNo ratings yet

- EE290C - Spring 2011 Course Prerequisites: High-Speed Electrical Interface Circuit Design Lecture 1: IntroductionDocument4 pagesEE290C - Spring 2011 Course Prerequisites: High-Speed Electrical Interface Circuit Design Lecture 1: IntroductionFahmida Pervin BrishtyNo ratings yet

- Lecture04 Timing Basics 6upDocument4 pagesLecture04 Timing Basics 6upFahmida Pervin BrishtyNo ratings yet

- Oracle Database Appliance Help Desk Support Consultant - Online AssessmentDocument35 pagesOracle Database Appliance Help Desk Support Consultant - Online AssessmentashisNo ratings yet

- System ArchitectureDocument34 pagesSystem ArchitecturesumanNo ratings yet

- Brooklyn DAC+ ManualDocument24 pagesBrooklyn DAC+ ManualAndrew BryantNo ratings yet

- 330 0218 R15.0Document10 pages330 0218 R15.0mch79No ratings yet

- Intensi-Fi™: Draft-802.11N Product FamilyDocument2 pagesIntensi-Fi™: Draft-802.11N Product FamilyGuilherme Ribeiro BarbosaNo ratings yet

- Competitive Programming RoadmapDocument6 pagesCompetitive Programming RoadmapVikash YadavNo ratings yet

- Final ProjectDocument26 pagesFinal ProjectMuhammad Shahzaib SamiNo ratings yet

- Lenovo Ih81mDocument36 pagesLenovo Ih81mVikings of KarnatakaNo ratings yet

- Dell Emc Poweredge R750: General Purpose Server Optimized To Address The Most Demanding WorkloadsDocument3 pagesDell Emc Poweredge R750: General Purpose Server Optimized To Address The Most Demanding Workloadsit4728No ratings yet

- Reanibex 300 - Presentacion 2013Document17 pagesReanibex 300 - Presentacion 2013Josiel MarlosNo ratings yet

- Chromebook User GuideDocument1 pageChromebook User GuideПолина МиховаNo ratings yet

- Fall Semester 2021-22 CSE1007 - Java Programming Lab Practice Problems On Threads and ExceptionsDocument2 pagesFall Semester 2021-22 CSE1007 - Java Programming Lab Practice Problems On Threads and ExceptionsPalanisamy VNo ratings yet

- Lab4 Djm30073-Ring CountersDocument4 pagesLab4 Djm30073-Ring CountersSyakir AiemanNo ratings yet

- Stenographer and Secretarial Assistant - Semester 1 Module 1 - Fundamentals of Shorthand and Computer HardwareDocument27 pagesStenographer and Secretarial Assistant - Semester 1 Module 1 - Fundamentals of Shorthand and Computer Hardwarevhenzhar saycoNo ratings yet

- Usecase DiagramDocument4 pagesUsecase Diagramharibabu madaNo ratings yet

- You Tube Video CatalogDocument27 pagesYou Tube Video CatalogUma SankarNo ratings yet

- Schneider - Ch16 - Inv To CS 8eDocument33 pagesSchneider - Ch16 - Inv To CS 8ePaulo SantosNo ratings yet

- Lesson 2: Online Safety, Security and Rules of Netiquette: ObjectivesDocument3 pagesLesson 2: Online Safety, Security and Rules of Netiquette: ObjectivesEissa May VillanuevaNo ratings yet

- CS506 MIDTERM SOLVED MCQS by JUNAIDDocument51 pagesCS506 MIDTERM SOLVED MCQS by JUNAIDabbas abbas khanNo ratings yet

- The Internet Quiz With AnswersDocument2 pagesThe Internet Quiz With Answersrex sedenoNo ratings yet

- Cream Cascade For G8M Dickator: UtorialDocument3 pagesCream Cascade For G8M Dickator: UtorialAuroraNo ratings yet

- Thesis Tungkol Sa KompyuterDocument7 pagesThesis Tungkol Sa KompyuterCarmen Pell100% (2)

- NinguDocument20 pagesNinguAsif BadegharNo ratings yet

- Sub-Nyquist Sampling For TDR Sensors:: Finite Rate of Innovation With Dithering Marc Ihle, Hochschule Karlsruhe, GermanyDocument21 pagesSub-Nyquist Sampling For TDR Sensors:: Finite Rate of Innovation With Dithering Marc Ihle, Hochschule Karlsruhe, GermanyFFSeriesvnNo ratings yet

- Install Sentinel CLI - Getting Started - Sentinel by HashiCorpDocument3 pagesInstall Sentinel CLI - Getting Started - Sentinel by HashiCorpRajeev GhoshNo ratings yet

- Graded Quiz Unit 3 - Attempt Review3Document14 pagesGraded Quiz Unit 3 - Attempt Review3TeoDoe MusicNo ratings yet

- Scorpion: Jendrik SeippDocument3 pagesScorpion: Jendrik SeippHarold Andrés Castañeda CastroNo ratings yet