Professional Documents

Culture Documents

N-Channel Trenchmos Transistor Irf530N: Features Symbol Quick Reference Data

Uploaded by

Willams SantosOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

N-Channel Trenchmos Transistor Irf530N: Features Symbol Quick Reference Data

Uploaded by

Willams SantosCopyright:

Available Formats

Philips Semiconductors Product specification

N-channel TrenchMOS transistor IRF530N

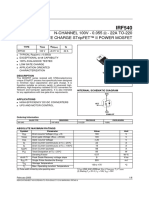

FEATURES SYMBOL QUICK REFERENCE DATA

• ’Trench’ technology d

• Low on-state resistance VDSS = 100 V

• Fast switching

• Low thermal resistance ID = 17 A

g

RDS(ON) ≤ 110 mΩ

s

GENERAL DESCRIPTION PINNING SOT78 (TO220AB)

N-channel enhancement mode PIN DESCRIPTION

tab

field-effect power transistor in a drain

plastic envelope using ’trench’ 1 gate

technology.

2 drain

Applications:-

• d.c. to d.c. converters 3 source

• switched mode power supplies 1 2 3

gate source

tab drain drain

The IRF530N is supplied in the

SOT78 (TO220AB) conventional

leaded package.

LIMITING VALUES

Limiting values in accordance with the Absolute Maximum System (IEC 134)

SYMBOL PARAMETER CONDITIONS MIN. MAX. UNIT

VDSS Drain-source voltage Tj = 25 ˚C to 175˚C - 100 V

VDGR Drain-gate voltage Tj = 25 ˚C to 175˚C; RGS = 20 kΩ - 100 V

VGS Gate-source voltage - ± 20 V

ID Continuous drain current Tmb = 25 ˚C; VGS = 10 V - 17 A

Tmb = 100 ˚C; VGS = 10 V - 12 A

IDM Pulsed drain current Tmb = 25 ˚C - 68 A

PD Total power dissipation Tmb = 25 ˚C - 79 W

Tj, Tstg Operating junction and - 55 175 ˚C

storage temperature

AVALANCHE ENERGY LIMITING VALUES

Limiting values in accordance with the Absolute Maximum System (IEC 134)

SYMBOL PARAMETER CONDITIONS MIN. MAX. UNIT

EAS Non-repetitive avalanche Unclamped inductive load, IAS = 7.8 A; - 150 mJ

energy tp = 300 µs; Tj prior to avalanche = 25˚C;

VDD ≤ 25 V; RGS = 50 Ω; VGS = 10 V; refer

to fig:14

IAS Peak non-repetitive - 17 A

avalanche current

August 1999 1 Rev 1.100

Philips Semiconductors Product specification

N-channel TrenchMOS transistor IRF530N

THERMAL RESISTANCES

SYMBOL PARAMETER CONDITIONS MIN. TYP. MAX. UNIT

Rth j-mb Thermal resistance junction - - 1.9 K/W

to mounting base

Rth j-a Thermal resistance junction SOT78 package, in free air - 60 - K/W

to ambient

ELECTRICAL CHARACTERISTICS

Tj= 25˚C unless otherwise specified

SYMBOL PARAMETER CONDITIONS MIN. TYP. MAX. UNIT

V(BR)DSS Drain-source breakdown VGS = 0 V; ID = 0.25 mA; 100 - - V

voltage Tj = -55˚C 89 - - V

VGS(TO) Gate threshold voltage VDS = VGS; ID = 1 mA 2 3 4 V

Tj = 175˚C 1 - - V

Tj = -55˚C - 6 V

RDS(ON) Drain-source on-state VGS = 10 V; ID = 9 A - 80 110 mΩ

resistance Tj = 175˚C - - 275 mΩ

gfs Forward transconductance VDS = 25 V; ID = 9 A 6.4 11 - S

IGSS Gate source leakage current VGS = ± 20 V; VDS = 0 V - 10 100 nA

IDSS Zero gate voltage drain VDS = 100 V; VGS = 0 V - 0.05 10 µA

current VDS = 80 V; VGS = 0 V; Tj = 175˚C - - 250 µA

Qg(tot) Total gate charge ID = 9 A; VDD = 80 V; VGS = 10 V - - 40 nC

Qgs Gate-source charge - - 5.6 nC

Qgd Gate-drain (Miller) charge - - 19 nC

td on Turn-on delay time VDD = 50 V; RD = 2.7 Ω; - 6 - ns

tr Turn-on rise time VGS = 10 V; RG = 5.6 Ω - 36 - ns

td off Turn-off delay time Resistive load - 18 - ns

tf Turn-off fall time - 12 - ns

Ld Internal drain inductance Measured tab to centre of die - 3.5 - nH

Ld Internal drain inductance Measured from drain lead to centre of die - 4.5 - nH

(SOT78 package only)

Ls Internal source inductance Measured from source lead to source - 7.5 - nH

bond pad

Ciss Input capacitance VGS = 0 V; VDS = 25 V; f = 1 MHz - 633 - pF

Coss Output capacitance - 103 - pF

Crss Feedback capacitance - 61 - pF

REVERSE DIODE LIMITING VALUES AND CHARACTERISTICS

Tj = 25˚C unless otherwise specified

SYMBOL PARAMETER CONDITIONS MIN. TYP. MAX. UNIT

IS Continuous source current - - 17 A

(body diode)

ISM Pulsed source current (body - - 68 A

diode)

VSD Diode forward voltage IF = 17 A; VGS = 0 V - 0.92 1.2 V

trr Reverse recovery time IF = 17 A; -dIF/dt = 100 A/µs; - 55 - ns

Qrr Reverse recovery charge VGS = 0 V; VR = 25 V - 135 - nC

August 1999 2 Rev 1.100

Philips Semiconductors Product specification

N-channel TrenchMOS transistor IRF530N

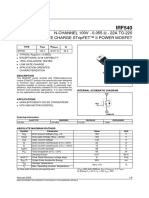

Normalised Power Derating, PD (%) Transient thermal impedance, Zth j-mb (K/W)

10

100

90

80

D = 0.5

70 1

0.2

60

50 0.1

0.05

40 P D = tp/T

0.1 D tp

30 0.02

20 single pulse

T

10

0.01

0

1E-06 1E-05 1E-04 1E-03 1E-02 1E-01 1E+00

0 25 50 75 100 125 150 175

Mounting Base temperature, Tmb (C) Pulse width, tp (s)

Fig.1. Normalised power dissipation. Fig.4. Transient thermal impedance.

PD% = 100⋅PD/PD 25 ˚C = f(Tmb) Zth j-mb = f(t); parameter D = tp/T

Drain Current, ID (A)

Normalised Current Derating, ID (%) 20

100 VGS = 10V 8V

18

90 Tj = 25 C

16 6V

80

14

70

12

60

50 10

5.4 V

40 8

5.2 V

30 6

20 5V

4

10 4.8 V

2 4.6 V

0 4.4 V

0

0 25 50 75 100 125 150 175

0 0.2 0.4 0.6 0.8 1 1.2 1.4 1.6 1.8 2

Mounting Base temperature, Tmb (C) Drain-Source Voltage, VDS (V)

Fig.2. Normalised continuous drain current. Fig.5. Typical output characteristics, Tj = 25 ˚C.

ID% = 100⋅ID/ID 25 ˚C = f(Tmb); conditions: VGS ≥ 10 V ID = f(VDS)

Peak Pulsed Drain Current, IDM (A)

100 Drain-Source On Resistance, RDS(on) (Ohms)

0.2

RDS(on) = VDS/ ID 4.8V 5.2 V Tj = 25 C

0.18 4.6V 5V 5.4 V

tp = 10 us 0.16

10 0.14 6V

100 us

0.12

D.C. 0.1

1 ms

10 ms 0.08 8V

1

100 ms 0.06 VGS = 10V

0.04

0.02

0.1 0

1 10 100 1000 0 2 4 6 8 10 12 14 16 18 20

Drain-Source Voltage, VDS (V) Drain Current, ID (A)

Fig.3. Safe operating area. Tmb = 25 ˚C Fig.6. Typical on-state resistance, Tj = 25 ˚C.

ID & IDM = f(VDS); IDM single pulse; parameter tp RDS(ON) = f(ID)

August 1999 3 Rev 1.100

Philips Semiconductors Product specification

N-channel TrenchMOS transistor IRF530N

Drain current, ID (A) Threshold Voltage, VGS(TO) (V)

4.5

20

VDS > ID X RDS(ON) 4

18 maximum

16 3.5

14 3 typical

12

2.5

10 minimum

2

8

175 C 1.5

6

Tj = 25 C

4 1

2 0.5

0 0

0 1 2 3 4 5 6 7 8 9 10 -60 -40 -20 0 20 40 60 80 100 120 140 160 180

Gate-source voltage, VGS (V) Junction Temperature, Tj (C)

Fig.7. Typical transfer characteristics. Fig.10. Gate threshold voltage.

ID = f(VGS) VGS(TO) = f(Tj); conditions: ID = 1 mA; VDS = VGS

Transconductance, gfs (S) Drain current, ID (A)

15 1.0E-01

14 VDS > ID X RDS(ON)

13 Tj = 25 C

12 1.0E-02

11

10

175 C minimum

9 1.0E-03

8

7 typical

6 1.0E-04

5 maximum

4

3 1.0E-05

2

1

0 1.0E-06

0 2 4 6 8 10 12 14 16 18 20 0 0.5 1 1.5 2 2.5 3 3.5 4 4.5 5

Drain current, ID (A) Gate-source voltage, VGS (V)

Fig.8. Typical transconductance, Tj = 25 ˚C. Fig.11. Sub-threshold drain current.

gfs = f(ID) ID = f(VGS); conditions: Tj = 25 ˚C; VDS = VGS

Normalised On-state Resistance

2.9 Capacitances, Ciss, Coss, Crss (pF)

2.7 10000

2.5

2.3

2.1

1000 Ciss

1.9

1.7

1.5

1.3 Coss

100

1.1

0.9

0.7 Crss

0.5 10

-60 -40 -20 0 20 40 60 80 100 120 140 160 180 0.1 1 10 100

Junction temperature, Tj (C) Drain-Source Voltage, VDS (V)

Fig.9. Normalised drain-source on-state resistance. Fig.12. Typical capacitances, Ciss, Coss, Crss.

RDS(ON)/RDS(ON)25 ˚C = f(Tj) C = f(VDS); conditions: VGS = 0 V; f = 1 MHz

August 1999 4 Rev 1.100

Philips Semiconductors Product specification

N-channel TrenchMOS transistor IRF530N

Source-Drain Diode Current, IF (A) Maximum Avalanche Current, IAS (A)

20 100

VGS = 0 V

18

16

14

10

25 C

12

175 C

10

8

Tj = 25 C Tj prior to avalanche = 150 C

6 1

4

2

0 0.1

0 0.1 0.2 0.3 0.4 0.5 0.6 0.7 0.8 0.9 1 1.1 1.2 0.001 0.01 0.1 1 10

Source-Drain Voltage, VSDS (V) Avalanche time, tAV (ms)

Fig.13. Typical reverse diode current. Fig.14. Maximum permissible non-repetitive

IF = f(VSDS); conditions: VGS = 0 V; parameter Tj avalanche current (IAS) versus avalanche time (tAV);

unclamped inductive load

August 1999 5 Rev 1.100

Philips Semiconductors Product specification

N-channel TrenchMOS transistor IRF530N

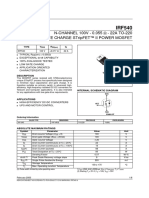

MECHANICAL DATA

Plastic single-ended package; heatsink mounted; 1 mounting hole; 3-lead TO-220 SOT78

E A

P A1

q

D1

L2(1) L1

Q

b1

L

1 2 3

b c

e e

0 5 10 mm

scale

DIMENSIONS (mm are the original dimensions)

(1)

UNIT A A1 b b1 c D D1 E e L L1 L2 P q Q

max.

4.5 1.39 0.9 1.3 0.7 15.8 6.4 10.3 15.0 3.30 3.8 3.0 2.6

mm 2.54 3.0

4.1 1.27 0.7 1.0 0.4 15.2 5.9 9.7 13.5 2.79 3.6 2.7 2.2

Note

1. Terminals in this zone are not tinned.

OUTLINE REFERENCES EUROPEAN

ISSUE DATE

VERSION IEC JEDEC EIAJ PROJECTION

SOT78 TO-220 97-06-11

Fig.15. SOT78 (TO220AB); pin 2 connected to mounting base (Net mass:2g)

Notes

1. This product is supplied in anti-static packaging. The gate-source input must be protected against static

discharge during transport or handling.

2. Refer to mounting instructions for SOT78 (TO220AB) package.

3. Epoxy meets UL94 V0 at 1/8".

August 1999 6 Rev 1.100

Philips Semiconductors Product specification

N-channel TrenchMOS transistor IRF530N

DEFINITIONS

Data sheet status

Objective specification This data sheet contains target or goal specifications for product development.

Preliminary specification This data sheet contains preliminary data; supplementary data may be published later.

Product specification This data sheet contains final product specifications.

Limiting values

Limiting values are given in accordance with the Absolute Maximum Rating System (IEC 134). Stress above one

or more of the limiting values may cause permanent damage to the device. These are stress ratings only and

operation of the device at these or at any other conditions above those given in the Characteristics sections of

this specification is not implied. Exposure to limiting values for extended periods may affect device reliability.

Application information

Where application information is given, it is advisory and does not form part of the specification.

Philips Electronics N.V. 1999

All rights are reserved. Reproduction in whole or in part is prohibited without the prior written consent of the

copyright owner.

The information presented in this document does not form part of any quotation or contract, it is believed to be

accurate and reliable and may be changed without notice. No liability will be accepted by the publisher for any

consequence of its use. Publication thereof does not convey nor imply any license under patent or other

industrial or intellectual property rights.

LIFE SUPPORT APPLICATIONS

These products are not designed for use in life support appliances, devices or systems where malfunction of these

products can be reasonably expected to result in personal injury. Philips customers using or selling these products

for use in such applications do so at their own risk and agree to fully indemnify Philips for any damages resulting

from such improper use or sale.

August 1999 7 Rev 1.100

You might also like

- IRF540Document9 pagesIRF540paul mathewNo ratings yet

- IRFZ24NDocument8 pagesIRFZ24NarcatusNo ratings yet

- Datasheet 6Document9 pagesDatasheet 6Ivanor Ipanaque CordovaNo ratings yet

- N-Channel Enhancement Mode Irfz48N Trenchmos Transistor: General Description Quick Reference DataDocument8 pagesN-Channel Enhancement Mode Irfz48N Trenchmos Transistor: General Description Quick Reference DataNixon MaldonadoNo ratings yet

- N-Channel Enhancement Mode Irfz44N Trenchmos Transistor: General Description Quick Reference DataDocument8 pagesN-Channel Enhancement Mode Irfz44N Trenchmos Transistor: General Description Quick Reference DataingucvNo ratings yet

- N-Channel Trenchmos Transistor Phx9Nq20T, Phf9Nq20T: Features Symbol Quick Reference DataDocument10 pagesN-Channel Trenchmos Transistor Phx9Nq20T, Phf9Nq20T: Features Symbol Quick Reference DatareparacionesdmaNo ratings yet

- Buk9635-100a 1Document7 pagesBuk9635-100a 1Raul OsoNo ratings yet

- BUK 9575 - Interruptor de PotênciaDocument8 pagesBUK 9575 - Interruptor de PotênciaTiago LeonhardtNo ratings yet

- N-Channel Trenchmos Transistor Psmn040-200W: Features Symbol Quick Reference DataDocument7 pagesN-Channel Trenchmos Transistor Psmn040-200W: Features Symbol Quick Reference DataRobert sibueaNo ratings yet

- N-Channel Enhancement Mode Irfz44Ns Trenchmos Transistor: General Description Quick Reference DataDocument8 pagesN-Channel Enhancement Mode Irfz44Ns Trenchmos Transistor: General Description Quick Reference DataDaniel Orlando Carballo FernándezNo ratings yet

- Powermos Transistor Irf730 Avalanche Energy Rated: Features Symbol Quick Reference DataDocument7 pagesPowermos Transistor Irf730 Avalanche Energy Rated: Features Symbol Quick Reference DataCarlos Morales AvilaNo ratings yet

- Trenchmos Transistor Buk7624-55 Standard Level Fet: General Description Quick Reference DataDocument8 pagesTrenchmos Transistor Buk7624-55 Standard Level Fet: General Description Quick Reference DataNicki LarsonNo ratings yet

- Powermos Transistors Irfp460 Avalanche Energy Rated: Features Symbol Quick Reference DataDocument7 pagesPowermos Transistors Irfp460 Avalanche Energy Rated: Features Symbol Quick Reference DataRio CandrapurwitaNo ratings yet

- Buk555 60a PDFDocument7 pagesBuk555 60a PDFGiraldoCarpioRamosNo ratings yet

- PDF Philips 26610Document11 pagesPDF Philips 26610ecsa tallerNo ratings yet

- Buk7514 55a - Buk7614 55aDocument9 pagesBuk7514 55a - Buk7614 55aHabacuc LopezNo ratings yet

- Buk7508 Buk7608-55a 1Document9 pagesBuk7508 Buk7608-55a 1Habacuc LopezNo ratings yet

- Powermos Transistors Php6N60E, Phb6N60E Avalanche Energy RatedDocument9 pagesPowermos Transistors Php6N60E, Phb6N60E Avalanche Energy RatedEmmanuel ZambranoNo ratings yet

- Important Notice: Kind RegardsDocument8 pagesImportant Notice: Kind Regardscarlosjamal95No ratings yet

- Buk455 200a PDFDocument8 pagesBuk455 200a PDFCarl Conter OnderNo ratings yet

- IRF540 ST PDFDocument8 pagesIRF540 ST PDFbaharNo ratings yet

- N-CHANNEL 100V - 0.055 - 22A TO-220 Low Gate Charge Stripfet™ Ii Power MosfetDocument8 pagesN-CHANNEL 100V - 0.055 - 22A TO-220 Low Gate Charge Stripfet™ Ii Power MosfetCode Main ProjectNo ratings yet

- Irf 540Document8 pagesIrf 540Tom TweedleNo ratings yet

- IRF540 ST PDFDocument8 pagesIRF540 ST PDFRubenNo ratings yet

- IRF540 ST PDFDocument8 pagesIRF540 ST PDFbaharNo ratings yet

- N-CHANNEL 100V - 0.055 - 22A TO-220 Low Gate Charge Stripfet™ Ii Power MosfetDocument8 pagesN-CHANNEL 100V - 0.055 - 22A TO-220 Low Gate Charge Stripfet™ Ii Power MosfetCode Main ProjectNo ratings yet

- IRF540 ST PDFDocument8 pagesIRF540 ST PDFbaharNo ratings yet

- N-CHANNEL 100V - 0.055 - 22A TO-220 Low Gate Charge Stripfet™ Ii Power MosfetDocument8 pagesN-CHANNEL 100V - 0.055 - 22A TO-220 Low Gate Charge Stripfet™ Ii Power MosfetCode Main ProjectNo ratings yet

- STP60NS04Z: N-Channel Clamped 10M - 60A TO-220 Fully Protected Mesh Overlay™ MosfetDocument8 pagesSTP60NS04Z: N-Channel Clamped 10M - 60A TO-220 Fully Protected Mesh Overlay™ MosfetВлад НNo ratings yet

- Trenchmos Transistor Buk9535-55A Logic Level Fet Buk9635-55ADocument9 pagesTrenchmos Transistor Buk9535-55A Logic Level Fet Buk9635-55AMotor CsillagNo ratings yet

- CRST065N08N Datasheet - Moto ElétricaDocument10 pagesCRST065N08N Datasheet - Moto ElétricaDenis OliveiraNo ratings yet

- Bf245a B CDocument11 pagesBf245a B CtemplpaNo ratings yet

- Bf245a bf245b bf245c - 2Document11 pagesBf245a bf245b bf245c - 2Antony VilcayauriNo ratings yet

- APM1105NFP Sinopower PDFDocument11 pagesAPM1105NFP Sinopower PDFFrancisco Alexander HernandezNo ratings yet

- P75N02LDG: N-Channel Enhancement Mode MOSFETDocument5 pagesP75N02LDG: N-Channel Enhancement Mode MOSFETAriel Rodrigo MuñozNo ratings yet

- 09 N 70 IDocument4 pages09 N 70 IIwan YogyaNo ratings yet

- Irlr3705Zpbf Irlu3705Zpbf: FeaturesDocument11 pagesIrlr3705Zpbf Irlu3705Zpbf: FeaturesGanNo ratings yet

- KIA KIA KIA: 1.descriptionDocument5 pagesKIA KIA KIA: 1.descriptionzakreaNo ratings yet

- Powermos Transistor Buk475-200A/B Isolated Version of Buk455-200A/BDocument7 pagesPowermos Transistor Buk475-200A/B Isolated Version of Buk455-200A/Bmaykel valdezNo ratings yet

- 9T16GH MOSFET CANAL N SMDDocument4 pages9T16GH MOSFET CANAL N SMDVictorManuelBernalBlancoNo ratings yet

- K2611 K2611 K2611 K2611: FeaturesDocument7 pagesK2611 K2611 K2611 K2611: FeaturesAndrew BanezNo ratings yet

- CRJQ190N65GCFDocument9 pagesCRJQ190N65GCFVadim PopovichNo ratings yet

- K2611 K2611 K2611 K2611: FeaturesDocument7 pagesK2611 K2611 K2611 K2611: Featureskaung kyel zin aung zaw moeNo ratings yet

- 70L02GHDocument8 pages70L02GHJtzabalaNo ratings yet

- 10fhy RSM1 Gan TF (LF) (SN)Document11 pages10fhy RSM1 Gan TF (LF) (SN)Mohamed ReyadNo ratings yet

- IRF840 AdvancedPowerElectronicsDocument4 pagesIRF840 AdvancedPowerElectronicssheikh sheharyarNo ratings yet

- Isc N-Channel MOSFET Transistor STD10NM60N: INCHANGE SemiconductorDocument2 pagesIsc N-Channel MOSFET Transistor STD10NM60N: INCHANGE SemiconductorY. Leonel MolinaNo ratings yet

- Irfr3505Pbf Irfu3505Pbf: FeaturesDocument11 pagesIrfr3505Pbf Irfu3505Pbf: FeaturesAzizullah AlizayNo ratings yet

- STP40NF10L: N-CHANNEL 100V - 0.028 - 40A TO-220 Low Gate Charge Stripfet™ Power MosfetDocument8 pagesSTP40NF10L: N-CHANNEL 100V - 0.028 - 40A TO-220 Low Gate Charge Stripfet™ Power MosfetCarlos A AvilaNo ratings yet

- Infineon IRFR540Z DataSheet v01 01 EN-3166491Document13 pagesInfineon IRFR540Z DataSheet v01 01 EN-3166491ANo ratings yet

- HGP105N15SLDocument6 pagesHGP105N15SLمحمد الراويNo ratings yet

- AP65SL190AI AdvancedPowerElectronicsDocument6 pagesAP65SL190AI AdvancedPowerElectronicsAkhmad Isnaeni RamdaniNo ratings yet

- MOSFETDocument7 pagesMOSFETjoswil21No ratings yet

- 10n65a 10n65afDocument6 pages10n65a 10n65afYeo LeoNo ratings yet

- j177 PDFDocument6 pagesj177 PDFMc Charles Adonis CaguitlaNo ratings yet

- Semiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsFrom EverandSemiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsNo ratings yet

- Hotone Ampero en PDFDocument86 pagesHotone Ampero en PDFFrancesco Cardillo0% (1)

- HVDCDocument20 pagesHVDCChloé Sid FILLEURNo ratings yet

- RRU 4G &5G Heatsink Design and Experimental EvaluationDocument13 pagesRRU 4G &5G Heatsink Design and Experimental EvaluationAnonymous P8Bt46mk5I100% (1)

- Fiche Technique BarrièreDocument2 pagesFiche Technique Barrièrepuriste modéréNo ratings yet

- Solis 30K User ManualDocument24 pagesSolis 30K User ManualHRNo ratings yet

- Arteche CT Tripping Relays Catalog PDFDocument28 pagesArteche CT Tripping Relays Catalog PDFtamky SubstationNo ratings yet

- Setup WizardDocument11 pagesSetup WizardMarlon CameyNo ratings yet

- MIL - Module 4Document10 pagesMIL - Module 4France PotterNo ratings yet

- BLRBACDocument78 pagesBLRBACJabulani2010100% (1)

- Manual Panasonic AG-DVC15Document4 pagesManual Panasonic AG-DVC15richercitolector01No ratings yet

- History of MediaDocument17 pagesHistory of Mediaapi-424887093No ratings yet

- E BallDocument22 pagesE BallKanishk YenugulaNo ratings yet

- Pic LedDocument4 pagesPic LededosviracNo ratings yet

- L37 WPAN Security PDFDocument28 pagesL37 WPAN Security PDFKalagara SaiNo ratings yet

- 5 DC GridsDocument75 pages5 DC GridsNamiraNo ratings yet

- Computer Architecture...Document8 pagesComputer Architecture...abdul.mannan.bcs.24No ratings yet

- Headset TesterDocument2 pagesHeadset Testerwaldo545No ratings yet

- Brand Fatigue: Case Study - ONIDADocument9 pagesBrand Fatigue: Case Study - ONIDADlichrisNo ratings yet

- Ces Manual-Ame 513Document31 pagesCes Manual-Ame 513Anush AntonyNo ratings yet

- Cast Resin TransformerDocument29 pagesCast Resin Transformerkrmurali2000No ratings yet

- Speech Quality and MOSDocument27 pagesSpeech Quality and MOSraghav_Sareen33% (3)

- FCC Regulations Part 97 PDFDocument2 pagesFCC Regulations Part 97 PDFChristopherNo ratings yet

- Eee 226 Microprocessor I ProposalDocument3 pagesEee 226 Microprocessor I Proposal楊傑克No ratings yet

- ARL-300 EU-Type Examination CertificateDocument1 pageARL-300 EU-Type Examination CertificateSamir Ben RomdhaneNo ratings yet

- Sweep Frequency Response Analyzer: Frax 99Document5 pagesSweep Frequency Response Analyzer: Frax 99Ajit KumarNo ratings yet

- PC1800 6Document18 pagesPC1800 6Mohsen KhabirNo ratings yet

- Antenna Training System PDFDocument2 pagesAntenna Training System PDFMerlin Gilbert Raj0% (1)

- ReadmeDocument4 pagesReadmeNicolas TorrezNo ratings yet

- LG Split Type Air Conditioner Complete Service ManualDocument74 pagesLG Split Type Air Conditioner Complete Service ManualArt Del R Salonga85% (75)

- Adham Al-Hassanieh CVDocument2 pagesAdham Al-Hassanieh CVAdham M. HassaniehNo ratings yet