Professional Documents

Culture Documents

الترانزيستور ذو الحقل المؤتر Jfet

الترانزيستور ذو الحقل المؤتر Jfet

Uploaded by

Ahmed AlsheikhCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

الترانزيستور ذو الحقل المؤتر Jfet

الترانزيستور ذو الحقل المؤتر Jfet

Uploaded by

Ahmed AlsheikhCopyright:

Available Formats

إعداد :احمد زھار

الترانزيستور االليكترونيك

الترانزيستور ذو تأثير الحقل

مبدأ العمل 1.1

الفرق بين transistor bipolaireو) JFETمن االنجليزية "Junction Field Effect

" (Transistorھو أن األول يتحكم به عن طريق تيار و األخر عن طريق توتر .تركيبة JFETنوع N

تعتمد على قطبان من أشباه-الموصالت من نوع Nمحاطة بحلقة من نوع .Pتركيبة JFETنوع Pتعتمد

على قطبان من أشباه-الموصالت من نوع Pمحاطة بحلقة من نوع .Nالمنطقة السفلى تسمى المنبع

صرف drainو بينھما توجد الشبكة .grilleااللكترونات تمر عبر ممر ضيق ،sourceالعليا تسمى ال َم ِ

من المنبع إلى المصرف .إن عرض ھذه القناة مھم ألنه يحدد شدة التيار الذي يمر عبر . JFET

Drain من نوع N

Barreau قضيبde

typeN D

Grille G

P P

N N

Beignet من de

نوع P type

Pحلقة

D S

Source

G

S

الشكل0

الحلقة و القضيب يشكالن وصل ) . PN (jonctionمنطقة الضعيفة حول الوصل ) (jonctionعازلة.

قطر ھذه األخيرة يتحكم ببعد القناة وسط الحلقة .في حالة JFETمن نوع ،Nالشبكة ستكون مستقطبة بتوتر

سلبي بالنسبة للقضبان .الغرض من منطقة الضعف ھو انه إذا كانت القناة صغيرة يكون التوتر UGSكبيرا و

التيار الذي المار في JFETصغيرا.الشكل 2يمثل استقطاب عادي للترانزيستور JFETمن نوع Nو .P

ultrasup@gmail.com الصفحة 1 احمد زھار

الترانزيستور االليكترونيك

ID ID

_

G D + Udd G D Udd

Ugg Ugg

_

_ S + S +

+ _

TypeN N

نوع Type

نPوع P

الشكل 2

إن ترانزيستور JFETال يطلب أي تيار في الشبكة لكي يعمل .و كان له ممانعة جدا عالية .ممانعة

المضخم العملياتي نوع TL071مثال تساوي !.1 TΩ

خاصياتJFET 1.2

ھي تحديد UGSالذي يخلق تيار المصرف ).(IDلكن يجب استقطاب الترانزيستور قبال.

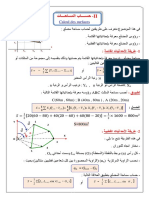

مبيان التياران ) id(udsو )id(ugs 1.3

الشكل 3أسفله يبن العالقة تيار المصرف IDو التوتر UDSبداللة توترات UGSمعطاة .ھذه المنحنيات

مشابھة لمنحنيات الترانزيستور العادي ) .IC(UCEالفرق يتجلى في توتر اإلشباع الكبير و الذي يتغير حسب

UGSو أن المنحنيات متقاربة نوعا ما.

ID

UGS = 0V

IDSS 10mA

UGS = -1V

5mA

UGS = -2V

2,5mA

UGS = -3V

1,25mA

UGSoff = -4V UDS

| Up = | UGSoff BUgds

Zone d'utilisation

االستعمال منطقة

الشكل 3

القيم في المبيان ليست سوى على سبيل المثال )ھناك قيم أخرى( .ھذا معناھا:

• : IDSSتيار المصرف عند .UGS = 0V

• : UGSoffالتوتر بين الشبكة و المنبع الالزم لكبح .JFET

• ): Upتوتر القرص( ھو توتر إشباع الترانزيستور .@ IDSS

• : BUgdsتوتر الكبح او الفصل )» (« break down voltageللترانزيستور .JFET

ultrasup@gmail.com الصفحة 2 احمد زھار

الترانزيستور االليكترونيك

ID

1

0,9

0,8

0,7

0,6

0,5

0,4

0,3

0,2

0,1

UGS 0

1 0,9 0,8 0,7 0,6 0,5 0,4 0,3 0,2 0,1 0

الشكل :4مبيان التوصيالت

في الشكل ، 4نجد العالقة الرياضياتية الموحدة بين IDو .UGSھذه العالقة صحيحة مادام JFET

مستعمال في منطقة العمليات )الشكل .(3ھذه العالقة مرباعاتية و ھو ما يشرح المسافة الفاصلة بين

المبيانات .المبيان يسمى مبيان .transconductance

العالقة الرياضياتية :

ID = IDSS x (1 - UGS / UGSoff)2

او كذلك :

)UGS = -UGSoff x (û(ID / IDSS) -1

ultrasup@gmail.com الصفحة 3 احمد زھار

الترانزيستور االليكترونيك

استقطاب JFET 1.4

1.4.1استقطاب عادي

مثال بسيط .مولد توتر ) (Uggمضبوط على أساس إنتاج التيار المرغوب به .ID

IDSS = 10mA

RD

UGSoff = -5V

1k

Udd

D 15V

G

Ugg

S

2,5V

الشكل 5

Ugg = UGS

ID = 10mA x (1 - -2,5V / -5V)2 = 2,5mA

UD = 15V - 2,5mA x 1k = 12,5V

- 1 #سؤال :

ما ھي قيمة Uggالضرورية للحصول علي تتوتر UDيساوي 10V؟

الحل :

URD = 15V - 10V = 5V

ID = 5V / 1k = 5mA

Ugg = UGS = 5V ( û( 5mA / 10mA) -1) = -1,46V

1.4.2استقطاب أوتوماتيكي

ھذه الطريقة تعتمد على وضع مقاومة بين المصرف ونقطة االشتراك و مقاومة بين الشبكة ونقطة

االشتراك )توتر الشبكة يساوي .( 0Vھذه المقاومة ھي التي تحدد ممانعة دخول .JFET

ultrasup@gmail.com الصفحة 4 احمد زھار

الترانزيستور االليكترونيك

IDSS = 10mA

RD

UGSoff = -5V

1k

Udd

D 15V

G

S

RG RS

100k 1k

نقطة االشتراك

الشكل 6

تيار المنبع متعلق ب .UGSتوتر الشبكة يساوي ) 0 vال تيار يمر( .إذن التوتر UGSمحدد بتوتر المنبع،

و الذي يحدد التوتر بين قطبي RSو يحدد تيار المنبع .إذن نظام ذو معادلتين

#1: ID = IDSS x (1 - UGS / UGSoff)2

#2: ID = -UGS / RS

قف :الحساب معقد نوعا ما و لتسھيل و ربح الوقت استعن بالشكل : 4

في محور IDيتمثل IDSSفي حالتنا .10mAفي محور UGSيتمثل UGSoffفي حالتنا .-5V

المعادلة #2ھي معادلة مستقيم ميله يساوي -1/RSحيت األصل في الصفر ،إليجاد نقطة أخرى من

المستقيم نعوض UGSب .-5V

.ID=-(-5V)/1k=5mAاآلن لدينا إحداثيات ) .(-5V, 5mAنرسم إذن المستقيم .نقطة تقاطع المستقيم و

المنحنى تعطي التيار IDQو التوتر ،UGSحيت يساويان ) .2,5mA et 2,5Vالشكل 7المستقيم األيسر(.

UD = 15V - 2,5mA x 1k = 12,5V

US = 2,5mA x 1k = 2,5V

UDSQ = 12,5V - 2,5V = 10V

ultrasup@gmail.com الصفحة 5 احمد زھار

الترانزيستور االليكترونيك

ID

10mA

)(0,725V, 7,25mA 0,9

0,8

7,25mA

0,7

)(-5V, 5mA 0,6

0,5

)(-2,5V, 2,5mA 0,4

0,3

2,5mA

0,2

0,1

UGS 0

-5V -0,9 -0,8 -0,7 -0,6 -0,5 -0,4 -0,3 -0,2 -0,1 0

0,725V

-2,5V

الشكل 7

مثال: -1#

السؤال :

جد للدارة في الشكل ) 6مع تعويض RSب IDQ, UGS, UD, US et UDSQ :(100Ω؟

الحل :

لنفترض تيارا = .10mAھذا يعني ان التوتر بين قطبي RSھو .1Vالشكل 7يعطي نقطة التقاطع

)) (0,725V et 7,25mAالمستقيم األيمن(.

UD = 15V - 7,25mA x 1k = 7,75V

US = 0,725V

UDSQ = 7,75V - 0,725V = 7,03V

ultrasup@gmail.com الصفحة 6 احمد زھار

You might also like

- تقرير تجربة قنطرة وتستون.Document5 pagesتقرير تجربة قنطرة وتستون.Siraj AL sharif75% (12)

- القنطرة المتريةDocument4 pagesالقنطرة المتريةYousef Sailini50% (4)

- Multimeter PDFDocument19 pagesMultimeter PDFAhmed AlsheikhNo ratings yet

- JFET1 OnlyDocument25 pagesJFET1 OnlyadilNo ratings yet

- 2Document44 pages2liobatmanNo ratings yet

- MOSFETDocument31 pagesMOSFETadilNo ratings yet

- Exo Circuit LC RLCDocument6 pagesExo Circuit LC RLCIhsan Mokhlisse100% (1)

- مجموعة الوكيلDocument10 pagesمجموعة الوكيلMahmoud AdelNo ratings yet

- CEDocument26 pagesCEadilNo ratings yet

- How To Measure Current, Voltage and Arc Power in Arc WeldingDocument11 pagesHow To Measure Current, Voltage and Arc Power in Arc Weldingsosolili4321No ratings yet

- (EL2-3) LED صمام ليدDocument5 pages(EL2-3) LED صمام ليدAhmed M. NawarNo ratings yet

- 27Document1 page27Med ElyoubiNo ratings yet

- PowerPoint 演示文稿Document139 pagesPowerPoint 演示文稿Amin darabiNo ratings yet

- ExerciceDocument3 pagesExerciceMOHAMED LABIADNo ratings yet

- Genie Electricite6Document1 pageGenie Electricite6Oúšşãmä ĐjézîríNo ratings yet

- تضمين الوسعDocument15 pagesتضمين الوسعalmuslim92% (12)

- 2 2Document1 page2 2boustakatbNo ratings yet

- الدوائر الكهربائية والقياسات د. معن عبدالرحمن سنويDocument40 pagesالدوائر الكهربائية والقياسات د. معن عبدالرحمن سنويSouhayl SaaidNo ratings yet

- Classic Control LECTURE 7Document17 pagesClassic Control LECTURE 7abdallah gomaaNo ratings yet

- MosfetDocument5 pagesMosfethejazi_mohamedNo ratings yet

- الموسفتDocument5 pagesالموسفتMohamed B Ali100% (1)

- ثنائي القطب RLDocument3 pagesثنائي القطب RLالغزيزال الحسن EL GHZIZAL Hassane100% (11)

- دوسية المشغلDocument42 pagesدوسية المشغلMohammad AghaNo ratings yet

- س و ج الكترونات القوى و يوجد بعض الاسئلة بدون اجاباتDocument28 pagesس و ج الكترونات القوى و يوجد بعض الاسئلة بدون اجاباتAbdallahHaniNo ratings yet

- الفصل الثامن الكواشف الضوئيةDocument18 pagesالفصل الثامن الكواشف الضوئيةAhmad Dawara0% (3)

- Exercices PC 2bac 02Document7 pagesExercices PC 2bac 02EmanuleNo ratings yet

- استخدام جهاز القياس الأفوميتر 3Document8 pagesاستخدام جهاز القياس الأفوميتر 3taharbiaNo ratings yet

- المحاضرة الثامنة أسس هندسة إلكترونيةDocument12 pagesالمحاضرة الثامنة أسس هندسة إلكترونيةattcshjj567No ratings yet

- Test 3TM M 2022Document3 pagesTest 3TM M 2022laidiwalid371No ratings yet

- تجارب الكهربائية اولDocument28 pagesتجارب الكهربائية اولEsraa WaheedNo ratings yet

- 5 7Document1 page5 7Kindman KindmanNo ratings yet

- الفصل الثامن الكواشف الضوئيةDocument31 pagesالفصل الثامن الكواشف الضوئيةKira100% (1)

- تجربة دارات القصDocument2 pagesتجربة دارات القصtarekhussein908No ratings yet

- القنطرة المترية PDFDocument4 pagesالقنطرة المترية PDFYousef Sailini0% (2)

- Riser سؤال 2005Document3 pagesRiser سؤال 2005ali azzamNo ratings yet

- Dzexams 2as Genie Civil 1478070Document6 pagesDzexams 2as Genie Civil 1478070samirasidalibouchramouaadNo ratings yet

- اختبار هندسة مدنية أقسام نهائي 2018 ثلاثي2 الأخيرDocument4 pagesاختبار هندسة مدنية أقسام نهائي 2018 ثلاثي2 الأخيرWaho HadakNo ratings yet

- المحولDocument12 pagesالمحولnoork12339No ratings yet

- دارة نجمية - ويكيبيدياDocument4 pagesدارة نجمية - ويكيبيدياsadiq. aljabha.2014No ratings yet

- 6 2018 11 01!07 57 56 PMDocument3 pages6 2018 11 01!07 57 56 PMjudybehet380No ratings yet

- المكبر LM385Document4 pagesالمكبر LM385Desouky100% (1)

- إيجاد مقاومة جلفامتر الظلDocument7 pagesإيجاد مقاومة جلفامتر الظلmahmab70No ratings yet

- 18Document6 pages18msmt1210No ratings yet

- HHHHHHHHHHHHHDocument9 pagesHHHHHHHHHHHHHاحمد فريشكNo ratings yet

- راسم الذبذباتDocument3 pagesراسم الذبذباتطه الحصن100% (1)

- Electronics LECTURE 1Document34 pagesElectronics LECTURE 1Abdallah GomaaNo ratings yet

- اختبار الفصل الثاني مع التصحيح ثانوية زيغود يوسف عنابة 2018Document12 pagesاختبار الفصل الثاني مع التصحيح ثانوية زيغود يوسف عنابة 2018Junior JuniusNo ratings yet

- Electronics LECTURE 3Document33 pagesElectronics LECTURE 3Abdallah GomaaNo ratings yet

- 2 5289534765152604786Document3 pages2 5289534765152604786Ahmed BassemNo ratings yet

- وظيفة منزلية 2Document2 pagesوظيفة منزلية 2dhiaa-eddine0% (2)

- Ondes Mec PeriodiquesDocument2 pagesOndes Mec PeriodiquesSaid BenkhaddaNo ratings yet

- Doc3 PDFJJDocument3 pagesDoc3 PDFJJnadaiiiiiNo ratings yet

- مغناطومتر الانحراف والقنطرة المترية وجلفانومتر الظلDocument44 pagesمغناطومتر الانحراف والقنطرة المترية وجلفانومتر الظلHagar KamalNo ratings yet

- Counters PDFDocument28 pagesCounters PDFMohmed Al NajarNo ratings yet

- فرض محروس رقم 10 في مادة الفيزياء والكيمياء السنة الثانية بكالوريا شعبة العلوم الفيزيائية الدورة الثانية من إنجاز الأستاذ الحسين عديDocument3 pagesفرض محروس رقم 10 في مادة الفيزياء والكيمياء السنة الثانية بكالوريا شعبة العلوم الفيزيائية الدورة الثانية من إنجاز الأستاذ الحسين عديمهدي محمدNo ratings yet

- حساب المساحات للأستاذDocument7 pagesحساب المساحات للأستاذAl Rayane ArafatNo ratings yet

- Dzexams 1as Techno Ge 20141 480722Document3 pagesDzexams 1as Techno Ge 20141 480722mn13hhNo ratings yet

- 000385Document6 pages000385Lazhar RamdaNo ratings yet

- الأفوميترDocument7 pagesالأفوميترkirookayNo ratings yet

- سلسلة التعرف علـى الحساسات المستخدمة مع الاردوينو الجزء الاولDocument13 pagesسلسلة التعرف علـى الحساسات المستخدمة مع الاردوينو الجزء الاولAhmed AlsheikhNo ratings yet

- كتاب مساعدات السيارة ونظام التعليق الإلكترونيDocument34 pagesكتاب مساعدات السيارة ونظام التعليق الإلكترونيAhmed AlsheikhNo ratings yet

- إجراءات السالمة في التعامل مع سيارات الهايبرد - بوابة التدريب PDFDocument55 pagesإجراءات السالمة في التعامل مع سيارات الهايبرد - بوابة التدريب PDFAhmed AlsheikhNo ratings yet