Professional Documents

Culture Documents

Question Bank CMOS VLSI 1

Uploaded by

Vaibhavraje Gaikwad0 ratings0% found this document useful (0 votes)

22 views4 pagesCopyright

© © All Rights Reserved

Available Formats

PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

© All Rights Reserved

Available Formats

Download as PDF, TXT or read online from Scribd

0 ratings0% found this document useful (0 votes)

22 views4 pagesQuestion Bank CMOS VLSI 1

Uploaded by

Vaibhavraje GaikwadCopyright:

© All Rights Reserved

Available Formats

Download as PDF, TXT or read online from Scribd

You are on page 1of 4

Fourth Y. B.Tech.

(Electronics & Telecommunication)

Question Bank on CMOS VLSI Design

Q. 1. Solve any four: [4 X 4 =16 Marks]

a. When Vgs of MOSFET with threshold voltage of 0.4 V, working in saturation region is

0.9 V, the drain current is observed to be 1 mA. Find the drain current if Vgs is 1.4 V.

b. Draw stick diagram of NAND gate.

c. Draw stick diagram of NOR gate.

d. Draw stick diagram of inverter.

e. Design NOR gate using CMOS logic.

f. Draw NAND gate using CMOS logic.

g. Design NOR gate using ratioed logic.

h. Design NAND gate using ratioed logic.

i. Differentiate between static and dynamic design in CMOS.

j. If supply voltage is 3 V and load capacitance is 5 fF, then calculate the amount of energy

stored on the capacitor.

k. If supply voltage is 3 V and load capacitance is 5 fF, then calculate the amount of energy

stored on the capacitor.

l. Define scaling. Explain the various types of scaling.

m. Design buffer using CMOS logic.

n. Explain the concept of dynamic CMOS logic with the help of example.

o. List out the various second order effects in MOS transistor.

Q.2. Solve any two: [2 X 6 = 12 Marks]

a. Explain various modes of operation in MOS transistor.

b. Explain the concept of Power, Energy and Energy Delay Product. If the load

capacitance is 6 fF and supply voltage is 2.5 V, then calculate the energy required

to charge and discharge the capacitance.

c. Obtain the current equations for MOS transistor in the cut off, non-saturation and

saturation region.

d. Explain the various signal integrity issues in Dynamic CMOS logic design.

e. Design 4:1 multiplexer using CMOS logic.

f. Explain the static and dynamic power dissipation for CMOS inverter. Obtain the

expression for total power dissipation.

g. Explain the following with respect to CMOS inverter:

i. Switching threshold ii. Noise Margin

h. Define threshold voltage for MOS transistor. Also, explain with the help of

equations various factors on which it depends.

i. Explain the various second order effects in MOS transistor.

Q. 3. Solve any four: [4 X 4 = 16 marks]

a. Explain multiplexer based positive latch.

b. Explain the concept of bistability principle.

c. Explain the concept of dynamic transmission-gate edge triggered registers.

d. Define the timing properties of registers.

e. Explain low voltage static latches.

f. Explain static SR flip flop.

g. Explain synchronizer with the help of neat diagram.

h. Explain clock skew and clock jitter.

i. Explain Wallace tree for 4 – bit multiplier.

j. Explain how PLL can be used to synchronize the clock.

k. Explain the concept of CLA adder with the help of equations.

l. Explain the concept of pseudo nMOS ROM with the help of neat diagram.

m. Explain the concept of 1 transistor DRAM cell. Also, draw the DRAM sub-array.

n. Explain the concept of Dual edge registers.

o. Write a note on:

i. Mesochronous interconnect ii. Plesiochronous interconnect

Q. 4. Solve the following: [2 X 6 = 12 Marks]

a. Classify timings depending on local clock.

b. Explain the concept of Bistability with the help of neat diagrams. Also, explain

metastability.

c. Explain how negative and positive level latches can be designed using multiplexers.

d. Explain C2MOS and TSPCR approach for skew tolerant.

e. Explain various clock distribution techniques.

f. Explain the concept of clock skew and clock jitter. What are the various sources of

Clock skew and clock jitter?

g. Explain the concept of clock distribution. What are the techniques to reduce clock

skew and clock jitter?

h. Explain the concept of CLA adder with the help of equations.

i. Explain the concept of 6 transistor SRAM cell. Also, explain read and write

operation using this memory cell.

You might also like

- Ec 703 2019-20Document2 pagesEc 703 2019-202000520310061No ratings yet

- CMOS Q BankDocument3 pagesCMOS Q BankRathore Yuvraj SinghNo ratings yet

- Question BankDocument13 pagesQuestion BankRishi JhaNo ratings yet

- VLSID R20 Q BankDocument4 pagesVLSID R20 Q BankSATYA SRI LIKHITHA DUSANAPUDINo ratings yet

- VLSI AssignDocument5 pagesVLSI AssignSrideviasokanNo ratings yet

- Vlsi Design Question Bank EEC 703Document10 pagesVlsi Design Question Bank EEC 703selvi0412No ratings yet

- Ec6111 - Vlsi DesignDocument9 pagesEc6111 - Vlsi DesignMegha SrivastavaNo ratings yet

- Interview QuestionsDocument6 pagesInterview QuestionskiranvlsiNo ratings yet

- Question BankDocument3 pagesQuestion BankTARUN PRASADNo ratings yet

- Vlsi - Ec - Be - Sem 5Document2 pagesVlsi - Ec - Be - Sem 5KrishnaNo ratings yet

- Vlsi BestDocument4 pagesVlsi Bestkunjanb11No ratings yet

- M.Tech. Degree Examination, Dec.08/Jan.09: Advances in VLSI DesignDocument1 pageM.Tech. Degree Examination, Dec.08/Jan.09: Advances in VLSI DesignRavindra vsNo ratings yet

- Kec 072 - CT2Document10 pagesKec 072 - CT22000520310061No ratings yet

- QB - CFD (U1 & U2) PDFDocument3 pagesQB - CFD (U1 & U2) PDFGanesh Natarajan SNo ratings yet

- Vlsi ModuleDocument2 pagesVlsi ModuleAshwini kumarNo ratings yet

- Kec 072 2023Document2 pagesKec 072 20232000520310061No ratings yet

- Analog Devices-To ShyamaDocument1 pageAnalog Devices-To Shyamahafeez_k_tNo ratings yet

- Question BankDocument9 pagesQuestion BankNiyas AhamedNo ratings yet

- Chapter Wise QuestionsDocument2 pagesChapter Wise QuestionshjjhghgNo ratings yet

- VLSI Question BankDocument2 pagesVLSI Question BankVikash SharmaNo ratings yet

- Logic DesignDocument2 pagesLogic DesignAman BatraNo ratings yet

- EC19641-VLSI Design Part B Question BankDocument2 pagesEC19641-VLSI Design Part B Question BankmyavananNo ratings yet

- Microwave and Radar QPDocument16 pagesMicrowave and Radar QPAdarsh RaiNo ratings yet

- CMOS VLSI Design - 102409020235 - 1Document7 pagesCMOS VLSI Design - 102409020235 - 1Raja Khurram ShahzadNo ratings yet

- A1429 VlsiDocument8 pagesA1429 VlsiratnamsNo ratings yet

- Mosfet and CMOSDocument4 pagesMosfet and CMOSRanga RajuNo ratings yet

- SMPLXDocument5 pagesSMPLXVikas DewanganNo ratings yet

- ASSIGNMENTiiiDocument1 pageASSIGNMENTiiiVarun ParasharNo ratings yet

- Mecve 101 SPDMDocument2 pagesMecve 101 SPDMSalini SasidharanNo ratings yet

- Vlsi Design 1 Mark QuestionsDocument7 pagesVlsi Design 1 Mark QuestionsVallabh JNo ratings yet

- DSVD Q BankDocument3 pagesDSVD Q BankAkhil ShettyNo ratings yet

- Vlsi QBDocument2 pagesVlsi QBSam Joel.DNo ratings yet

- C C1115 Pages 2: Answer Any Two Full Questions, Each Carries 15 MarksDocument2 pagesC C1115 Pages 2: Answer Any Two Full Questions, Each Carries 15 MarksFayaz aliNo ratings yet

- Q. No. Questions CO RBT Marks: Uestion ANK Ormat)Document2 pagesQ. No. Questions CO RBT Marks: Uestion ANK Ormat)Manjunath MNo ratings yet

- High Voltage Engineering PDFDocument2 pagesHigh Voltage Engineering PDFShweta KhadseNo ratings yet

- EC-72 Super-Imp-Tie-23Document2 pagesEC-72 Super-Imp-Tie-23Rocky BhaiNo ratings yet

- Explain Small Signal AC Characteristics of MOSFET With Its Design EquationsDocument11 pagesExplain Small Signal AC Characteristics of MOSFET With Its Design EquationsradhikasontakayNo ratings yet

- Dec 2018/ Jan 2019Document2 pagesDec 2018/ Jan 2019Kalyan HvNo ratings yet

- Question Bank Fundamentals of CMOS VLSI-10EC56 15-16Document10 pagesQuestion Bank Fundamentals of CMOS VLSI-10EC56 15-16Pranav KpNo ratings yet

- Ec1461 Vlsi DesignDocument17 pagesEc1461 Vlsi DesignArunkumarNo ratings yet

- Analog Ic DesignDocument2 pagesAnalog Ic DesignIbmWasuserNo ratings yet

- Measuring CMOS Dynamic Input CapacitanceDocument118 pagesMeasuring CMOS Dynamic Input CapacitanceDalton BentleyNo ratings yet

- Advanced Digital VLSI Design (ECE 521) (Makeup) PDFDocument2 pagesAdvanced Digital VLSI Design (ECE 521) (Makeup) PDFRahul PinnamaneniNo ratings yet

- Microwave Engineering Assignment 1 To 5Document6 pagesMicrowave Engineering Assignment 1 To 5Anonymous 4bUl7jzGqNo ratings yet

- CMOS Question Bank 1Document3 pagesCMOS Question Bank 1Sameer R. KhanNo ratings yet

- EDC - Old Question Papers For Unit 3, 4, 5Document19 pagesEDC - Old Question Papers For Unit 3, 4, 5Deepak SahuNo ratings yet

- 16EC5DCFOVDocument2 pages16EC5DCFOVvkjoshiNo ratings yet

- Q Paper 09ec61 May June 2012Document2 pagesQ Paper 09ec61 May June 2012Bhaskar MishraNo ratings yet

- Karunya University: Answer ALL Questions (5 X 20 100 Marks)Document1 pageKarunya University: Answer ALL Questions (5 X 20 100 Marks)Shylu SamNo ratings yet

- Assignment 4201 AY 2223Document2 pagesAssignment 4201 AY 2223Aravind TallaNo ratings yet

- Awp Question PaperDocument4 pagesAwp Question Paperpuja bhendarkarNo ratings yet

- BE (2nd) May19Document1 pageBE (2nd) May19jagdish singhNo ratings yet

- Chapter12 ExDocument4 pagesChapter12 ExVishwanath NatarajanNo ratings yet

- Assignment 2 Unit 2Document3 pagesAssignment 2 Unit 2Maharshi Sanand Yadav TNo ratings yet

- C C192023 Pages:2: Answer Any Two Full Questions, Each Carries 15 MarksDocument2 pagesC C192023 Pages:2: Answer Any Two Full Questions, Each Carries 15 MarksFayaz aliNo ratings yet

- MSC Physics Sem-3 PaperDocument29 pagesMSC Physics Sem-3 PaperschoolhelpmentorNo ratings yet

- PDC Assignment Questions: Semester:2-2 Teacher: T. BalajiDocument2 pagesPDC Assignment Questions: Semester:2-2 Teacher: T. Balajikprk414No ratings yet

- Edc Question Bank R20 2021Document5 pagesEdc Question Bank R20 2021khadarskb19No ratings yet

- Capacitor Discharges - Magnetohydrodynamics - X-Rays - UltrasonicsFrom EverandCapacitor Discharges - Magnetohydrodynamics - X-Rays - UltrasonicsRating: 5 out of 5 stars5/5 (1)

- Zener BZX 3V6Document2 pagesZener BZX 3V6Rifqi ZayusmanNo ratings yet

- Jjap Express Letter: P-Gan Contact Pd/Au ZroDocument3 pagesJjap Express Letter: P-Gan Contact Pd/Au ZroBillieNo ratings yet

- RF Transistor List: Bipolar NPN Power TransistorDocument5 pagesRF Transistor List: Bipolar NPN Power TransistorAnonymous XoW23y58O100% (3)

- Ideal: EE 233/51 Midterm 2 Spring 2017 Name: ID: There Are 15 Points in The Exam. Problem 1 (9 Points)Document5 pagesIdeal: EE 233/51 Midterm 2 Spring 2017 Name: ID: There Are 15 Points in The Exam. Problem 1 (9 Points)DodyAboDoddaNo ratings yet

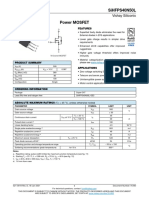

- Sihfps 40 N 50 LDocument10 pagesSihfps 40 N 50 LRAMESH JUNJUNo ratings yet

- Experiment 3 PDFDocument4 pagesExperiment 3 PDFVmosaNo ratings yet

- 2015 Model Predictive Control MPC's Role in The Evolution of Power ElectronicsDocument15 pages2015 Model Predictive Control MPC's Role in The Evolution of Power Electronicsdaiduongxanh14113No ratings yet

- Problems For BJT Section: Lecture Notes: Sec. 3Document9 pagesProblems For BJT Section: Lecture Notes: Sec. 3CattNo ratings yet

- 1 1 7 A Datasheets Mod 2Document6 pages1 1 7 A Datasheets Mod 2api-247436935No ratings yet

- Vlsi Lab 1Document11 pagesVlsi Lab 1Shawon karmokar JotyNo ratings yet

- Intrinsic Vs Extrinsic: Forward BiasingDocument9 pagesIntrinsic Vs Extrinsic: Forward BiasingnuruthinNo ratings yet

- SolarCell Lab Manual 06-2009Document43 pagesSolarCell Lab Manual 06-2009Muhammad Rahman NadeemNo ratings yet

- Experiment 2 The P-N Junction. DiodesDocument5 pagesExperiment 2 The P-N Junction. DiodesIrene SarpongNo ratings yet

- Vlsi Lab ManualDocument27 pagesVlsi Lab Manualnagarjun3802No ratings yet

- Silicon PhotonicsDocument112 pagesSilicon PhotonicsSabiran GibranNo ratings yet

- Stzta42: Small Signal NPN TransistorDocument5 pagesStzta42: Small Signal NPN TransistorAhmed Sherif CupoNo ratings yet

- 2sk3687 - 600V, 16ADocument4 pages2sk3687 - 600V, 16ARenatoMaiaNo ratings yet

- Beginning FPGA Programming - Partie24Document5 pagesBeginning FPGA Programming - Partie24ali alilouNo ratings yet

- Silicon PNP Power Transistors: Savantic Semiconductor Product SpecificationDocument4 pagesSilicon PNP Power Transistors: Savantic Semiconductor Product SpecificationEngin UzunNo ratings yet

- Photodetectors and Solar CellsDocument11 pagesPhotodetectors and Solar CellsavecafeNo ratings yet

- Unit 2Document23 pagesUnit 2poo235No ratings yet

- Eoc 1 e System AnsweredDocument4 pagesEoc 1 e System AnsweredSamNo ratings yet

- Analog VLSI Design: Technology TrendsDocument31 pagesAnalog VLSI Design: Technology TrendsSathyaNarasimmanTiagarajNo ratings yet

- Chapter 8Document85 pagesChapter 8edward solomonNo ratings yet

- ThereminoSystem SmdCodes PDFDocument95 pagesThereminoSystem SmdCodes PDFAgin TersakitiNo ratings yet

- 50N06 PDFDocument9 pages50N06 PDFAntonio Perez PerezNo ratings yet

- MTD3302T4 ON SemiconductorDocument12 pagesMTD3302T4 ON SemiconductorMacwill MoraNo ratings yet

- Bipolar Transistors: Fabrizio BonaniDocument64 pagesBipolar Transistors: Fabrizio BonaniBilal Haider TanoliNo ratings yet

- Chapter 3 CMOS Processing Technology: PassivationDocument1 pageChapter 3 CMOS Processing Technology: PassivationCarlos SaavedraNo ratings yet

- Silicon Switching Diode Array BAV 70: Type Ordering Code (Tape and Reel) Marking Package Pin ConfigurationDocument4 pagesSilicon Switching Diode Array BAV 70: Type Ordering Code (Tape and Reel) Marking Package Pin Configurationjavier venturaNo ratings yet