Professional Documents

Culture Documents

FA21 Lec16 2021-11-06 UART Programming

Uploaded by

MahreenOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

FA21 Lec16 2021-11-06 UART Programming

Uploaded by

MahreenCopyright:

Available Formats

UART

Programming in

AVR

LECTURE# 16

MICROPROCESSOR SYSTEMS AND INTERFACING

Saad Arslan COMSATS UNIVERSITY ISLAMABAD 1

Last Lecture

Keypad Interfacing

Serial Communication

◦ Simplex, Half Duplex and Full Duplex

◦ Synchronous and Asynchronous

◦ UART

◦ RS232

AVR Serial Port Programming

◦ Introduction

Saad Arslan COMSATS UNIVERSITY ISLAMABAD 2

Quiz 2

Saad Arslan COMSATS UNIVERSITY ISLAMABAD 3

Quiz 2 -

Saad Arslan COMSATS UNIVERSITY ISLAMABAD 4

Vector Program

Source Interrupt Definition

No. Address

Quiz 2 – Timer 8

9

10

0x000E

0x0010

0x0012

TIMER2_COMPA

TIMER2_COMPB

TIMER2_OVF

Timer/Counter2 Compare Match A

Timer/Counter2 Compare Match B

Timer/Counter2 Overflow

Programming using Interrupts

Q1. How many timers are available in AVR ATmega328?

Q2. What is the different between Normal and CTC mode?

◦ Write 2 - 3 lines each

Q3. Write steps (or C or assembly), register values and ISR to

◦ Configure timer 2 in CTC mode

◦ 𝐹𝑂𝑆𝐶 = 16 MHz, 𝐹𝑡𝑖𝑚𝑒𝑟2 = 2 MHz

◦ Using OCR2A register

◦ To toggle pin PC.3

◦ every (2 x reg#) clock cycles

◦ Using interrupts

Other registers are TCNT2, OCR2A, OCR2B

Saad Arslan COMSATS UNIVERSITY ISLAMABAD 5

Serial Communication

Offers communication over less number of wires

◦ Imagine LCD interfacing with 3 wires

Saad Arslan COMSATS UNIVERSITY ISLAMABAD 6

Simplex, Half and Full Duplex

UART offers Full Duplex

◦ Two simplex lines

Saad Arslan COMSATS UNIVERSITY ISLAMABAD 7

Synchronous and Asynchronous

Serial Communication

The sender and receiver should agree to a few rules

◦ Called protocol

In Synchronous communication

◦ the clock is shared between sender and receiver

In Asynchronous communication there is no shared clock

◦ Both sender and receiver have their own clock sources

◦ But should have same frequency (called baud rate)

◦ Also, extra bits are added to ensure reliable transfer

UART (Universal Asynchronous Receiver/Transmitter)

◦ is an asynchronous means of serial communication

Baud rate is signal changes per second

◦ Unlike bit rate which is number of bits sent per second

Saad Arslan COMSATS UNIVERSITY ISLAMABAD 8

UART Frame

In UART, communication is done, frame by frame

◦ Each frame contains 5-9 data bits, usually

Each character transmitted is placed between start and stop bit(s)

◦ This is called framing

There is always one start bit

◦ Start bit is logic low

Stop bit(s) can be one or two bits

◦ Stop bit(s) is always high

A UART frame is shown for sending 8 data bits 0b01000001

Saad Arslan COMSATS UNIVERSITY ISLAMABAD 9

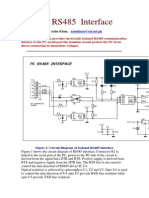

RS232

A standard for defining signals

◦ Voltage levels, pinouts, connectors

◦ Like COM ports on a PC

While UART define timings and bits

◦ RS232 defines physical signals

Unlike TTL, RS232

◦ Logic Low is +3 to +25 V

◦ Logic High is -3 to -25 V

◦ Undefined -3 to +3 V

A converter is needed

◦ MAX232

Saad Arslan COMSATS UNIVERSITY ISLAMABAD 10

ATMEGA328p and RS232

Connection of ATmega328p with PC using RS232 is shown below

◦ MAX232 IC translates logic levels between TTL (µC side) and RS232 (PC side)

Vcc Nowadays, USB-to-UART (TTL)

C3 converter is used instead, such

16 +

+ 2 as CH340 or CP2102 ICs.

C1 1 MAX232 ATmega328p To connect PC with µC.

3 6

+ C4 MAX232

4

C2 5 +

T1IN T1OUT (PD1)TXD 3 11

14 2

5

11 14

R1OUT R1IN

12 13 13 3

(PD0)RXD 2 12

T2IN T2OUT

10 7

R2OUT R2IN DB-9

9 8

TTL side 15 RS232 side 40-Pin DIP Package ATmega32

Corrected version of

Figure 11-7 (a) Inside MAX232 and (b) Its connection to ATmega328p*

Saad Arslan COMSATS UNIVERSITY ISLAMABAD 11

AVR Serial port programming

Baud rate calculation

→

For 8 MHz oscillator:

Saad Arslan COMSATS UNIVERSITY ISLAMABAD 12

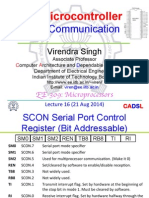

AVR Registers

UBRR0

◦ URSEL = 0

UDR0

◦ Tx and Rx Register

UCSR0A, UCSR0B & UCSR0C

Saad Arslan COMSATS UNIVERSITY ISLAMABAD 13

AVR Registers

UCSR0A RXC0 TXC0 UDRE0 FE0 DOR0 UPE0 U2X0 MPCM0

RXC (Bit 7): USART Receive Complete

This flag bit is set when there are new data in the receive buffer that are not read yet. It is cleared when the receive buffer is

empty. It also can be used to generate a receive complete interrupt.

TXC (Bit 6): USART Transmit Complete

This flag bit is set when the entire frame in the transmit shift register has been transmitted and there are no new data available in

the transmit data buffer register (TXB). It can be cleared by writing a one to its bit location. Also, it is automatically cleared when

a transmit complete interrupt is executed. It can be used to generate a transmit complete interrupt.

jab yeh bit UCSR0A mein empty ho ga tou it will get ready to receive the new data jo k us ko print

UDRE (Bit 5): USART Data Register Empty karw a ga if we want to print something udre0a should be empty in register UCSR0A

This flag is set when the transmit data buffer is empty and it is ready to receive new data. If this bit is cleared, you should not

write to UDR because it overrides your las tdata. The UDRE flag can generate a data register empty interrupt.

FE (Bit 4): Frame Error

This bit is set if a frame error has occurred in receiving the next character in the receive buffer. A frame error is detected when the

first stop bit of the next character in the receive buffer is zero.

DOR (Bit 3): Data OverRun

This bit is set if a data overrun is detected. A data overrun occurs when the receive data buffer and receive shift register are full,

and a new start bit is detected.

PE (Bit 2): Parity Error

This bit is set if parity checking was enabled (UPM1 = 1) and the next character in the receive buffer had a parity error when

received.

U2X (Bit 1): Double the USART Transmission Speed

Setting this bit will double the transfer rate for asynchronous communication.

MPCM (Bit 0): Multi-processor Communication Mode

This bit enables the multi-processor communication mode. The MPCM feature is not discussed in this text.

Notice that FE, DOR, and PE are valid until the receive buffer (UDR) is read. Always

Saad Arslan COMSATS UNIVERSITY ISLAMABAD 14

Enable transmitter

AVR Registers Enable receiver

UCSR0B RXCIE0 TXCIE0 UDRIE0 RXEN0 TXEN0 UCSZ02 RXB80 TXB80

RXCIE (Bit 7): Receive Complete Interrupt Enable

To enable the interrupt on the RXC flag in UCSRA you should set this bit to one. UCSR0B=0b10000000

TXCIE (Bit 6): Transmit Complete Interrupt Enable

To enable the interrupt on the TXC flag in UCSRA you should set this bit to one. UCSR0B=0b01000000

UDRIE (Bit 5): USART Data Register Empty Interrupt Enable

To enable the interrupt on the UDRE flag in UCSRA you should set this bit to one. UCSR0B=0b00100000

RXEN (Bit 4): Receive Enable

To enable the USART receiver you should set this bit to one.

UCSR0B=0b00011000

TXEN (Bit 3): Transmit Enable

To enable the USART transmitter you should set this bit to one.

UCSZ2 (Bit 2): Character Size

This bit combined with the UCSZ1:0 bits in UCSRC sets the number of data bits (character size) in a frame.

RXB8 (Bit 1): Receive data bit 8

This is the ninth data bit of the received character when using serial frames with nine

TXB8 (Bit 0): Transmit data bit 8

This is the ninth data bit of the transmitted character when using serial frames with nine data bits. This bit is not used in this text.

Saad Arslan COMSATS UNIVERSITY ISLAMABAD 15

AVR Registers

UCSR0C

UMSEL01 UMSEL00 UPM01 UPM00 USBS0 UCSZ01 UCSZ00 UCPOL0

USBS0 Stop Bit Select

0 1-bit

1 2-bit

UPM[1:0] Parity Mode UCSZ0[2:0] Character Size

00 Disabled 000 5-bit

01 (Reserved 001 6-bit

10 Even Parity 010 7-bit

11 Odd Parity 011 8-bit

100 (Reserved)

UMSEL01 UMSEL00 Mode 101 (Reserved)

0 0 Asynchronous USART 110 (Reserved)

0 1 Synchronous USART 111 9-bit

1 0 (Reserved)

1 1 Master SPI (MSPIM) UCPOL Used in Synchronous Mode

Saad Arslan COMSATS UNIVERSITY ISLAMABAD 16

AVR Registers Summary

and Interrupt Vectors

UMSEL01 UMSEL00 UPM01 UPM00 USBS0 UCSZ01 UCSZ00 UCPOL0

UCSR0A RXC0 TXC0 UDRE0 FE0 DOR0 UPE0 U2X0 MPCM0 UCSZ0[2:0] Character Size

UCSR0B RXCIE0 TXCIE0 UDRIE0 RXEN0 TXEN0 UCSZ02 RXB80 TXB80 000 5

UCSR0C UMSEL01 UMSEL00 UPM01 UPM00 USBS0 UCSZ01 UCSZ00 UCPOL0 001 6

010 7

UBRR0H - - - - UBBR[11:8] 011 8

UBRR0L UBRR[7:0] 111 9

UDR0 (Read) RXB0[7:0] Number of

UDR0 (Write) TXB0[7:0] USBS0

Stop bits

0 1

1 2

Address Source Interrupt Definition

$024 USART_RX USART, Rx Complete

$026 USART_UDRE USART Data Register Empty

$028 USART_TX USART, Tx Complete End of lecture

Saad Arslan COMSATS INSTITUTE OF INFORMATION TECHNOLOGY, ISLAMABAD 17

You might also like

- Transistor Electronics: Use of Semiconductor Components in Switching OperationsFrom EverandTransistor Electronics: Use of Semiconductor Components in Switching OperationsRating: 1 out of 5 stars1/5 (1)

- Intel 8253 Programmable Timer GuideDocument9 pagesIntel 8253 Programmable Timer Guideroshi478No ratings yet

- Microchip MCP7940M Low Cost I2C Real Time Clock Calendar With SRAMDocument39 pagesMicrochip MCP7940M Low Cost I2C Real Time Clock Calendar With SRAM邱子威No ratings yet

- 128mbit SDRAM: 2M X 16bit X 4 Banks Synchronous DRAM LVTTLDocument11 pages128mbit SDRAM: 2M X 16bit X 4 Banks Synchronous DRAM LVTTLThiago Cristiano TavaresNo ratings yet

- Micrprocessors-AIN SHAMSDocument75 pagesMicrprocessors-AIN SHAMSjannatulishra.fourthNo ratings yet

- An 477Document28 pagesAn 477radaresNo ratings yet

- Rtos Course ProjectDocument20 pagesRtos Course Projecthammad choudharyNo ratings yet

- Ns16C552, Pc16552D: Pc16552D Dual Universal Asynchronous Receiver/Transmitter With FifosDocument24 pagesNs16C552, Pc16552D: Pc16552D Dual Universal Asynchronous Receiver/Transmitter With FifosNeimar HahmeierNo ratings yet

- Automatic Temperature ControllerDocument11 pagesAutomatic Temperature Controllerppksn0% (1)

- Microprocessor: Based, Multipurpose, ProgrammableDocument61 pagesMicroprocessor: Based, Multipurpose, ProgrammableSiddhant MittalNo ratings yet

- Ds1302 Datasheet PDFDocument14 pagesDs1302 Datasheet PDFarturoNo ratings yet

- Standard UART Data Word: Ideal State Ideal StateDocument10 pagesStandard UART Data Word: Ideal State Ideal StateVishad HatwarNo ratings yet

- Metal Detector Robot Controlled RemotelyDocument25 pagesMetal Detector Robot Controlled RemotelyDarshan ParmarNo ratings yet

- SCC2691 UART DatasheetDocument24 pagesSCC2691 UART DatasheetMstr BlinkyNo ratings yet

- 5.serial Communication - 1Document28 pages5.serial Communication - 1Dr-Samson ChepuriNo ratings yet

- Statistical analysis of key chapters for electronics engineering examsDocument57 pagesStatistical analysis of key chapters for electronics engineering examsshubhankar palNo ratings yet

- Slaa 115Document4 pagesSlaa 115api-3744762No ratings yet

- Interface Rs485Document13 pagesInterface Rs485jol1386100% (1)

- DS1302 Trickle Charge Timekeeping Chip: Features Pin AssignmentDocument14 pagesDS1302 Trickle Charge Timekeeping Chip: Features Pin AssignmentPedro PerezNo ratings yet

- Development Board For Stm8S003F3: by Nitin Chand M S (2018H1400171P), Rohith Krishnan P (2018H1400180P)Document13 pagesDevelopment Board For Stm8S003F3: by Nitin Chand M S (2018H1400171P), Rohith Krishnan P (2018H1400180P)Thông NguyễnNo ratings yet

- DS1302 Real-Time Clock Chip with 31-Byte RAMDocument16 pagesDS1302 Real-Time Clock Chip with 31-Byte RAMJuan Isaac Rodriquez MaldonadoNo ratings yet

- MSP430 DatasheetDocument32 pagesMSP430 DatasheetFilipe GalizaNo ratings yet

- Microprocessor and Systems Lab Electrical Engineering Uet Taxila Home AutomationDocument12 pagesMicroprocessor and Systems Lab Electrical Engineering Uet Taxila Home AutomationKashif HassanNo ratings yet

- DS1302Document15 pagesDS1302szetomsdNo ratings yet

- 8051 - Serial CommunicationDocument44 pages8051 - Serial CommunicationDr-Samson ChepuriNo ratings yet

- Tty To Rs232Document8 pagesTty To Rs232sandeepverma8257100% (2)

- LPC P2148Document19 pagesLPC P2148Sharath Babu100% (1)

- Micro Lab 6Document10 pagesMicro Lab 6Hacker YousafzaiNo ratings yet

- Casio FX9700GE PC Interface Circuit Electronics SerialDocument2 pagesCasio FX9700GE PC Interface Circuit Electronics Seriallakis lalakis888No ratings yet

- Serial Communications: ObjectivesDocument26 pagesSerial Communications: ObjectivesAmy OliverNo ratings yet

- DS1388Document19 pagesDS1388mar_barudjNo ratings yet

- GM16C550Document23 pagesGM16C550kranti06No ratings yet

- Arduino NoteDocument9 pagesArduino NoteMircea TirziuNo ratings yet

- MPSI Quiz2 SolutionDocument2 pagesMPSI Quiz2 SolutionIman HayatNo ratings yet

- 8-Bit Microcontroller With 2K/4K Bytes In-System Programmable Flash AT90S2333 AT90LS2333 AT90S4433 AT90LS4433 PreliminaryDocument103 pages8-Bit Microcontroller With 2K/4K Bytes In-System Programmable Flash AT90S2333 AT90LS2333 AT90S4433 AT90LS4433 Preliminaryapi-19831863No ratings yet

- 8051 Microcontroller Serial Communication: Doubling the Baud RateDocument15 pages8051 Microcontroller Serial Communication: Doubling the Baud RateRohan JainNo ratings yet

- Lab Serial Communication 8051Document3 pagesLab Serial Communication 8051khawar iqbalNo ratings yet

- UART Interfacing With ARM PrimerDocument13 pagesUART Interfacing With ARM PrimerSmruti PoreNo ratings yet

- UART Interfacing With 8051 PrimerDocument10 pagesUART Interfacing With 8051 PrimerNitesh JadhavNo ratings yet

- Intelligent Water Control System Using 8051 (AT89C51) : Project ReportDocument12 pagesIntelligent Water Control System Using 8051 (AT89C51) : Project ReportNadeem AnjumNo ratings yet

- Panasonic FP KWDocument15 pagesPanasonic FP KWLP MaxNo ratings yet

- Pic 16 F 628Document20 pagesPic 16 F 628Merényi Oszkár100% (1)

- EE-379 Embedded Systems and Applications: (Serial) BusesDocument40 pagesEE-379 Embedded Systems and Applications: (Serial) Busesss mNo ratings yet

- Pin No. Pin Name Description Alternate FunctionDocument7 pagesPin No. Pin Name Description Alternate FunctionnareshhhhhNo ratings yet

- Experiment No.: 5Document6 pagesExperiment No.: 5Dhrumil ManiyarNo ratings yet

- UC3848Document9 pagesUC3848Sergio Daniel BarretoNo ratings yet

- Embedded SystemsDocument12 pagesEmbedded SystemsAl-Amin BhuiyanNo ratings yet

- Time DelayDocument27 pagesTime DelayPrincipal GEC RajkotNo ratings yet

- D D D D D: DescriptionDocument39 pagesD D D D D: DescriptionAnonymous o4taPXTPLNo ratings yet

- Appkit:: Using The Ds1620 Digital Thermometer/ThermostatDocument26 pagesAppkit:: Using The Ds1620 Digital Thermometer/ThermostatMUHAMMAD SISWANTORONo ratings yet

- System Controllers: A Navya Vishnu 1210410304Document33 pagesSystem Controllers: A Navya Vishnu 1210410304Ananda KrishnaNo ratings yet

- MSP 430 G 2452Document63 pagesMSP 430 G 2452Đặng Quốc HuyNo ratings yet

- MX614 Packet ModemDocument3 pagesMX614 Packet ModemtivisNo ratings yet

- Ds92Lv16: Ds92Lv16 16-Bit Bus Lvds Serializer/Deserializer - 25 - 80 MHZDocument21 pagesDs92Lv16: Ds92Lv16 16-Bit Bus Lvds Serializer/Deserializer - 25 - 80 MHZlur46No ratings yet

- PROJECT USING MICROCONTROLLER ATMEGA16Document34 pagesPROJECT USING MICROCONTROLLER ATMEGA16KARTHIK S SNo ratings yet

- BLDC MainDocument24 pagesBLDC MainGeralt VesemirNo ratings yet

- DS1320Document13 pagesDS1320Annelise Grottker de OliveiraNo ratings yet

- LS7366 PulseCounter PDFDocument10 pagesLS7366 PulseCounter PDFJoan WascNo ratings yet

- Image Enhancement in Spatial DomainDocument43 pagesImage Enhancement in Spatial DomainMahreenNo ratings yet

- Image Enhancement in Frequency DomainDocument37 pagesImage Enhancement in Frequency DomainMahreenNo ratings yet

- Introduction Part Ii: Graphics in MatlabDocument16 pagesIntroduction Part Ii: Graphics in MatlabMahreenNo ratings yet

- Image Enhancement in Spatial Domain: Pixel Operations and Histogram ProcessingDocument59 pagesImage Enhancement in Spatial Domain: Pixel Operations and Histogram ProcessingMahreenNo ratings yet

- Introduction Part I: Basic Matlab StructureDocument28 pagesIntroduction Part I: Basic Matlab StructureMahreenNo ratings yet

- Image Enhancement in Frequency DomainDocument16 pagesImage Enhancement in Frequency DomainMahreenNo ratings yet

- PWM Programming and DC Motor Control: Lecture# 22Document15 pagesPWM Programming and DC Motor Control: Lecture# 22MahreenNo ratings yet

- FA21 - Lec24 - 2021-12-11 - SPI Programming in AVRDocument23 pagesFA21 - Lec24 - 2021-12-11 - SPI Programming in AVRMahreenNo ratings yet

- Introduction Part Iii: Programming in MatlabDocument12 pagesIntroduction Part Iii: Programming in MatlabMahreenNo ratings yet

- FA21 - Lec17 - 2021-11-10 - UART - Programming - Part 2Document17 pagesFA21 - Lec17 - 2021-11-10 - UART - Programming - Part 2MahreenNo ratings yet

- FA21 Lec25 2021-12-15 I2CDocument20 pagesFA21 Lec25 2021-12-15 I2CMahreenNo ratings yet

- Nternational Journal For Research in Electronics & Electrical Engineering ISSN: 2208-2735Document11 pagesNternational Journal For Research in Electronics & Electrical Engineering ISSN: 2208-2735MahreenNo ratings yet

- Timers and Microprocessor InterfacingDocument20 pagesTimers and Microprocessor InterfacingMahreenNo ratings yet

- FA21 - Lec23 - 2021-12-08 - PWM - Part2 and SPIDocument24 pagesFA21 - Lec23 - 2021-12-08 - PWM - Part2 and SPIMahreenNo ratings yet

- Adc Dac and Sensor Interfacing - Part 2Document14 pagesAdc Dac and Sensor Interfacing - Part 2MahreenNo ratings yet

- ADC DAC and Sensor Interfacing LECTURE# 19Document17 pagesADC DAC and Sensor Interfacing LECTURE# 19MahreenNo ratings yet

- Relay, Optoisolators and Stepper Motor LECTURE# 21Document27 pagesRelay, Optoisolators and Stepper Motor LECTURE# 21MahreenNo ratings yet

- AVR Programming in C - Bitwise OperationsDocument16 pagesAVR Programming in C - Bitwise OperationsMahreenNo ratings yet

- Interrupts: Lecture# 13 Microprocessor Systems and InterfacingDocument16 pagesInterrupts: Lecture# 13 Microprocessor Systems and InterfacingMahreenNo ratings yet

- Microprocessor Assembly Arithmetic, Logic and Programs LectureDocument18 pagesMicroprocessor Assembly Arithmetic, Logic and Programs LectureMahreenNo ratings yet

- FA21 - Lec15 - 2021-11-03 - Keypad InterfacingDocument20 pagesFA21 - Lec15 - 2021-11-03 - Keypad InterfacingMahreenNo ratings yet

- AVR I/O Port Programming: Lecture# 07 Microprocessor Systems and InterfacingDocument18 pagesAVR I/O Port Programming: Lecture# 07 Microprocessor Systems and InterfacingMahreenNo ratings yet

- LCD Interfacing: Lecture# 14 Microprocessor Systems and InterfacingDocument26 pagesLCD Interfacing: Lecture# 14 Microprocessor Systems and InterfacingMahreenNo ratings yet

- AVR Architecture and Assembly Language ProgrammingDocument17 pagesAVR Architecture and Assembly Language ProgrammingMahreenNo ratings yet

- FA21 - Lec08-2021-10-09 - AVR Programming in CDocument15 pagesFA21 - Lec08-2021-10-09 - AVR Programming in CMahreenNo ratings yet

- FA21 - Lec10-2021-10-16 - Arithmetic, Logic Instructions and ProgramsDocument15 pagesFA21 - Lec10-2021-10-16 - Arithmetic, Logic Instructions and ProgramsMahreenNo ratings yet

- FA21 - Lec04-2021-09-25 - RISC, Branching and LoopingDocument18 pagesFA21 - Lec04-2021-09-25 - RISC, Branching and LoopingMahreenNo ratings yet

- Timing & Pipelining: Lecture# 06 Microprocessor Systems and InterfacingDocument11 pagesTiming & Pipelining: Lecture# 06 Microprocessor Systems and InterfacingMahreenNo ratings yet

- FA21 - Lec05-2021-09-29 - CALL, Return and StackDocument32 pagesFA21 - Lec05-2021-09-29 - CALL, Return and StackMahreenNo ratings yet

- FFRTC LogDocument2,040 pagesFFRTC LogSNEYDER ZABALANo ratings yet

- Implenting Secure SSO With OpenSAMLDocument43 pagesImplenting Secure SSO With OpenSAMLsgsfak100% (1)

- R1 2016 2017 1 (Q+S) PDFDocument10 pagesR1 2016 2017 1 (Q+S) PDFmarwanNo ratings yet

- Sure Signal Premium - UK High Level Design v3.0Document80 pagesSure Signal Premium - UK High Level Design v3.0Hector SolarteNo ratings yet

- Acceptance Report - For Telecom SiteDocument16 pagesAcceptance Report - For Telecom Siteraviranjan1975No ratings yet

- CH - 8 Wsjuly11Document26 pagesCH - 8 Wsjuly11Abhinav DandareNo ratings yet

- Teletronik Optical EquipmentDocument20 pagesTeletronik Optical EquipmentosamaokokNo ratings yet

- HP Computer - WorkstationDocument23 pagesHP Computer - Workstationmathan_aeNo ratings yet

- WDM WokshopDocument26 pagesWDM Wokshopmohas92No ratings yet

- NGN Architecture - Final - July12Document11 pagesNGN Architecture - Final - July12jayasanthosh janakiNo ratings yet

- Converting Voice To Packets and Bandwidth CalculationDocument9 pagesConverting Voice To Packets and Bandwidth CalculationLinda J. EvansNo ratings yet

- Musthaq Original 2023Document4 pagesMusthaq Original 2023Musthaq ahamedNo ratings yet

- zNID-GPON-GE-6024T - DZSDocument4 pageszNID-GPON-GE-6024T - DZSKAREEEMNo ratings yet

- Leading Multi-Tech Radio Planning SoftwareDocument16 pagesLeading Multi-Tech Radio Planning SoftwarePatrick LofomboliNo ratings yet

- Configuring The Access Point For The First TimeDocument30 pagesConfiguring The Access Point For The First TimeYoussef AoufiNo ratings yet

- SMS BASED VOTING MACHINE Project ReportDocument71 pagesSMS BASED VOTING MACHINE Project ReportRahul Garg67% (6)

- Wulfsberg Product GuideDocument141 pagesWulfsberg Product GuideJeane MarquesNo ratings yet

- PIC24FJ128Document504 pagesPIC24FJ128rabeekNo ratings yet

- Communication Systems Course OutlineDocument34 pagesCommunication Systems Course OutlineIhsan ul HaqNo ratings yet

- Mpls l2vpn VLLDocument24 pagesMpls l2vpn VLLminhtuanqniNo ratings yet

- Introduction To IoT SyllabusDocument6 pagesIntroduction To IoT Syllabusayrakb2003No ratings yet

- Rs416 Installation GuideDocument43 pagesRs416 Installation GuidetedoNo ratings yet

- SimbaNET Malawi Overview 2016Document28 pagesSimbaNET Malawi Overview 2016Brian Munyao LongweNo ratings yet

- Cisco ESA Email Security Best FiltersDocument18 pagesCisco ESA Email Security Best Filtersluis_omar07No ratings yet

- CCNA 200-301 Drag and Drop Questions (By Passleader - Com)Document9 pagesCCNA 200-301 Drag and Drop Questions (By Passleader - Com)bikash_shrest5No ratings yet

- SRS485 Option Card For Lon Star Coupler RER 111: Technical Reference ManualDocument16 pagesSRS485 Option Card For Lon Star Coupler RER 111: Technical Reference ManualSarah FrazierNo ratings yet

- Swot of NOKIADocument3 pagesSwot of NOKIAynkamat75% (4)

- CN - WT Cse Lab ManualDocument195 pagesCN - WT Cse Lab ManualSahithi Priya AttiliNo ratings yet

- Satellite CommunicationsDocument17 pagesSatellite CommunicationsAreab DarwishNo ratings yet

- Acm Series Dual Stream 5616 V DVRDocument4 pagesAcm Series Dual Stream 5616 V DVRaditgroupNo ratings yet