Professional Documents

Culture Documents

Interrupts: Lecture# 13 Microprocessor Systems and Interfacing

Uploaded by

MahreenOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Interrupts: Lecture# 13 Microprocessor Systems and Interfacing

Uploaded by

MahreenCopyright:

Available Formats

Interrupts

LECTURE# 13

MICROPROCESSOR SYSTEMS AND INTERFACING

Saad Arslan COMSATS UNIVERSITY ISLAMABAD 1

Last Lecture

AVR Timers

◦ Timer0 Normal and CTC mode

◦ Timer2

◦ Timer1 theory only

◦ Using timers as counters

Saad Arslan COMSATS UNIVERSITY ISLAMABAD 2

What are interrupts

Is a signal (generated by hardware or software) to processor telling

◦ That an event needs attention

Allows μC/μP to effectively service multiple devices

There are two methods of servicing multiple devices

◦ Polling

◦ Keep polling/checking all the devices if any needs service

◦ Interrupts

◦ CPU performs normal routine

◦ if a device needs service, the control automatically transfers to service

Consider the timers

◦ TOV or OCF flag is polled continuously

◦ Keeps the CPU busy and CPU cannot perform any other task

Saad Arslan COMSATS UNIVERSITY ISLAMABAD 3

Interrupt Service Routine (ISR)

ISR is the service perform by the CPU

◦ in response to an interrupt call

◦ The service required by the device

◦ Example, what happens when timer overflow?

In our case

◦ ISR is a subroutine, executed only when particular interrupt occurs

Required by every interrupt that will be serviced

ISR is pointed by Interrupt Vector Table

Saad Arslan COMSATS UNIVERSITY ISLAMABAD 4

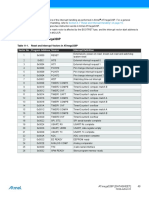

ATmega328

Interrupt Vector Table

Vector Program

Source Interrupt Definition

There can be multiple No. Address

External Pin, Power-on Reset, Brown-out Reset and

possible interrupts, like 1 0x0000 RESET

Watchdog System Reset

2 0x0002 INT0 External Interrupt Request 0

◦ Timer overflow or compare 3 0x0004 INT1 External Interrupt Request 1

4 0x0006 PCINT0 Pin Change Interrupt Request 0

match 5 0x0008 PCINT1 Pin Change Interrupt Request 1

6 0x000A PCINT2 Pin Change Interrupt Request 2

◦ Serial data received or 7 0x000C WDT Watchdog Time-out Interrupt

transmitted 8 0x000E TIMER2_COMPA Timer/Counter2 Compare Match A

9 0x0010 TIMER2_COMPB Timer/Counter2 Compare Match B

◦ Some pin changed on a port 10

11

0x0012

0x0014

TIMER2_OVF

TIMER1_CAPT

Timer/Counter2 Overflow

Timer/Counter1 Capture Event

◦ ADC conversion completed 12

13

0x0016

0x0018

TIMER1_COMPA

TIMER1_COMPB

Timer/Counter1 Compare Match A

Timer/Counter1 Compare Match B

◦ SPI, I2C 14

15

0x001A

0x001C

TIMER1_OVF

TIMER0_COMPA

Timer/Counter1 Overflow

Timer/Counter0 Compare Match A

16 0x001E TIMER0_COMPB Timer/Counter0 Compare Match B

Interrupt Vector Table points 17

18

0x0020

0x0022

TIMER0_OVF

SPI_STC

Timer/Counter0 Overflow

SPI Serial Transfer Complete

to specific ISR for a particular 19

20

0x0024

0x0026

USART_RX

USART_UDRE

USART Rx Complete

USART, Data Register Empty

interrupt 21 0x0028 USART_TX USART, Tx Complete

22 0x002A ADC ADC Conversion Complete

23 0x002C EE_READY EEPROM Ready

24 0x002E ANALOG_COMP Analog Comparator

25 0x0030 TWI 2-wire Serial Interface

26 0x0032 SPM_Ready Store Program Memory Ready

Saad Arslan COMSATS UNIVERSITY ISLAMABAD 6

Servicing an Interrupt

1. It finishes executing current instruction, and stores address of the next

instruction in stack (Like CALL)

2. It jumps to a fixed location in memory called the Interrupt Vector Table

a. Interrupt Vector Table points to the address of ISR

3. Microcontroller starts to execute ISR

a. until it reaches end, which is RETI (Return from Interrupt) instruction

4. Upon executing RETI, the microcontroller returns to the place where it was

interrupted

• POPs the address from stack and updates Program Counter (PC).

5. The microcontroller resumes the execution of Normal routine

(1)

Interrupt Signal (2)

Received

(3)

Main code Resume main Interrupt Service

execution code execution Routine Execution

(5)

(4)

Saad Arslan COMSATS UNIVERSITY ISLAMABAD 7

Enabling Interrupts

Bit 7 6 5 4 3 2 1 0

First Global Interrupt is enabled 0x3F (0x5F) I T H S V N Z C SREG

Read/Write R/W R/W R/W R/W R/W R/W R/W R/W

◦ Using I bit in SREG Initial Value 0 0 0 0 0 0 0 0

C – Carry flag S – Sign flag

◦ Enable using SEI, Z – Zero flag H – Half carry

◦ disable using CLI instruction N – Negative Flag T – Bit copy storage

V – Overflow flag I – Global interrupt enable

Then Particular Interrupt is enabled

◦ Some register contains bits for enabling particular interrupts

◦ Like TIMSKn shown here Bit 7 6 5 4 3 2 1 0

(0x6E) – – – – – OCIE0B OCIE0A TOIE0 TIMSK0

◦ Used for Timer 0, 1 & 2 Interrupts

(0x6F) – – ICIE1 – – OCIE1B OCIE1A TOIE1 TIMSK1

(0x70) – – – – – OCIE2B OCIE2A TOIE2 TIMSK2

Saad Arslan COMSATS UNIVERSITY ISLAMABAD 8

Programming Interrupts

Write Assembly program to use Timer0 Overflow interrupt

What happens when timer overflows?

◦ How is it utilized? Interrupt Vector Table?

Saad Arslan COMSATS UNIVERSITY ISLAMABAD 9

ATmega328 Timer0 Normal Mode

using Polling and Interrupt (cont.)

.ORG 0x00; location for reset

LDI R16, 1<<5 ;R16 = 0b0010 0000 RJMP MAIN

SBI DDRB, 5 ;PB5 as an output .ORG 0x20; location of Timer0 overflow TIMER0_OVF

LDI R17, 0 RJMP TOV0_ISR

OUT PORTB, R17 ;clear PORTB polling MAIN:

Interrupts

BEGIN:RCALL DELAY ;call timer delay LDI R16, 1<<5 ;R16 = 0b0010 0000

EOR R17, R16 ;toggle D5 of R1 SBI DDRB, 5 ;PB5 as an output

OUT PORTB, R17 ;toggle PB5 LDI R17, 0

RJMP BEGIN OUT PORTB, R17 ;clear PORTB

;-------------------------------Timer0 delay LDI R20, 0xF2 ;R20 = 0xF2

DELAY:LDI R20, 0xF2 ;R20 = 0xF2 OUT TCNT0, R20 ;load timer0

OUT TCNT0, R20 ;load timer0 LDI R20, 0x00

LDI R20, 0x00 OUT TCCR0A, R20 ;Tim0 Normal mode

OUT TCCR0A, R20 ;Tim0 Normal mode LDI R20, 0x01

LDI R20, 0x01 OUT TCCR0B, R20 ;Tim0 Normal mode, int clk

OUT TCCR0B, R20 ;Tim0 Normal mode, int clk LDI R18, 0x01

AGAIN:IN R20, TIFR0 ;read TIFR STS TIMSK0, R18 ; enable tim0 OVF interrupt

SBRS R20, TOV0 ;if TOV0=1,skip nxt inst. SEI ;enable global interrupt

RJMP AGAIN HERE: RJMP HERE

LDI R20, 0x0 .ORG 0x200

OUT TCCR0B, R20 ;stop Timer0 TOV0_ISR:

LDI R20, (1<<TOV0) EOR R17, R16 ;toggle D5 of R1

OUT TIFR0, R20 ;clear TOV0 flag OUT PORTB, R17 ;toggle PB5

RET LDI R20, 0xF2;R20 = 0xF2

OUT TCNT0, R20 ;load timer0

RETI

Saad Arslan COMSATS UNIVERSITY ISLAMABAD 11

ATmega328 Timer0 CTC mode

Using Polling and Interrupt

LDI R16, 0x08 .ORG 0x00; location for reset

SBI DDRB, 3 ;PB3 as an output RJMP MAIN

LDI R17, 0 polling .ORG 0x1C ; loc. of Timer0 Comp. Match A - OCF0A

BEGIN: OUT PORTB, R17 ;PORTB = R17

RCALLDELAY MAIN:

RJMP OCF0A_ISR Interrupts

EOR R17, R16 ;toggle D3 of R17 LDI R16, 1<<5 ;R16 = 0b0010 0000

RJMPBEGIN SBI DDRB, 5 ;PB5 as an output

;------------------- Timer0 Delay LDI R17, 0

DELAY: LDI R20, 0 OUT PORTB, R17 ;clear PORTB

OUT TCNT0, R20 LDI R20, 0;R20 = 0xF2

LDI R20, 9 OUT TCNT0, R20 ;load timer0

OUT OCR0A, R20 ;load OCR0 LDI R20, 9

LDI R20, 0x02 OUT OCR0A, R20 ;load OCR0A

OUT TCCR0A, R20 ;Timer0, CTC mode LDI R20, 0x02

LDI R20, 0x01 OUT TCCR0A, R20 ;Timer0, CTC mode

OUT TCCR0B, R20 ;Timer0, CTC mode,int clk LDI R20, 0x01

AGAIN: IN R20, TIFR0 ;read TIFR OUT TCCR0B, R20 ;Timer0, CTC mode,int clk

SBRS R20, OCF0A ; skip nxt inst. If OCF=1 LDI R18, 0x02

RJMP AGAIN STS TIMSK0, R18 ;Enable Tim0 OCF0A interrupt

LDI R20, 0x0 SEI ;enable global interrupt

OUT TCCR0B, R20 ;stop Timer0 HERE: RJMP HERE

LDI R20, 1<<OCF0A .ORG 0x200

OUT TIFR0, R20 ;clear OCF0 flag OCF0A_ISR:

HERE: RJMP HERE EOR R17, R16 ;toggle D5 of R1

OUT PORTB, R17 ;toggle PB5

RETI

Saad Arslan COMSATS UNIVERSITY ISLAMABAD 13

RETI and RET

Whenever the CPU starts to execute an ISR

◦ It disables global interrupt (clears I flag in SREG)

◦ But, why?

◦ So that no other source interrupts the CPU

Both (RET and RETI) return to address popped from stack

RETI performs an additional task of setting I flag

◦ I flag is cleared when interrupt occurs

◦ To block new interrupts while servicing one

Saad Arslan COMSATS UNIVERSITY ISLAMABAD 14

External Interrupts

ATmega328

ATmega328p has two dedicated external hardware interrupts

◦ External Interrupt 0 and 1 (INT0 & INT1)

For polling flags, use

◦ Generate interrupt INT0 or INT1, when • EIFR register for INT0 to INT1

◦ Low-level (ISCnx = 00) • PCIFR register for PCINT[23:0]

◦ Falling and rising edge (ISCnx = 01)

◦ Falling edge (ISCnx = 10)

(PCINT14/RESET) PC6 1 28 PC5 (ADC5/SCL/PCINT13)

◦ Rising edge (ISCnx = 11) (PCINT16/RXD) PD0 2 27 PC4 (ADC4/SDA/PCINT12)

◦ Using EICRA register (PCINT17/TXD) PD1 3 26 PC3 (ADC3/PCINT11)

(PCINT18/INT0) PD2 4 25 PC2 (ADC2/PCINT10)

◦ Enable INT1 and/or INT2 in EIMSK register (PCINT19/OC2B/INT1) PD3 5 24 PC1 (ADC1/PCINT9)

(PCINT20/XCK/T0) PD4 6 23 PC0 (ADC0/PCINT8)

◦ Also have three shared interrupts VCC 7 22 GND

GND 8 21 AREF

◦ PCINT[23:16], PCINT[14:8], & PCINT[7:0] (PCINT6/XTAL1/TOSC1) PB6 9 20 AVCC

(PCINT7/XTAL2/TOSC2) PB7 10 19 PB5 (SCK/PCINT5)

◦ Enable through PCICR register (PCINT21/OC0B/T1) PD5 11 18 PB4 (MISO/PCINT4)

◦ Containing PCIE2:0 bits for each interrupt (PCINT22/OC0A/AIN0) PD6 12 17 PB3 (MOSI/OC2A/PCINT3)

(PCINT23/AIN1) PD7 13 16 PB2 (SS/OC1B/PCINT2)

◦ Enable interrupt pins (PCINT0/CLKO/ICP1) PB0 14 15 PB1 (OC1A/PCINT1)

◦ using PCMSK0,1,2 registers

Saad Arslan COMSATS UNIVERSITY ISLAMABAD 16

External Interrupts cont.

INT0 and 1 are enabled by respective bits in EIMSK

◦ EIMSK

INT0 and 1 are configured using

◦ EICRA ISC11 ISC10 ISC01 ISC00

Like TOV0, OCF0 flags, there are INTF0 and INTF1 in EIFR

◦ EIFR

◦ When an external interrupt is generated

◦ The corresponding flag is set

◦ If polling, the flag is manual cleared by writing 1 to it

◦ Means either no external interrupt is enable in EICR or global interrupt is disabled

◦ When using interrupts, the flag is automatically cleared

Saad Arslan COMSATS UNIVERSITY ISLAMABAD 18

External Interrupts cont.

Pin Change Interrupt

◦ Enable using

◦ Flag Register

◦ Interrupt enable on individual pins using

Saad Arslan COMSATS UNIVERSITY ISLAMABAD 19

Interrupt Priority

If two or more interrupts are activated at the same time

◦ The interrupt with higher priority is served first

The address in the Interrupt Vector Table define priorities

◦ Lower addresses have higher priority compared to higher addresses

When an interrupt is being served (ISR being executed)

◦ Any other interrupt activated at that time will not be served

◦ Even if the new interrupt activated has higher priority

◦ The new interrupt will be served after the current ISR is completed

◦ This is because global interrupt is disabled while executing an interrupt

You can manually enable global interrupt in an ISR

◦ To serve new interrupts, but may cause infinite loop

◦ For example, when low-level triggered interrupt is used

Saad Arslan COMSATS UNIVERSITY ISLAMABAD 20

Context saving in multitasking

.INCLUDE "M32DEF.INC"

When multi-tasking, like interrupts .ORG 0x00

JMP MAIN

;location for reset

◦ Resources (registers and status flags) .ORG 0x14 ;location for TimerO compare match

should be managed carefully .ORG 0x100

JMP T0_CM_ISR

;-main program for initialization and keeping CPU busy

MAIN: LDI R20, HIGH(RAMEND)

Resource conflicts can occur OUT

LDI

SPH, R20

R20, LOW(RAMEND)

◦ When main program and ISR uses OUT

SBI

SPL, R20

DDRB, 5

;set up stack

;PB5 as an output

◦ Same registers or status flags LDI R20, (1<<OCIE0)

OUT TIMSK, R20 ;enable Timer0 compare match interrupt

SEI ;set I (enable interrupts globally)

Consider Program 10-4 LDI R20, 160

OUT OCR0, R20 ;load Timer0 with 160

◦ Main program increments R20 LDI R20, 0x09

OUT TCCR0, R20 ;CTC mode, int clk, no prescaler

◦ And write it to PORTC LDI R20, 0xFF

OUT DDRC, R20 ;make PORTC output

◦ ISR copies PIND To R20 increments it OUT DDRD, R20 ;make PORTD output

and writes it to PORTD LDI R20, 0

HERE: OUT PORTC, R20 ;PORTC = R20

◦ Do you see an issue here? INC R20

JMP HERE ;keeping CPU busy waiting for interrupt

.ORG 0x200

So, conflicting resources are copied T0_CM_ISR:

IN R20, PIND

ISR for Timer0 Compare Match

and restored INC R20

OUT PORTD, R20 ;PORTD = R20

RETI ;return from interrupt

Saad Arslan COMSATS UNIVERSITY ISLAMABAD 21

You might also like

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet

- Exercises in Electronics: Operational Amplifier CircuitsFrom EverandExercises in Electronics: Operational Amplifier CircuitsRating: 3 out of 5 stars3/5 (1)

- Interrupts: 11.1 Interrupt Vectors in Atmega328PDocument1 pageInterrupts: 11.1 Interrupt Vectors in Atmega328PnamerNo ratings yet

- 4 Experiment 4 Interrupt and I/O InterfacingDocument17 pages4 Experiment 4 Interrupt and I/O InterfacingSuhas NipaneNo ratings yet

- 10 ATmega328P InterruptsDocument17 pages10 ATmega328P InterruptsJarfoNo ratings yet

- Lecture 7 - AVR Interrupt ProgrammingDocument26 pagesLecture 7 - AVR Interrupt Programmingmminhdoan2203No ratings yet

- Ch10 AVR Interrupt ProgrammingDocument23 pagesCh10 AVR Interrupt ProgrammingWarforce Rox100% (1)

- Ch11 AVR Serial Port ProgrammingDocument25 pagesCh11 AVR Serial Port ProgrammingSimple knowledgeNo ratings yet

- Embedded Systems - Lec 4 - InterruptsDocument29 pagesEmbedded Systems - Lec 4 - InterruptsIslam Abd ElhadlyNo ratings yet

- Topic 11 - ATMega32 Interrupt in C (ISMAIL - FKEUTM 2018)Document60 pagesTopic 11 - ATMega32 Interrupt in C (ISMAIL - FKEUTM 2018)Aya AmirNo ratings yet

- Programable Elements I InterruptsDocument17 pagesProgramable Elements I InterruptsOliver Ochoa GarciaNo ratings yet

- Unit 4 - Microprocessor & Its Application - WWW - Rgpvnotes.inDocument9 pagesUnit 4 - Microprocessor & Its Application - WWW - Rgpvnotes.inJayesh JoshiNo ratings yet

- Avr Atmega128 Interrupts Cheat-SheetDocument14 pagesAvr Atmega128 Interrupts Cheat-SheetNick TarasNo ratings yet

- FA21 Lec16 2021-11-06 UART ProgrammingDocument17 pagesFA21 Lec16 2021-11-06 UART ProgrammingMahreenNo ratings yet

- MPSI Quiz2 SolutionDocument2 pagesMPSI Quiz2 SolutionIman HayatNo ratings yet

- Electronics-Communication Engineering Embedded-Systems Timers NotesDocument17 pagesElectronics-Communication Engineering Embedded-Systems Timers NotesSSSSSSSSSSSSNo ratings yet

- Government Engineering College, GandhinagarDocument8 pagesGovernment Engineering College, GandhinagarDhrumil ManiyarNo ratings yet

- Interrupt Numbers and NVIC RegistersDocument15 pagesInterrupt Numbers and NVIC Registerspotato moon berryNo ratings yet

- Unit2-Timer & InterruptDocument47 pagesUnit2-Timer & Interruptmanikandan trNo ratings yet

- Avr Tutorials - Com AVR Microcontroller InterruptsDocument4 pagesAvr Tutorials - Com AVR Microcontroller InterruptsMohamed AshrafNo ratings yet

- GPIO Interrupt Example CodeDocument9 pagesGPIO Interrupt Example Codepotato moon berryNo ratings yet

- PCF8523Document14 pagesPCF8523Cosmin AndreiNo ratings yet

- MPS - Ch10 - AVR - Interrupt Programming in Assembly and CDocument83 pagesMPS - Ch10 - AVR - Interrupt Programming in Assembly and CPhương Nghi LiênNo ratings yet

- 05 AVR Timer-Counter AVRDocument95 pages05 AVR Timer-Counter AVRPriscillaNo ratings yet

- Pin No. Pin Name Description Alternate FunctionDocument7 pagesPin No. Pin Name Description Alternate FunctionnareshhhhhNo ratings yet

- EEE 342 09 Timer 8254Document33 pagesEEE 342 09 Timer 8254Hafiz Adil AsrarNo ratings yet

- Isa - Timerg CBUS: 0x2666Document3 pagesIsa - Timerg CBUS: 0x2666asdasdasfli.elkinNo ratings yet

- 8051 Interrupts and Interfacing Applications: Module - 5Document26 pages8051 Interrupts and Interfacing Applications: Module - 5Pate VishnuNo ratings yet

- 5 InterruptsDocument9 pages5 InterruptsTam PhamNo ratings yet

- GUI LPC2103 Cau Trúc Phàn C NGDocument104 pagesGUI LPC2103 Cau Trúc Phàn C NGBắc HoàiNo ratings yet

- Intel 8254 TimerDocument18 pagesIntel 8254 Timermohitsingh316No ratings yet

- Ee3954 Fall13 08 InterruptsDocument44 pagesEe3954 Fall13 08 InterruptsHeart StopperNo ratings yet

- Avr ArchitectureDocument29 pagesAvr ArchitectureOdoch HerbertNo ratings yet

- Apuntes de Clase PICDocument117 pagesApuntes de Clase PICJonathan FranNo ratings yet

- Experiment No.: 6: To Implement Timer and Counter Programming For Avr Atmega32Document9 pagesExperiment No.: 6: To Implement Timer and Counter Programming For Avr Atmega32Dhrumil ManiyarNo ratings yet

- WelcomeDocument58 pagesWelcomeSatya VenkatNo ratings yet

- PIC24FJ64GA002 Interrupt VectorsDocument10 pagesPIC24FJ64GA002 Interrupt Vectorsocelot_and_allNo ratings yet

- Introduction To MSP430 MicrocontrollersDocument32 pagesIntroduction To MSP430 MicrocontrollersAlejandro OrtizNo ratings yet

- VCV CXB CCNBFVBFCGXC VNVCN Vcnxdcvnxbcfhbxddsafcdsvfgsadgvbzfshfscxvbxbvxzsdsafgdshgf VNBVNVNVNBDocument8 pagesVCV CXB CCNBFVBFCGXC VNVCN Vcnxdcvnxbcfhbxddsafcdsvfgsadgvbzfshfscxvbxbvxzsdsafgdshgf VNBVNVNVNBnareshhhhhNo ratings yet

- Sdsafgdshgfvnbvnvnvnb: Description Alternate FunctionDocument8 pagesSdsafgdshgfvnbvnvnvnb: Description Alternate FunctionnareshhhhhNo ratings yet

- Interrupts: Interrupt VectorDocument2 pagesInterrupts: Interrupt VectoranharNo ratings yet

- Module - III (A&B)Document80 pagesModule - III (A&B)PamusainagaharshavardhanNo ratings yet

- XC VNVCN Vcnxdcvnxbcfhbxddsafcdsvfgsadgvbzfshfscxvbxbvxzsdsafgdshgf VNBVNVNVNBDocument8 pagesXC VNVCN Vcnxdcvnxbcfhbxddsafcdsvfgsadgvbzfshfscxvbxbvxzsdsafgdshgf VNBVNVNVNBnareshhhhhNo ratings yet

- Microcontrollers LabDocument19 pagesMicrocontrollers LabAMARNATHNAIDU77No ratings yet

- Xddsafcdsvfgsadgvbzfshfscxvbxbvxzsdsafgdshgfvnbvnvnvn B: Descriptio N Alternate FunctionDocument8 pagesXddsafcdsvfgsadgvbzfshfscxvbxbvxzsdsafgdshgfvnbvnvnvn B: Descriptio N Alternate FunctionnareshhhhhNo ratings yet

- Description Alternate Function: SFDFDGFBGFDocument8 pagesDescription Alternate Function: SFDFDGFBGFnareshhhhhNo ratings yet

- DS1286 Watchdog Timekeeper: Features Pin AssignmentDocument13 pagesDS1286 Watchdog Timekeeper: Features Pin Assignmentjose goncalvesNo ratings yet

- 6 AncmpDocument18 pages6 AncmpNick TarasNo ratings yet

- Adc PWMDocument26 pagesAdc PWMShivaram Reddy ManchireddyNo ratings yet

- ES Exp 10Document13 pagesES Exp 10Maryam TariqNo ratings yet

- Time DelayDocument27 pagesTime DelayPrincipal GEC RajkotNo ratings yet

- L12 Timer Functions PDFDocument18 pagesL12 Timer Functions PDFAhmed M H Al-YousifNo ratings yet

- Module 4 Embedded SystemsDocument51 pagesModule 4 Embedded SystemsnpottiNo ratings yet

- AVR091 Replacing AT90S2313 by ATtiny2313Document8 pagesAVR091 Replacing AT90S2313 by ATtiny2313NIKOLAOS NANNOSNo ratings yet

- Timers of ATmega328PDocument26 pagesTimers of ATmega328PZaryab Khalil SiddiqueNo ratings yet

- 10 Interrupt v22Document29 pages10 Interrupt v22Pipat NakasenoNo ratings yet

- AVR 133: Long Delay Generation Using The AVR MicrocontrollerDocument8 pagesAVR 133: Long Delay Generation Using The AVR MicrocontrollernicoletabytaxNo ratings yet

- 8254 AnniDocument43 pages8254 AnniCSE7 NDUBNo ratings yet

- Lecture 7Document48 pagesLecture 7tecleador1No ratings yet

- Microprocessor Architectures and Systems: RISC, CISC and DSPFrom EverandMicroprocessor Architectures and Systems: RISC, CISC and DSPRating: 4 out of 5 stars4/5 (1)

- Image Enhancement in Frequency DomainDocument37 pagesImage Enhancement in Frequency DomainMahreenNo ratings yet

- Introduction Part I: Basic Matlab StructureDocument28 pagesIntroduction Part I: Basic Matlab StructureMahreenNo ratings yet

- Image Enhancement in Spatial Domain: Pixel Operations and Histogram ProcessingDocument59 pagesImage Enhancement in Spatial Domain: Pixel Operations and Histogram ProcessingMahreenNo ratings yet

- Nternational Journal For Research in Electronics & Electrical Engineering ISSN: 2208-2735Document11 pagesNternational Journal For Research in Electronics & Electrical Engineering ISSN: 2208-2735MahreenNo ratings yet

- Image Enhancement in Frequency DomainDocument16 pagesImage Enhancement in Frequency DomainMahreenNo ratings yet

- Image Enhancement in Spatial DomainDocument43 pagesImage Enhancement in Spatial DomainMahreenNo ratings yet

- Introduction Part Ii: Graphics in MatlabDocument16 pagesIntroduction Part Ii: Graphics in MatlabMahreenNo ratings yet

- FA21 - Lec21 - 2021-12-01 - Relay, Optoisolators and Stepper MotorDocument27 pagesFA21 - Lec21 - 2021-12-01 - Relay, Optoisolators and Stepper MotorMahreenNo ratings yet

- Introduction Part Iii: Programming in MatlabDocument12 pagesIntroduction Part Iii: Programming in MatlabMahreenNo ratings yet

- PWM Programming and DC Motor Control: Lecture# 22Document15 pagesPWM Programming and DC Motor Control: Lecture# 22MahreenNo ratings yet

- Adc Dac and Sensor Interfacing - Part 2Document14 pagesAdc Dac and Sensor Interfacing - Part 2MahreenNo ratings yet

- FA21 - Lec23 - 2021-12-08 - PWM - Part2 and SPIDocument24 pagesFA21 - Lec23 - 2021-12-08 - PWM - Part2 and SPIMahreenNo ratings yet

- FA21 Lec25 2021-12-15 I2CDocument20 pagesFA21 Lec25 2021-12-15 I2CMahreenNo ratings yet

- FA21 - Lec24 - 2021-12-11 - SPI Programming in AVRDocument23 pagesFA21 - Lec24 - 2021-12-11 - SPI Programming in AVRMahreenNo ratings yet

- Timers: Lecture# 12 Microprocessor Systems and InterfacingDocument20 pagesTimers: Lecture# 12 Microprocessor Systems and InterfacingMahreenNo ratings yet

- FA21 - Lec15 - 2021-11-03 - Keypad InterfacingDocument20 pagesFA21 - Lec15 - 2021-11-03 - Keypad InterfacingMahreenNo ratings yet

- LCD Interfacing: Lecture# 14 Microprocessor Systems and InterfacingDocument26 pagesLCD Interfacing: Lecture# 14 Microprocessor Systems and InterfacingMahreenNo ratings yet

- Adc Dac and Sensor InterfacingDocument17 pagesAdc Dac and Sensor InterfacingMahreenNo ratings yet

- FA21 - Lec11-2021-10-20 - Arithmetic, Logic Instructions and Programs - ContDocument18 pagesFA21 - Lec11-2021-10-20 - Arithmetic, Logic Instructions and Programs - ContMahreenNo ratings yet

- FA21 Lec16 2021-11-06 UART ProgrammingDocument17 pagesFA21 Lec16 2021-11-06 UART ProgrammingMahreenNo ratings yet

- AVR I/O Port Programming: Lecture# 07 Microprocessor Systems and InterfacingDocument18 pagesAVR I/O Port Programming: Lecture# 07 Microprocessor Systems and InterfacingMahreenNo ratings yet

- FA21 - Lec17 - 2021-11-10 - UART - Programming - Part 2Document17 pagesFA21 - Lec17 - 2021-11-10 - UART - Programming - Part 2MahreenNo ratings yet

- FA21 - Lec04-2021-09-25 - RISC, Branching and LoopingDocument18 pagesFA21 - Lec04-2021-09-25 - RISC, Branching and LoopingMahreenNo ratings yet

- FA21 - Lec08-2021-10-09 - AVR Programming in CDocument15 pagesFA21 - Lec08-2021-10-09 - AVR Programming in CMahreenNo ratings yet

- Timing & Pipelining: Lecture# 06 Microprocessor Systems and InterfacingDocument11 pagesTiming & Pipelining: Lecture# 06 Microprocessor Systems and InterfacingMahreenNo ratings yet

- FA21 - Lec03-2021 - 09 - 22 - AVR Architecture and Programming - 2Document17 pagesFA21 - Lec03-2021 - 09 - 22 - AVR Architecture and Programming - 2MahreenNo ratings yet

- AVR Programming in C - Continued: Lecture# 09 Microprocessor Systems and InterfacingDocument16 pagesAVR Programming in C - Continued: Lecture# 09 Microprocessor Systems and InterfacingMahreenNo ratings yet

- FA21 - Lec10-2021-10-16 - Arithmetic, Logic Instructions and ProgramsDocument15 pagesFA21 - Lec10-2021-10-16 - Arithmetic, Logic Instructions and ProgramsMahreenNo ratings yet

- FA21 - Lec05-2021-09-29 - CALL, Return and StackDocument32 pagesFA21 - Lec05-2021-09-29 - CALL, Return and StackMahreenNo ratings yet

- FA21 - Lec02-2021-09-16 - AVR Architecture and ProgrammingDocument16 pagesFA21 - Lec02-2021-09-16 - AVR Architecture and ProgrammingMahreenNo ratings yet

- Experiment 1: Naman Goyal 14-06-2022 Cse Subject Name: 20ECP-156BDocument10 pagesExperiment 1: Naman Goyal 14-06-2022 Cse Subject Name: 20ECP-156BNamanNo ratings yet

- (International English Language Testing System) : Learning Aims IELTS (CEF B2 - C2)Document4 pages(International English Language Testing System) : Learning Aims IELTS (CEF B2 - C2)Muraru RalucaNo ratings yet

- The Lion Witch and Wardrobe Unit PlanDocument47 pagesThe Lion Witch and Wardrobe Unit PlanKATHERINE GIOVANNA IGLESIAS PEREZ75% (4)

- Handout 2.1 Early - Literacy - and - Beginning - To - ReadDocument6 pagesHandout 2.1 Early - Literacy - and - Beginning - To - ReadShagufta MoghalNo ratings yet

- Presentation Tweet - 140 Ways To Present With ImpactDocument22 pagesPresentation Tweet - 140 Ways To Present With Impactstoma2005No ratings yet

- Sage 100 ERP Custom Office SpecDocument2 pagesSage 100 ERP Custom Office SpecBrian RiceNo ratings yet

- Chandrakala - Newar Presentation Jan 29 2016Document29 pagesChandrakala - Newar Presentation Jan 29 2016KabitagosthiNo ratings yet

- Al-Farabi and The Reconciliation of Plato and AristotleDocument11 pagesAl-Farabi and The Reconciliation of Plato and AristotlejanmalolepszyNo ratings yet

- Franke - The Good Shepherd Antef PDFDocument28 pagesFranke - The Good Shepherd Antef PDFImhotep72No ratings yet

- First Grade Math Lesson - MoneyDocument7 pagesFirst Grade Math Lesson - Moneyapi-383249099No ratings yet

- Technical Note: e MMC™ Linux EnablementDocument8 pagesTechnical Note: e MMC™ Linux Enablementkarz03160No ratings yet

- Attendance EagleDocument8 pagesAttendance EagleDario De la CruzNo ratings yet

- Sequential Function ChartDocument26 pagesSequential Function ChartOswaldo Rojas GoveaNo ratings yet

- Socratic Seminar Questions - Parts 3 and 4Document3 pagesSocratic Seminar Questions - Parts 3 and 4James HollomanNo ratings yet

- Ba 2 Year FC Hindi Language and Moral Valuesenglish Language y 241 Apr 2021Document2 pagesBa 2 Year FC Hindi Language and Moral Valuesenglish Language y 241 Apr 2021Vikash RaghuwanshiNo ratings yet

- Auto2000 Samarinda PDFDocument25 pagesAuto2000 Samarinda PDFfitriyadiwmpNo ratings yet

- Ericsson Consono MD110 PBX CSA EL7 TCP-IP VM IntegrationDocument26 pagesEricsson Consono MD110 PBX CSA EL7 TCP-IP VM IntegrationAshraf KaraymehNo ratings yet

- Passive VoiceDocument3 pagesPassive Voiceanon_805613190No ratings yet

- Europass CVDocument2 pagesEuropass CVMatjaž PečanNo ratings yet

- 1 s2.0 S0889490605000530 MainDocument4 pages1 s2.0 S0889490605000530 Main邱琦No ratings yet

- LCMDocument100 pagesLCMANSHUMAN MISHRANo ratings yet

- Readings Philosophy of Mind 2017-18Document4 pagesReadings Philosophy of Mind 2017-18suraj kumarNo ratings yet

- Product Line AccountingDocument37 pagesProduct Line AccountingMiguel Felicio100% (1)

- Kristiani Mita Natalia 044657974 Tugas Tutorial 1 Mkwi4201Document4 pagesKristiani Mita Natalia 044657974 Tugas Tutorial 1 Mkwi4201Kristiani Mita NataliaNo ratings yet

- Modeling of Seismic Isolators in Software ProgramsDocument20 pagesModeling of Seismic Isolators in Software ProgramsSkerdi MucoNo ratings yet

- 6 Review - Exercises - 2022Document8 pages6 Review - Exercises - 2022Nghi PhuongNo ratings yet

- Le Futur Simple: The Simple Future Tense What WILL Happen in The FutureDocument14 pagesLe Futur Simple: The Simple Future Tense What WILL Happen in The FutureAshar Ardhi EriyadiNo ratings yet

- Humss12e g1 NDocument50 pagesHumss12e g1 NKatherine AliceNo ratings yet

- B.inggris Kelas IxDocument6 pagesB.inggris Kelas IxKlinem NullNo ratings yet

- EDU726 Week 2 Self-Assessment Checklist For Online Facilitation 2022 - 2Document1 pageEDU726 Week 2 Self-Assessment Checklist For Online Facilitation 2022 - 2Oluwatobi AkindeNo ratings yet