Professional Documents

Culture Documents

Unit - 1: Number Systems: Number System Base (B) Digits

Unit - 1: Number Systems: Number System Base (B) Digits

Uploaded by

sai bOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Unit - 1: Number Systems: Number System Base (B) Digits

Unit - 1: Number Systems: Number System Base (B) Digits

Uploaded by

sai bCopyright:

Available Formats

Digital Logic Circuit

UNIT - 1: NUMBER SYSTEMS

1. A number system with base „b‟ will have „b‟ different digits from 0 to (b-1)

2.

Number System Base (b) Digits

Binary 2 0,1

Octal 8 0, 1, 2, 3, 4, 5, 6, 7

Decimal 10 0, 1, 2, 3, 4, 5, 6, 7, 8, 9

Hexadecimal 16 0, 1, 2, 3, 4, 5, 6, 7, 8, 9,

A, B, C, D, E, F.

3.

Decimal Hexadecimal Binary

0 0 0000

1 1 0001

2 2 0010

3 3 0011

4 4 0100

5 5 0101

6 6 0110

7 7 0111

8 8 1000

9 9 1001

10 A 1010

11 B 1011

12 C 1100

13 D 1101

14 E 1110

15 F 1111

#62, Rakame Complex, Periyar Bus Stand, Madurai-11 | 7373007731 | www.maduracoaching.com

12

Digital Logic Circuit

4. 4 bits = 1 nibble

8 bits = 1 Byte

5. Binary coded decimal code (BCD)

(i) In 4 bit binary formats

Possible representation = 24 = 16

Valid BCD codes = 10

Invalid BCD codes = 6

(ii) In 8 bit binary formats possible representation = 28

Valid BCD codes = 100

Invalid BCD codes = 156

6. Largest number that can be represented by using N bits = (2N − 1)10

UNIT – 2: LOGIC GATES

I/P O/P

1. NOT gate

A Y=A

0 1

1 0

I/P O/P

2. AND gate A B Y = AB

0 0 0

0 1 0

1 0 0

1 1 1

3. OR gate I/P O/P

A B Y = A+B

0 0 0

0 1 1

1 0 1

1 1 1

#62, Rakame Complex, Periyar Bus Stand, Madurai-11 | 7373007731 | www.maduracoaching.com

13

Digital Logic Circuit

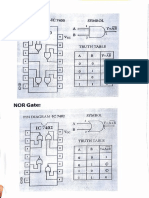

4. NAND gate

I/P O/P

A B Y = AB

0 0 1

0 1 1

1 0 1

1 1 0

5. NOR gate I/P O/P

A B Y= A + B

0 0 1

0 1 0

1 0 0

1 1 0

6. EX-OR gate I/P O/P

A B Y=A⊕B

0 0 0

0 1 1

1 0 1

1 1 0

7. EX-NOR gate I/P O/P

A B Y = A⊙B

0 0 1

0 1 0

1 0 0

1 1 1

8.

No of NAND No of NOR gate

Logic Gates

gate required required

NOT 1 1

AND 2 3

OR 3 2

EX-OR 4 5

EX-NOR 5 4

#62, Rakame Complex, Periyar Bus Stand, Madurai-11 | 7373007731 | www.maduracoaching.com

14

Digital Logic Circuit

UNIT - 3: BOOLEAN ALGEBRA

1) Commutative law: 𝐴 + 𝐵 = 𝐵 + 𝐴

𝐴 .𝐵 = 𝐵 .𝐴

2) Associative law: 𝐴 + (𝐵 + 𝐶) = (𝐴 + 𝐵) + 𝐶 = 𝐴 + 𝐵 + 𝐶

𝐴. (𝐵 . 𝐶) = (𝐴 . 𝐵)𝐶 = 𝐴𝐵𝐶

3) Distributive law: 𝐴 (𝐵 + 𝐶) = 𝐴𝐵 + 𝐴𝐶

(𝐴 + 𝐵) (𝐶 + 𝐷) = 𝐴𝐶 + 𝐴𝐷 + 𝐵𝐶 + 𝐵𝐷

4) Boolean algebraic theorems

(i) 𝐴 . 𝐴 = 𝐴; 𝐴 .0 = 0

𝐴 .1 = 𝐴; 𝐴 . 𝐴 = 0

(ii) A = A

(iii) 𝐴 + 𝐴 = 𝐴; 𝐴 + 0 = 𝐴

𝐴 + 1 = 1; 𝐴 + 𝐴 = 1

(iv) Demorgan’s theorem,

1) 𝐴 . 𝐵 . 𝐶 = 𝐴 + 𝐵 + 𝐶 2) 𝐴 + 𝐵 + 𝐶 = 𝐴 . 𝐵 . 𝐶

(v) Transposition theorem

0 (𝐴 + 𝐵) (𝐴 + 𝐶) = 𝐴 + 𝐵𝐶

(vi) Distribution theorem

𝐴 + 𝐵𝐶 = (𝐴 + 𝐵) (𝐴 + 𝐶)

(vii) Consensus Theorem

𝐴𝐵 + 𝐴𝐶 + 𝐵𝐶 = 𝐴𝐵 + 𝐴𝐶

Other Theorems:

1) (𝐴 + 𝐵) . (𝐴 + 𝐵 ) = 𝐴 5) (𝐴 + 𝐵) (𝐴 + 𝐶) = 𝐴𝐶 + 𝐴𝐵

2) 𝐴 + 𝐵 + 𝐶 = 𝐴. 𝐵 . 𝐶 6) 𝐴𝐵 + 𝐴𝐶 + 𝐵𝐶 = 𝐴𝐵 + 𝐴𝐶

3) 𝐴𝐵 + 𝐴𝐶 = (𝐴 + 𝐶) (𝐴 + 𝐵) 7) (𝐴 + 𝐵) (𝐴 + 𝐶) (𝐵 + 𝐶) = (𝐴 + 𝐵) (𝐴 + 𝐶)

4) 𝐴 . 𝐵 . 𝐶 = 𝐴 + 𝐵 + 𝐶

#62, Rakame Complex, Periyar Bus Stand, Madurai-11 | 7373007731 | www.maduracoaching.com

15

Digital Logic Circuit

5) Duality Theorem:-

(i) Change OR Sign to AND sign

(ii) Complement “0” to “1”

(iii) Keep literals as it

n

For N variables, maximum possible self-dual function = 2(2 /2 )

With N variables, maximum possible distinct logic functions = 22n

6) AND – OR logic ≡ NAND – NAND logic in SOP

OR – AND logic ≡ NOR – NOR logic in POS

7)

Dual Complement

1) AND ↔ OR 1) AND ↔ OR

2) 1 ↔ 0 2) 1 ↔ 0

3) Keep variable as it as 3) Complement each variable

8)

With „n‟ variable max possible logical expressions = 22n

n −1

With „n‟ variable max possible self dual expressions = 22

9) Digital Number Representation:-

(i) Unsigned magnitude representation = 0 to (2n - 1)

(ii) Signed magnitude representation = - (2n−1 - 1) to + (2n−1 - 1)

(iii) Range of 1‟s complement number = - (2n−1 - 1) to + (2n−1 - 1)

(iv) Range of 2‟s complement number = -2n−1 to + (2n−1 – 1)

UNIT - IV: COMBINATIONAL CIRCUITS

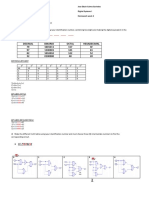

1.

Type of Circuit Logical Expressions

Sum = A⨁B

Half adder

Carry = AB

Difference = A⨁B

Half Subtractor

Borrow = AB

SUM = A⨁B⨁C

Full Adder

Carry = AB + BC + CA

Difference = A⨁B⨁C

Full Subtractor

Borrow = AB + AC + BC

#62, Rakame Complex, Periyar Bus Stand, Madurai-11 | 7373007731 | www.maduracoaching.com

16

Digital Logic Circuit

2.

Type of No of gates

circuit required

NAND NOR

Half adder 5 5

Half

subtractor 5 5

Full adder 9 9

Full subtractor 9 9

3. Full adder can be implemented with = Two half adder + one OR gate

4. Parallel adder [Ripple carry adder (or) Binary adder]

n FA (or) (n – 1) FA & one HA FA → Full adder

(or) HA → Half adder

(2n -1) HA & (n – 1) OR

5. Delay time (𝐓𝐝𝐞𝐥𝐚𝐲 ):

Tdelay = (n – 1) t cpd + max (t spd , t cpd )

Where t cpd → Carry propagation delay

t spd → Sum propagation delay

6. Multiplexer:

Y0 = (ABI0 + A B I1 + A BI2 + A B I3 ) E

m ≤ 2n (or) log 2 m ≤ n

7. 2 : 1 multiplexer applications:

Multiplexer Logical Expression

Y0 = A

(NOT)

Y0 = A B + A

=A+B

(OR)

#62, Rakame Complex, Periyar Bus Stand, Madurai-11 | 7373007731 | www.maduracoaching.com

17

Digital Logic Circuit

Y0 = A.0 + AB

Y0 = AB

(AND)

Y0 = AB + A.O

Y0 = A + B

(NOR)

Y0 = A.1 + AB

=A+B

Y0 = AB(NAND)

Y0 = A⨁B

(EX – OR)

Y0 = A⊙B

(EX – NOR)

8) Higher order mux using lower order mux:

Required Number

Given Mux Needed Mux

of Mux

2:1 4:1 3

4:1 16 : 1 4+1=5

4:1 64 : 1 16 + 4 + 1 = 21

8:1 64 : 1 8+1=9

8:1 256 : 1 32 + 4 + 1 = 37

9) Demultiplexer: (One to many circuit):

1 : 2 Demux

D0 = SA ; D1 = SA

#62, Rakame Complex, Periyar Bus Stand, Madurai-11 | 7373007731 | www.maduracoaching.com

18

Digital Logic Circuit

1 : 4 Demux

D0 = S1 S0 A

D1 = S1 S0 A

D2 = S1 S0 A

D3 = S1 S0 A

10. Higher order Demux using lower order Demux:

Given Needed

Required number of mux

Demux Demux

1:2 1:4 1+2=3

1:2 1:8 1+2+4=7

1:2 1 : 16 1 + 2 + 4 + 8 = 15

1:2 1 : 64 1 + 2 + 4 + 8 + 16 + 32 = 63

1:4 1 : 16 1+4=5

11. 2 ×4 Decoder :

E A B 𝐃𝟎 𝐃𝟏 𝐃𝟐 𝐃𝟑

1 X X 1 1 1 1

0 0 0 0 1 1 1

0 0 1 1 0 1 1

0 1 0 1 1 0 1

0 1 1 1 1 1 0

Higher order decoder using lower order decoder:

Required

Needed

Given decoder number of

decoder

decoder

2:4 4 : 16 1+4=5

2:4 3:8 2 + Not gate

4 : 16 8 : 256 1 + 16 = 17

#62, Rakame Complex, Periyar Bus Stand, Madurai-11 | 7373007731 | www.maduracoaching.com

19

Digital Logic Circuit

12. Code Converters:

(i) BCD to Excess – 3 code : (BCD + 0011 = excess – 3 code)

Input (BCD) Output (Excess – 3 code)

A B C D W X Y Z

0 0 0 0 0 0 1 1

0 0 0 1 0 1 0 0

0 0 1 0 0 1 0 1

0 0 1 1 0 1 1 0

0 1 0 0 0 1 1 1

0 1 0 1 1 0 0 0

0 1 1 0 1 0 0 1

0 1 1 1 1 0 1 0

(ii) Binary to gray converter

G3 = B3

G2 = B3 ⨁B2

G1 = B2 ⨁B1

G0 = B1 ⨁B0

(iii) Gray to Binary converter

B3 = G3

B2 = B3 ⨁G2

B1 = B2 ⨁G1

B0 = G1 ⨁G0

(iv) Magnitude Comparator

A B X Y Z

0 0 0 1 0

0 1 1 0 0

1 0 0 0 1

1 1 0 1 0

o/p Expression AB A⊙B AB

#62, Rakame Complex, Periyar Bus Stand, Madurai-11 | 7373007731 | www.maduracoaching.com

20

Digital Logic Circuit

UNIT - V: SEQUENTIAL CIRCUITS

Flip Flop Truth Table

1) SR Flip Flop

CLK S R Q 𝐐

0 X X Previous

1 0 0 Previous

1 0 1 0 1

1 1 0 1 0

1 1 1 NOT ALLOWED

2) J-K Flip Flop

CLK J K 𝐐𝐧 𝐐𝐧

0 X X Previous

1 0 0 Previous

1 0 1 0 1

1 1 0 1 0

1 1 1 Toggle

3) D Flip Flop

CLK D O/P

0 X Previous

1 0 0

1 1 1

4) T – Flip Flop CLK T 𝐐𝐧+𝟏

0 X Qn (Previous)

1 0 Qn (Previous)

1 1 Qn Toggle

#62, Rakame Complex, Periyar Bus Stand, Madurai-11 | 7373007731 | www.maduracoaching.com

21

Digital Logic Circuit

2) Characteristic Table

JK Flip Flop SR Flip Flop T Flip Flop

J K 𝐐𝐧 𝐐𝐧+𝟏 J K 𝐐𝐧 𝐐𝐧+𝟏 T 𝐐𝐧 𝐐𝐧+𝟏

0 0 0 0 0 0 0 0 0 0 0

0 0 1 1 0 0 1 1 0 1 1

0 1 0 0 0 1 0 0 1 0 1

0 1 1 0 0 1 1 0 1 1 0

1 0 0 1 1 0 0 1 Qn+1 = T⨁𝑄𝑛

1 0 1 1 1 0 1 1

1 1 0 1 1 1 0 X

1 1 1 0 1 1 1 X

Qn+1 = JQn + KQn Qn+1 = S + R

3) Excitation Table

JK FF SR FF

𝐐𝐧 𝐐𝐧+𝟏 S R

𝐐𝐧 𝐐𝐧+𝟏 J K

0 0 0 X

0 0 0 X

0 1 1 0

0 1 1 X

1 0 0 1

1 0 X 1

1 1 X 0

1 1 X 0

D FF T - FF

𝐐𝐧 𝐐𝐧+𝟏 𝐃 𝐐𝐧 𝐐𝐧+𝟏 T

0 0 0 0 0 0

0 1 1 0 1 1

1 0 0 1 0 1

1 1 1 1 1 0

#62, Rakame Complex, Periyar Bus Stand, Madurai-11 | 7373007731 | www.maduracoaching.com

22

Digital Logic Circuit

4) Race-around condition:

(i) J = K = 1

(ii) 𝑡𝑝𝑑 𝐹𝐹 <𝑡𝑝𝑤

(iii) Flip – flop is level triggered

UNIT - VI: COUNTERS

1) N = total number of states

N = no of FF‟s → N ≤ 2n

2) If N = 2n → Binary counter

N <2n → Non-binary counter

3) For n FF ′ s → 2n states → called MOD - 2n counter capable of counting (2n - 1) states.

4) FOR MOD-N counter, I/P frequency = f

f

O/P frequency = N

5) If two counters cascaded

Modulus number =

𝑓𝑖

Output freq. = 𝑥.𝑦

6) Binary ripple counter (Asynchronous Counter)

1

(i) fclk ≤ nt pd (FF )

t pd =Propagation delay

1

(ii) Maximum clock frequency, fclk = nt pd (FF )

7) Up/down counter

Clock

Triggering Counter

Connection

-ve edge Q Up counter

+ve edge 𝑄 Up counter

-ve edge 𝑄 Down counter

+ve edge Q Down counter

#62, Rakame Complex, Periyar Bus Stand, Madurai-11 | 7373007731 | www.maduracoaching.com

23

Digital Logic Circuit

8) Synchronous Counters:

(i) Ring counter: (non self starting counter)

Modulus number = n

f

fo = ni

max count = 2n−1

Tdelay = t pd

(ii) Johnson Counter: (Twisted Ring Counter)

Modulus number = 2n

f

fo = 2𝑛i

max count = 2n − 1

(iii) Synchronous series carry counter (serial counter)

Modulus number = 2n

f

fo = 2ni

max count = 2n -1

Tdelay = t pd (FF ) + (n - 2) t pd

(iv) Parallel counter

Modulus number = 2n

f

fo = 2ni

max count = 2n -1

Tdelay = t pd ff + t pd

Where t pd FF ⇒ propagation delay of flip flop

t pd ⇒propagation delay of gate

Shift Registers

(i) I/P O/P Total

Serial in serial out (SISO) n n-1 2n-1

Serial in parallel out (SIPO) n 0 n

Parallel in serial out (PISO) 1 n-1 n

Parallel in parallel out (PIPO) 1 0 1

where n = no of F.F‟s

(ii) Interms of speed:

PIPO > PISO > SIPO > SISO

#62, Rakame Complex, Periyar Bus Stand, Madurai-11 | 7373007731 | www.maduracoaching.com

24

Digital Logic Circuit

UNIT – VII: DIGITAL CONVERTERS

1) Digital to Analog Converter (DAC):

Specifications:

vr

(i) Resolution = , vr = reference voltage ; n = number of bit

2n −1

(ii) Resolution × Decimal equivalent of binary data = Output Voltage

(iii) Analog O/P voltage

Vo = k 2N−1 bN−1 + 2N−2 bN−2 + ⋯ 21 b1 + b0

Where k → proportionality factor

bn →1 ; If nth bit of digital i/p is 1.

→ 0 ; If nth bit digital i/p is 0.

(iv) Full scale output voltage = Resolution × max decimal

Vr

(vFS ) = × (2n − 1) = Vr

2n −1

Resolution 1

% Resolution = × 100 = × 100

V FS 2n −1

2) Weighted Resistor DAC:

RF

(i) Output Voltage V0 = (2N−1 VN−1 + 2N−2 VN−2 + ⋯ 20 V2 )

2N −1 .R

RF

(ii) Proportionality factor k = VR

2 −1 .R

N

(iii) LSB Resistance = 2N−1 × 𝑀𝑆𝐵 𝑅𝑒𝑠𝑖𝑠𝑡𝑎𝑛𝑐𝑒

(iv) For N bit DAC,

Number of different levels = 2N

Number of steps = 2N -1

3) R-2R ladder type DAC:

RF Vr Vr Vr

V0 = D2 × + D1 × + D0 ×

3R 2 4 8

4) Counter type DAC:

V FSC

(i) Resolution = 2n −1

1

(ii) % Resolution = × 100

2n −1

(iii) No of clock pulse required for n-bit conversion = 2n -1

(iv) Maximum conversion time = (2N − 1). TCIK

(v) VO = VDAC = R × (Decimal equivalent of binary)

(vi) VFSC = (2𝑛 − 1) × Step Size

#62, Rakame Complex, Periyar Bus Stand, Madurai-11 | 7373007731 | www.maduracoaching.com

25

Digital Logic Circuit

5) Flash type ADC:

It requires (i) 2n − 1 comparators

(ii) 2n resistors

(iii) One 2n × n priority encoder

6) Successive approximation type ADC:

(i) Number of clock pulse required = n

(ii) Maximum conversion time = n * TCIK

7) Dual slope integrating type ADC:

Va

(i) Count = 2n

VR

(ii) Tconv = (2n+1 -1)TC

1

(iii) fsamp = (2n +1 −1)T C

(iv) De-integration time

Va

(T2 - T1 ) = × Integration time (T1 )

VR

(v) T1 = 2n TC

𝐷𝑒−𝑖𝑛𝑡𝑒𝑔𝑟𝑎𝑡𝑖𝑜𝑛 𝑡𝑖𝑚𝑒

(vi) Va = × VR

𝐼𝑛𝑡𝑒𝑔𝑟𝑎𝑡𝑖𝑜𝑛 𝑡𝑖𝑚𝑒

#62, Rakame Complex, Periyar Bus Stand, Madurai-11 | 7373007731 | www.maduracoaching.com

26

You might also like

- CIPP - US Certification Guide With Sample Questions-1Document14 pagesCIPP - US Certification Guide With Sample Questions-1Harshit RajputNo ratings yet

- 2 - Kubernetes On Azure Pitch DeckDocument103 pages2 - Kubernetes On Azure Pitch Decksai b100% (1)

- Digital Electronics Lesson 6 Logic GatesDocument11 pagesDigital Electronics Lesson 6 Logic GatesJanette C.No ratings yet

- Term 2 - Grade 8 Coding Chapter 8 Smart ComputersDocument3 pagesTerm 2 - Grade 8 Coding Chapter 8 Smart Computersprakashjoshi23aprilNo ratings yet

- DT Ica Booklet Final 2024-25 Sem-I With BorderDocument67 pagesDT Ica Booklet Final 2024-25 Sem-I With BorderAvinash HaraleNo ratings yet

- 06ESL38 - Logic Design Lab1Document76 pages06ESL38 - Logic Design Lab1Sachin S ShettyNo ratings yet

- 1008uf Eeec-DigitalDocument9 pages1008uf Eeec-DigitalAshutosh JaiswalNo ratings yet

- Unit2Activities-GUMANAD, RICKY Q.Document12 pagesUnit2Activities-GUMANAD, RICKY Q.Ricky GumanadNo ratings yet

- Computer Number Systems and Boolean Algebra Notes Formula SheetDocument2 pagesComputer Number Systems and Boolean Algebra Notes Formula SheetElaine zhuNo ratings yet

- Week 7Document16 pagesWeek 7Abdullah SohailNo ratings yet

- Digital ElectronivsDocument35 pagesDigital ElectronivsRaja KumarNo ratings yet

- Digital Computer-Unit-I-6Document21 pagesDigital Computer-Unit-I-6suhelkhan900500No ratings yet

- Question 3Document2 pagesQuestion 3Sasi DarranNo ratings yet

- Previous Final Exam SolutionDocument5 pagesPrevious Final Exam SolutionArnav ChaturvediNo ratings yet

- Lab ProgramsDocument14 pagesLab ProgramsspgmaniarunagiriNo ratings yet

- Expt 06-1Document5 pagesExpt 06-1Aurongo NasirNo ratings yet

- University of Zimbabwe: Laboratory Report: Logic GatesDocument5 pagesUniversity of Zimbabwe: Laboratory Report: Logic GatesJohn MutarauswaNo ratings yet

- Co Lab ManualDocument81 pagesCo Lab ManualShiva KumarNo ratings yet

- Chapter 04 SolutionsDocument73 pagesChapter 04 Solutions박대민No ratings yet

- Exp 8Document6 pagesExp 8Pragyan AnshNo ratings yet

- Laboratory Exercise 7Document4 pagesLaboratory Exercise 7BriNyanNo ratings yet

- Ecef 1114 Electronic Technology LAB 3: Verification of Logic GateDocument11 pagesEcef 1114 Electronic Technology LAB 3: Verification of Logic GateJeromeNo ratings yet

- VHDL RecordDocument200 pagesVHDL RecordssplrbNo ratings yet

- Simulation Manual PHY340Document12 pagesSimulation Manual PHY340aisyahNo ratings yet

- DD Lab ManualDocument12 pagesDD Lab ManualKothapalli Likhith Sri SaiNo ratings yet

- Digital Microprocessor Lab Manual 5th SemDocument26 pagesDigital Microprocessor Lab Manual 5th SemRonit ChowdhuryNo ratings yet

- Carry Look Ahead Adders: Lesson ObjectivesDocument10 pagesCarry Look Ahead Adders: Lesson ObjectivespadmavathiNo ratings yet

- Manual 2018-1Document47 pagesManual 2018-1Deepa JerinNo ratings yet

- Preview Report For Experiment 1: SimulationsDocument5 pagesPreview Report For Experiment 1: Simulations이훈석No ratings yet

- Tutorial3-With Answer KeyDocument12 pagesTutorial3-With Answer KeyRetheshNo ratings yet

- Lab Report 1Document6 pagesLab Report 1Bappy HossenNo ratings yet

- EGR 265 Final ExamDocument6 pagesEGR 265 Final Examcompuguy1088No ratings yet

- Lab 2: Logic Gates / Simulation Software: EIE2810 Digital Systems Design LaboratoryDocument10 pagesLab 2: Logic Gates / Simulation Software: EIE2810 Digital Systems Design LaboratoryYabin CHENGNo ratings yet

- Modified DLD Lab ManualsDocument40 pagesModified DLD Lab ManualsASHEESH TiwariNo ratings yet

- Dpco Lab ManuaDocument54 pagesDpco Lab ManuaHANISHA SAALIHNo ratings yet

- Experiment No. - 1: Realization of Logic Gates 1) Aim: 2) RequirementsDocument7 pagesExperiment No. - 1: Realization of Logic Gates 1) Aim: 2) RequirementsVashisth ZatakiaNo ratings yet

- ENS2456 Solutions 4Document9 pagesENS2456 Solutions 4omairakhtar12345No ratings yet

- DLD THEORY ASS 01 - Izaan Ahmed Khan (FA19-BSCS-0049)Document13 pagesDLD THEORY ASS 01 - Izaan Ahmed Khan (FA19-BSCS-0049)Izaan Ahmed KhanNo ratings yet

- Chapter 4: Basics of Digital Electronics: Logic GatesDocument19 pagesChapter 4: Basics of Digital Electronics: Logic GatesSyed ShaNo ratings yet

- RIVERA Logics - Lab 8Document5 pagesRIVERA Logics - Lab 8Ricardo Edrell RiveraNo ratings yet

- ExperimentDocument28 pagesExperimentGitesh NagarNo ratings yet

- Taller Chapter 3 Sistemas DigitalesDocument4 pagesTaller Chapter 3 Sistemas DigitalesCristian PuentesNo ratings yet

- Recent PHD ResultDocument72 pagesRecent PHD ResultSavita Kiran BNo ratings yet

- FDDGDocument3 pagesFDDGaliffpadziNo ratings yet

- DSD Lab Manual 2021Document21 pagesDSD Lab Manual 2021adityaNo ratings yet

- Experiment 2 FinalDocument9 pagesExperiment 2 Finalliddleme33No ratings yet

- Tutorial 5 - Digital SystemDocument2 pagesTutorial 5 - Digital Systembalqies281No ratings yet

- Seven Segments ReportDocument12 pagesSeven Segments ReportJun TobiasNo ratings yet

- Experiment 7Document3 pagesExperiment 7AAAAALLENNNo ratings yet

- Index: S.No Experiment Name Date of Experiment Date of Submission Remark & Sign 1Document32 pagesIndex: S.No Experiment Name Date of Experiment Date of Submission Remark & Sign 1Ritwik KumarNo ratings yet

- Computer Organization and Architecture Lab: Mr. Laxmi Kant Sagar Vishal Sharma 1901920100328Document28 pagesComputer Organization and Architecture Lab: Mr. Laxmi Kant Sagar Vishal Sharma 1901920100328ayushNo ratings yet

- Digital III B.SC Practical MaterialDocument29 pagesDigital III B.SC Practical Materialtamilsrm003No ratings yet

- Screenshot 2023-02-01 at 12.08.22 PM PDFDocument27 pagesScreenshot 2023-02-01 at 12.08.22 PM PDFCM 54 Darshan VadnereNo ratings yet

- Verification of Logic Gates: Exp No: 01 DATE: 19-01-09Document208 pagesVerification of Logic Gates: Exp No: 01 DATE: 19-01-09gpuonlineNo ratings yet

- Homework Week 1Document3 pagesHomework Week 1JonatanNo ratings yet

- Lab Report DraftDocument2 pagesLab Report Draftyubraj belbaseNo ratings yet

- Digital Systems: Exercises 1Document5 pagesDigital Systems: Exercises 1月野姮娥No ratings yet

- LCD Mod3Ass TUMALIUANDocument6 pagesLCD Mod3Ass TUMALIUANmaxpein100% (1)

- Index: Sr. No. Experiment Title No. Date SignDocument15 pagesIndex: Sr. No. Experiment Title No. Date SignKrunal MakwanaNo ratings yet

- S23 DLD Lab04Document7 pagesS23 DLD Lab04thomas edisonNo ratings yet

- 50 Number Series Questions AnswerDocument15 pages50 Number Series Questions Answersai bNo ratings yet

- 30 Quant Data Sufficiency QuestionsDocument42 pages30 Quant Data Sufficiency Questionssai bNo ratings yet

- 21Q1 VMware ITExec Decision Framework Virt To MultiCloud EbookDocument14 pages21Q1 VMware ITExec Decision Framework Virt To MultiCloud Ebooksai bNo ratings yet

- 9 AeDocument20 pages9 Aesai bNo ratings yet

- Math Fundamentals For Capital MarketsDocument1 pageMath Fundamentals For Capital Marketssai bNo ratings yet

- Government of Telangana Finance (HRM - Vii) Department U.O.Note No.1093467-A/357/A1/HRM - VII/2021, Dated:10.7.2021Document2 pagesGovernment of Telangana Finance (HRM - Vii) Department U.O.Note No.1093467-A/357/A1/HRM - VII/2021, Dated:10.7.2021sai bNo ratings yet

- Microsoft Azure Administrator: @androdaggerDocument679 pagesMicrosoft Azure Administrator: @androdaggersai bNo ratings yet

- Cloud Trainee Engineer: Gandhinagar Institute of TechnolgyDocument19 pagesCloud Trainee Engineer: Gandhinagar Institute of Technolgysai bNo ratings yet

- Github Test: Mithun Technologies +91-9980923226 Git and Github Author Mithun Reddy L Web SiteDocument4 pagesGithub Test: Mithun Technologies +91-9980923226 Git and Github Author Mithun Reddy L Web Sitesai bNo ratings yet

- Vagrant Cheat Sheet + Get Started With VagrantDocument6 pagesVagrant Cheat Sheet + Get Started With Vagrantsai bNo ratings yet

- Bangalore/ChennaiDocument34 pagesBangalore/Chennaisai bNo ratings yet

- Position Summary:: Job TitleDocument1 pagePosition Summary:: Job Titlesai bNo ratings yet

- 1 Linux Interview QuestionsDocument1 page1 Linux Interview Questionssai bNo ratings yet

- Microsoft: Exam Questions AZ-104Document25 pagesMicrosoft: Exam Questions AZ-104sai bNo ratings yet

- 5 6086985088212402970Document113 pages5 6086985088212402970sai b100% (2)

- 5 6240001016188634612Document50 pages5 6240001016188634612sai bNo ratings yet

- Kodavath Ravi Naik: Personal InformationDocument2 pagesKodavath Ravi Naik: Personal Informationsai bNo ratings yet

- 1 1 2 JCLDocument6 pages1 1 2 JCLsai bNo ratings yet

- Continuity Differentiability Formula Sheet PDFDocument3 pagesContinuity Differentiability Formula Sheet PDFUtkarsh GuptaNo ratings yet

- LowPower UserDocument74 pagesLowPower Uservinodkumar kNo ratings yet

- Data Analyst - Job DescriptionDocument3 pagesData Analyst - Job DescriptionWear my GlovesNo ratings yet

- Course Code: Scax1001 Course Name: Computer Applications in Business Chapter Name: MS-WORD' Subject Coordinator: Mrs - JancyDocument26 pagesCourse Code: Scax1001 Course Name: Computer Applications in Business Chapter Name: MS-WORD' Subject Coordinator: Mrs - JancyGracyNo ratings yet

- Laboratory Manual: Analogue and Digital Communication LabDocument18 pagesLaboratory Manual: Analogue and Digital Communication LabZain HaiderNo ratings yet

- Data SecurityDocument13 pagesData SecurityAravind BabuNo ratings yet

- A Cloud Services Cheat Sheet For AWS, Azure, and Google CloudDocument16 pagesA Cloud Services Cheat Sheet For AWS, Azure, and Google CloudKartik ShuklaNo ratings yet

- Your Business Your Growth Game Your Business Your Growth GameDocument10 pagesYour Business Your Growth Game Your Business Your Growth Gamehitesh100% (1)

- Advanced Animations in Animate CCDocument10 pagesAdvanced Animations in Animate CCAly HassanNo ratings yet

- ComputerDocument28 pagesComputerJai RaiNo ratings yet

- Bilge Water SeparatorDocument121 pagesBilge Water SeparatorКостяNo ratings yet

- AtlasViewer Manual en 090522Document12 pagesAtlasViewer Manual en 090522Mihai FloreaNo ratings yet

- Sun 10.2 European Software Applications GuideDocument264 pagesSun 10.2 European Software Applications GuideMathia BellussiNo ratings yet

- Page Intentionally Left Blank: Cl-604 Aircraft Illustrated Parts CatalogDocument5 pagesPage Intentionally Left Blank: Cl-604 Aircraft Illustrated Parts CatalogEmmanuel OnwukaNo ratings yet

- TRBOnet Telephony User Guide v5.2Document20 pagesTRBOnet Telephony User Guide v5.2Christian ChavezNo ratings yet

- 08 Adhoc Sensitivity AnalysisDocument8 pages08 Adhoc Sensitivity AnalysisUdhav JoshiNo ratings yet

- L1 SAP Process InsightsDocument55 pagesL1 SAP Process InsightsGustavo RosselNo ratings yet

- Poweredge-T710 Owner's Manual En-UsDocument214 pagesPoweredge-T710 Owner's Manual En-UsVictorNo ratings yet

- Manual de Usuario Tc-p42x1x (Es) - PanasonicDocument124 pagesManual de Usuario Tc-p42x1x (Es) - PanasonicCiro lopexNo ratings yet

- Prepare Operating System: Systemd SystemdDocument6 pagesPrepare Operating System: Systemd Systemd8D audio drugsNo ratings yet

- MA2265 Part A Part B OriginalDocument112 pagesMA2265 Part A Part B OriginalSelvi SelvarajNo ratings yet

- FT VictoriaDocument55 pagesFT Victoriac_632434784No ratings yet

- Use-Ups-Power-Single-Phase-Winner-Pro TowerDocument2 pagesUse-Ups-Power-Single-Phase-Winner-Pro TowerGermanYPNo ratings yet

- Supervised Learning Classification Algorithms ComparisonDocument6 pagesSupervised Learning Classification Algorithms Comparisonpriti yadavNo ratings yet

- Deluxe3Document1 pageDeluxe3Firdaus YasinNo ratings yet

- Full Ebook of Network Programming With Go Language Essential Skills For Programming Using and Securing Networks With Open Source Google Golang 2Nd Edition Jan Newmarch 2 Online PDF All ChapterDocument70 pagesFull Ebook of Network Programming With Go Language Essential Skills For Programming Using and Securing Networks With Open Source Google Golang 2Nd Edition Jan Newmarch 2 Online PDF All Chapterjerrylorensen725426100% (5)

- Service Manual C Electric Section 2 (25 46)Document22 pagesService Manual C Electric Section 2 (25 46)Геннадий Дармоедов100% (2)

- Instructions For NITTT Test V1.1Document5 pagesInstructions For NITTT Test V1.1sarifnNo ratings yet

- 6.2.1.11 Lab - Anatomy of MalwareDocument1 page6.2.1.11 Lab - Anatomy of MalwareMelissa Fisk50% (2)