Professional Documents

Culture Documents

Isil13 Mi02

Isil13 Mi02

Uploaded by

jungjh3711Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Isil13 Mi02

Isil13 Mi02

Uploaded by

jungjh3711Copyright:

Available Formats

조합 공정 (2) – 배선 공정

Module Integration (2) - Interconnection

Introduction to Semiconductor Industry Copyright by DHLee 2013 Spring

Dept. of SCEE, Kukdong University

미세화에 따른 RC 성분의 증가로 인한 신호 전달 속도의 지연

• RC에 의한 지연은 어떤 System에서든지 나타날 수 있는 일종의 기생 효과(Parasitic Effect)에 의한 전기 신호 전달 속도의 지연을 뜻한다

. ‘R’은 기생 효과에 의해 생기는 저항(Resistance) 성분을 뜻하고, ‘C’ 역시 기생 효과에 의해 생기는 전하의 축전량(Capacitance) 성분이다

. RC 지연(RC Delay), TRC는 따라서 다음과 같이 표현된다

0.5 1.0 1.5 2.0 2.5 3.0 3.5

2.5 2.5

TRC = (r0∙LI/tD)(kD/eo)

1 mm 이하의 미세화로 진행할수록

배선에 의한 지연 성분이 Gate에 의한

개선 성분보다 점점 우세해 진다

2.0 2.0

ro: 배선 재료의 선 저항, LI: 배선 길이, tD: 절연재의 두께,

Submicron

Delay Time ( X 10-9sec)

kD: 절연재의 유전상수, eo: 배선 재료의 전도도 Regime

1.5 1.5

. 집적도가 커지면 배선 길이는 길어지고, 배선 재료의 두께는 얇아지므로

위의 식에서 보면 RC 지연 성분이 점점 커진다

1.0 1.0

. 반면에 Gate에서는 미세화와 더불어 신호 처리 속도가 증대되므로 배선

에 의한 지연 성분을 상쇄시키는 효과가 있다

0.5 0.5

. 우측 그림에서 보듯이 수 mm 단위의 설계 치수에서는 Gate의 신호 전달

속도가 배선에 의한 RC 지연 효과보다 훨씬 우세하므로 배선에 의한 RC

0 0

지연이 크게 문제가 되지 않았지만, 1mm 이하의 영역 (우측 그림 파란 0.5 1.0 1.5 2.0 2.5 3.0 3.5

색 영역)으로 들어서면서 배선에 의한 RC 지연 효과는 급격하게 지수적 Feature Size (μm)

으로 상승하므로 Gate에 의한 신호 전달 속도의 미미한 증가보다 훨씬 Figure 미세화에 따른 배선에 의한 지연 효과와 Gate에 의한 지연 효과의 변화

우세하게 작용하여 신호 처리 속도의 심각한 지연을 가져오게 된다

. 위의 RC 지연에 대한 식을 정성적으로 살펴 보면, 미세화에 따른 배선 길이의 증가, 절연재 두께의 감소는 피할 수 없는 상황이므로 이러한 지연을

감소시키기 위해서는 배선 재료에 대한 고려(교체)가 불가피하며 더불어 Capacitance를 줄이기 위해 절연 재료에 대한 고려도 필요하다

. 이에 따라 전통적으로 사용해 왔던 배선 재료 Aluminum은 최근 들어 서서히 Copper로 교체되고 있는 흐름이다

Introduction to Semiconductor Industry Copyright by DHLee 2013 Spring

Dept. of SCEE, Kukdong University

미세화에 따른 배선(Interconnection)에서의 전기적 변화

• 미세화(Scale-down)가 배선에 미치는 영향 Table Transistor 미세화가 단/장거리 배선에 미치는 영향

. 이미 살펴 본 바와 같이 미세화에 의해 Transistor Local Long Distance Remark

Component Component

Transistor는 물리적인 치수의 변화와 Level Interconnect Interconnect (Offset)

더불어 여러가지 전가적 성질의 변화를 Lateral L/S,

Length/Width L/S, W/S L/S, W/S

Dimension W/S

겪게 된다

Vertical Tox/S, Interconnect/

. 마찬가지로 미세화는 배선의 전기적인 성질 T/S, D/S T/S, D/S

Dimension xj/S Insulator Thickness

에도 많은 영향을 미치는데, 우측의 표에

Supply

VDD/S Spacing Z/S Z/S

미세화가 배선에 미치는 여러가지 영향을 Voltage

정리하였다 Doping

SNj Resistance SR S2SCR* Circuit Design

Concentration

. 미세화와 더불어 집적도가 증가하면서 과거

Capacitance

보다 더 많은 수의 Transistor가 한 Chip에 CLS/S SCCLS*

(Line-to-Substrate)

들어가게 되고, 이에 따라 Chip의 크기는 오히려 더 커지는 경향이 나타 Capacitance

CLL/S SCCLL*

나는데 DRAM이나 NAND Flash Memory 같은 기억 소자에서 최근 이 (Line-to-Line)

러한 경향이 더욱 두드러지게 나타나고 있다 Time Constant RC S2SC2RC* Circuit Design

. 이에 따라 특히 장거리 배선(Long Distance Interconnect의 경우 그 Voltage Drop IR > IR Circuit Design

전기적 성질의 변화에 IR Drop (Inductance와 Resistance에 의한 공급 Current Density SJ < SJ

전압의 변화)이 심각한 영향을 미치게 됨에 따라 이를 반영하고 설명하기 Not

Contact Resistance S2RC

Applicable

위해서 기존의 미세화 인자 S 외에 SC(>1)라는 미세화 인자가 추가된다

S: Scaling Factor, * SC: Subsequent Scaling Factor for Long Distance Interconnection

. 우측의 표에서 보는 바와 같이 옅은 주황색으로 표시된 부분들이 미세화

가 미치는 부정적인 영향인데 Line-to-Line, Line-to-Substrate Capacitance 등의 기생 성분들은 단거리 배선(Short Distance Interconnect)과는

반대로 오히려 미세화에 의해 나쁜 영향이 나타나며, 언급한 바와 같이 IR Drop도 단거리 배선의 경우보다 더 커진다

Sources: 1) J.D. Meidl, “Opportunities for Gigascale Integration,” Solid State Technology, vol. 30, no.12, p87, Dec. 1987,

2) R.H. Dennard et. al., “Design of Ion-Implanted MOSFETs with Very Small Physical Dimensions,” IEEE J. Solid State Circuits, vol. SC-9, p.256, Oct. 1974

Introduction to Semiconductor Industry Copyright by DHLee 2013 Spring

Dept. of SCEE, Kukdong University

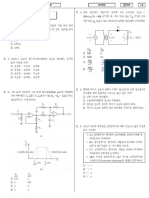

RC(Resistance & Capacitance)에 의한 신호 지연

• 기생 효과(Parasitic Effect)에 의한 축전량(Capacitance)과 소자의 저항(Resistance)

. 여러가지 기생 효과(RC)에 의한 신호 지연을 TD라 하면, 아래의 식으로 표현된다

TD = CLoad ∙(VD/ID) = CLoad ∙R

CLoad; Gate, 접합(Junctions), 배선(Interconnects) 등에서 기생 효과로 부터 발생하는 총 부하 축전량(Capacitance), R; 구성 소자 전체 저항의 합,

VD; Drain 전압, ID; Drain 전류

. 한편, 위의 식에 포함된 총 부하 축전량 CLoad 는

CLoad = CG + CJ + Cint

CG; Gate 축전량 성분, CJ; 축전량의 접합 성분,

CInt: 배선에서 발생하는 축전량

. 오른편 그림에 1개의 MOSFET Transistor에서 일어나는 모든 기생

축전량과 소자의 저항 성분을 도식적으로 표시하였다

Figure MOSFET에서 기생 효과에 의해 발생하는 축전량 성분과 구성 소자 간 저항의 Model

Source: POSTECH Lecture Materials, April 2002, 강영석

Introduction to Semiconductor Industry Copyright by DHLee 2013 Spring

Dept. of SCEE, Kukdong University

배선 재료와 배선 간 절연 재료에 의한 신호 지연 효과

• 배선 재료(Interconnect Materials)와 배선 간 절연 재료(IMD; Intermetal Dielectric Materials)의 신호 전달 속도에 대한 영향

. 앞서 본 바와 같이 배선에서 발생하는 신호 전달 속도의 지연은 1) 소자 구성 상 불가피하게 생길 수 밖에 없는 저항(Resistance) 성분, 2) 기생 효과

에 의해 발생하는 축전량(Capacitance) 성분 등이 그 원인이 되지만, 두 말할 필요도 없이 3) 배선 재료(금속)에 의해서도 영향을 받을 것이다

. 배선 재료 간 절연 역할을 수행하는 절연 재료의 절연 상수(k)에 의해서 기생 효과에 의해 발생하는 축전량(CInt)이 달라질 것이므로, 오늘날 배선

기술에 있어서 가장 중요한 문제가 1) 배선 재료로서 무엇을 선택할 것인가, 2) 절연 상수가 낮은 재료 (총칭하여 Low k 재료라고 일컬음)를 사용

하여 기생 효과를 줄이는 것이다

• Aluminum에서 Copper로의 배선 재료의 전환

. 과거에는 배선 재료로서 전기 전도도가 좋으며 값이 저렴한 Aluminum

(비저항 2.7 ~ 3.0 mW∙cm)을 전통적으로 사용하여 왔다

. 또한 Aluminum은 쉽게 Patterning이 되고 Silicon과 쉽게 고용체를 이루는

문제가 있긴 하지만, 사전에 Silicon이 일부 고용된 Al-Si 합금을 써서 접합

부위에서의 손상을 막는 것이 가능하므로 많이 이용되어 왔다

. 그러나, 집적도가 높아지고 미세화가 급속히 이루어짐에 따라 접촉(Contact)

부위가 점점 작아지고 깊어져서 Aspect Ratio가 커짐에 따라 Aluminum의

낮은 층덮임(Step Coverage)이 문제가 되었으며, 신호선 길이가 길어짐에

따라 IR Drop등의 문제도 심각하게 대두되어 전도도가 Al보다 더 좋은

Copper (비저항 1.7 mW∙cm) 로서 교체되기에 이르렀다

• 오른편 그림은 실제 실험을 통하여 배선 재료와 절연 재료의

조합이 어떻게 신호 지연에 영향을 미치는지 살펴 본 예이다 Figure 배선 재료와 배선 간 절연재의 조합에 따른 소자 신호 지연의 효과

Source: M. T. Bohr, “Interconnect Scaling – The Real Limiter to High Performance ULSI,”

Procs. of the 1996, IEEE International Electron Devices Meeting(pp241-242)

Introduction to Semiconductor Industry Copyright by DHLee 2013 Spring

Dept. of SCEE, Kukdong University

새로운 배선 재료와 저유전 재료(Low k Materials)

• 신호 전달 속도의 지연을 막기 위한 재료/공정 측면의 진보

. 신호 전달 속도의 문제는 1차적으로는 회로 설계(Circuit Design)와 소자 설계(Device Engineering)의 문제이긴 하지만, 최근 더 가속되고 있는

미세화와 고집적화 경향 속에서 이러한 접근 방법만으로는 개선시키기 쉽지 않은 문제가 되었다

. 따라서, 앞서 살펴 본 바와 같이 미세화/고집적화에 따라 불가피하게 발생하는 기생 효과들을 제어하기 위해서는 배선 재료의 교체 (예; Al -> Cu)

뿐만 아니라 배선 간 절연 물질에 대한 고려도 절대적으로 필요하다

Table 여러가지 저유전 재료(군)과 유전 상수

. 배선 재료와 절연재의 저항과 축전량을 각각 R, C라 하면, 신호 지연에 기여는 앞에서

Low k Dielectric

이미 언급한 것처럼 정량적으로 아래와 같이 표현된다 Material

Material Group Const. (kD)

CVD SiO2 SiO2, BPSG*1 4.0 - 4.2

TRC = (ro∙LI/tD)(kD/eo) SiOF ~ 3.5

Si-O Based SiOC ~ 3.0

HSQ*3 ~ 3.0

ro: 배선 재료의 선 저항, LI: 배선 길이, tD: 절연재의 두께, kD: 절연재의 유전상수,

Organic SOG ~ 2.9

eo: 배선 재료의 전도도 SOG*2

Hydrophobic Porous SOG 2.6 - 3.0

Spin-on 2.2 - 2.8

Polymer

. 위에서 보는 것처럼 미세화에 의해 LI/tD가 커질 수 밖에 없는데, 이는 미세화의 부정적 Vapor-Deposited 2.0 - 2.3

영향이며(∵ 미세화에 의해 LI↑, tD↓ -> TRC ↑) 이를 보상하여 주기 위해서 ro, kD 측면의 Porous

Si-O XerogelTM/AerogelTM ~ 2.2

Dielectric

조절이 필요한데 ro, kD 등은 재료의 고유의 값들이므로 이를 바꾸기 위해서는 재료의

Inorganic Carbonfluoride(CFx) ~ 2.5

교체가 불가피하다

Reference Air 1.0

*1

BPSG: Boro-Phosphorous Silicate Glass, *2 SOG: Spin-on-Glass

*3 Hydrogen-Silsesquioxane(H Si O )

• 새로운 배선 재료와 절연 재료 8 8 12

. 따라서 배선 재료는 Aluminum의 한계와 맞물려 자연스럽게 전도도가 더 높으면서도 비교적 저렴한 Copper로의 교체가 이루어지고 있다

. 새로운 절연 재료로는 오른쪽 표에 보인 바와 같이 전통적으로 쓰이던 SiO2 계열의 재료보다 유전 상수가 더 낮은 재료 여러가지 대체 재료가

개발, 제안되고 있다

Introduction to Semiconductor Industry Copyright by DHLee 2013 Spring

- Dept. of SCEE, Kukdong University

Copper와 저유전 재료(Low k Materials)의 적용 시 이점의 예

• 고집적화와 더불어 생겨난 IC 배선 공정에서의 또 하나의 큰 변화는 과거 단층 배선(SLM; Single Level Metallization)으로 충분하던 것이 신호

처리의 다양성과 IC Chip의 기능성의 증대로 인한 다층 배선 공정(MLM; Multi-Level Metallization)의 등장이라 할 수 있다

. MLM 공정은 반드시 필요하기는 하지만, 아래의 예에서 보는 것처럼 Copper의 등장은 저유전 재료의 사용과 더불어 다층 배선 공정에서 그 층수를

줄임으로써 공정을 상대적으로 단순화하며 공정 비용을 절감할 수 있게 되었다

a) Device with Al/SiO2 b) Device with Cu & Low k

Figure Copper와 저유전 재료의가 다층 배선 공정에 적용된 결과로 이루어진 공정 단순화(층수의 절감)

Source: M. T. Bohr, 1995 Proc. IEDM (pp241-242)

Introduction to Semiconductor Industry Copyright by DHLee 2013 Spring

Dept. of SCEE, Kukdong University

Copper 공정의 어려운 점

• Copper 공정에서 극복해야 할 과제

. 반도체 제조 공정에 있어서는 재료가 바뀌면 대부분의 경우 공정법, 장비 등이 따라서

바뀌는 것이 일반적이다

. 배선 재료가 Aluminum에서 Copper로 바뀌면서 겪는 문제점들도 공정법과 장비가

MOCVD Cu

바뀌면서 생기는 문제점들인데, 1990년대 말 ~ 2000년대 초에 대부분의 반도체 제조

회사들이 Cu 공정을 개발하면서 시행 착오와 어려움을 겪은 것은 주지의 사실이다 Electroplated

Copper

. 여러가지 문제점들은 크게, 1) 전통적 CVD, PVD 증착 공정의 어려움으로 인한 새로운

증착 공정 개발의 필요성, 2) 식각의 어려움으로 인한 새로운 Patterning 공정 개발의 Ti/TiN

필요성 등이었다

• 증착의 문제 Figure Electrodeposited Copper and Barrier Layer

. Aluminum은 PVD(Sputtering) 공정으로 증착하여 왔으나, Copper는 유사한 방법으로

증착하기 어려우며, 또한 PVD 공정은 재료 사용의 효율이 지극히 낮은 방법이므로 Al보다 비싼 Cu를 PVD로 증착하는 것은 기술적인 측면에서나

경제성의 측면에서 바람직하지 못한 방법이어서 Cu를 위해서는 새로운 증착 공정 기술의 개발이 필수적이다

. Copper를 도포하는 방법으로는 1) 전해 증착법(Electroplating), 2) 침착법(浸着, Electroless Plating) 등이 개발되었다

. 또한, Copper를 어느 두께 이상으로 증착하여 배선층으로 사용하기 위해서는 처음에 핵을 형성하는 얇은 층(Seed Layer)을 먼저 만들어 주어야

하는 것이 필요하므로, 얇은 층을 MOCVD(Metalorganic CVD) 방법으로 먼저 증착하고, 그 후에 전해 증착하거나 침착하는 것이 일반적인 공정

방법이다

. Copper의 확산을 방지하기 위해서 Seed Layer를 증착하기 전에 Ti/TiN의 확산 방지층(Diffusion Barrier Layer)을 형성해 주어야 한다

. 또한, 이렇게 새로운 증착법을 사용하기 위해서 증착 공정 전후에 새로운 세정 방법의 개발 또한 필수적이다

Introduction to Semiconductor Industry Copyright by DHLee 2013 Spring

Dept. of SCEE, Kukdong University

Copper 공정의 어려운 점 (계속)

• Copper 공정에서 극복해야 할 과제 (계속)

• Patterning과 평탄화(Planarization)의 문제

. Copper를 전통적인 방법 (Subtractive Patterning) 으로 떨어내기 위해서는 감광 공정 이후에 식각을 해주어야 하지만, 수많은 시도에도 불구하고

적절한 식각재를 개발할 수 없었다 (Cu의 염화물은 200°C 이상만 되면 너무 휘발성이 강해 Pattern을 조절하기 어려움)

. 따라서, 전통적인 Subtractive Patterning 대신 상감(象嵌, Damascene) 공법을 도입하여 Patterning하는 방법이 개발되기에 이르렀다

다음 Slide에 상감 공정 기술을 전통적인 Subtractive Patterning 법과 비교하여 설명하였다

. 이렇게 상감 공법으로 Copper를 Patterning하기 위해서는 후속 공정으로 반드시 Copper 층 자체의 평탄화(Planarization) 및 전통적인 식각 과정

과 마찬가지로 필요 없는 Copper층의 제거가 필수적이다

. 따라서, Copper의 Patterning을 위해서는 CMP(Chemical Mechanical Planarization) 공정이 필수적인 과정이 되었다

Properties of MOCVD Source

. Resistivity: 1.98 mW/cm

. Impurity(C, O): < 1.0 at.%

. Orientation: (111)

. Grain size: 0.3 ∼ 0.5 mm

1.0mm 1.0mm 1.0mm 1.0mm

0.4mm Contact Hole 0.5mm Contact Hole 0.6mm Contact Hole 0.7mm Contact Hole

Photo (hfac)Cu(TMVS)을 원료로 사용한 MOCVD 공정을 이용하여 Cu로 채워진 서로 다른 크기의 Contact Hole 주사 전자 현미경 사진

Introduction to Semiconductor Industry Copyright by DHLee 2013 Spring

Dept. of SCEE, Kukdong University

Damascene Process(象嵌 기법)

Lithography Lithography

Mask Mask

NPR* NPR

Metal

Oxide

Oxide

Etch

Oxide

Metal Dep.

Metal

Oxide

Etch CMP

Metal Metal

Oxide Oxide

a) Conventional Subtractive Patterning b) Damascene Patterning

*

NPR; Negative Photo Resist

Figure 상감 공법과 전통적인 Patterning 방법의 비교

Introduction to Semiconductor Industry Copyright by DHLee 2013 Spring

Dept. of SCEE, Kukdong University

다층 배선 공정과 Cu 상감 공정 (1)

• 다층 배선 공정(MLM; Multilevel Metallization)의 기능

. 고집적화

. Chip 크기의 감소와 기능의 다양화에 따른 신호 I/O(Package Pin 수)의 증가에 대응

. 장거리 배선의 최소화

Mn+1 Copper

Via

Mn Copper

Substrate

Figure 다층 배선 공정의 모식도 및 이에 대응하는 실제 Chip 부분에서 Cu를 사용한 다층 배선 구조의 투과 전자 현미경 사진

Introduction to Semiconductor Industry Copyright by DHLee 2013 Spring

Dept. of SCEE, Kukdong University

다층 배선 공정과 Cu 상감 공정 (2)

M6

Via

M5

Aspect Ratio=1.6

M4

M3

Photo Damascene Copper Interconnect* M2

M1

Transistor Direct

Contact

Photo 6 Layers of Damascene Copper*

*

S. Chou, M. Bohr, Intel Technology Briefing, Nov. 7, 2000

Introduction to Semiconductor Industry Copyright by DHLee 2013 Spring

Dept. of SCEE, Kukdong University

평탄화와 CMP

• 평탄화가 필요한 이유

. 감광 공정에서 초점 심도를 늘리는 데는 한계가 존재하며, 특히 오른편 그림과 같이 전체 단차

(Global Topology, Cell 지역과 주변 회로 사이의 단차)가 매우 큰 DRAM의 경우에는 감광

공정만으로 초점 심도를 개선시켜 전체 단차를 극복하기는 매우 어렵다

Cell Peripheral

. 따라서, 집적 공정 측면에서 사전에 미리 단차를 줄여 주는 평탄화 공정이 필요하다 Area Area

Local

. 후반부 공정에서 진행하게 되는 Bit Line Contact이나 배선 공정에서 필요한 Metal Contact은 Topology

그 깊이가 깊어져서 High Aspect Ratio의 Trench 형태가 되는데, 이러한 Contact 공정 전후에

Global Topology

반드시 평탄화가 필요하다

• 종래의 평탄화 공정 기술 (0.35mm 급 이상의 공정)

. 과거 0.35mm급 이상의 집적 공정에서는 높은 온도에서 점성이 있는 BPSG 등을 절연 재료로

증착하고, 850~900℃ 이하로 온도를 높여 주면 표면 이동(Surface Migration) 하는 현상을

Figure DRAM의 전체 단차와 국부 단차

이용하여 평탄화하는 방법을 전통적으로 사용하였다

. 미세화와 더불어 접합의 깊이가 점점 얕아짐에 따라 접합을 형성한 이후의 온도 상승이 극히

제한 (Thermal Budget)되어 전통적인 BPSG Flow 방식은 더 이상 사용할 수 없는 한계 상황

을 맞이하게 됨에 따라 열 공정이 전혀 필요 없는 CMP 공정이 사용되게 되었다

. CMP 공정은 화학적인 반응과 물리적인 마찰(연마, Polishing)을 이용하여 증착된 연마 대상

층 재료를 갈아 없애는 공정 기술로서, 오늘날 Copper Patterning과 그 외의 다른 목적의

평탄화 기술로서 없어서는 안될 중요한 공정 기술로 자리잡게 되었다

. 과거에 CMP는 IC 제조의 기판이 되는 Wafer를 가공하는데 많이 쓰이는 기술이었으나,

High AR Trenches

이제는 IC 제조의 본 공정(주로 후반부) 공정에서 없어서는 안 될 필수적인 IC 제조 기술의 Figure 다양한 Aspect Ratio를 가지는 Trench에서 절연 재료 충전 후

하나로 자리잡게 되었다 CMP로 평탄화한 결과를 보여주는 현미경 사진

Introduction to Semiconductor Industry Copyright by DHLee 2013 Spring

Dept. of SCEE, Kukdong University

집적 공정에서 필요로 하는 CMP 적용의 다른 예

• 오늘날 IC 제조 집적 공정 중에 CMP 평탄화가 적용되는 공정으로는 다음과 같은

것들이 있다

1) 층간 절연막 (ILD; Interlayer Dielectric) 평탄화

. 종래의 BPSG, TEOS Oxide 등을 증착 후 열 공정에 의한 평탄화를 실시하는 공정

평탄화된 지역

대체

2) 배선 층간 절연막(IMD; Intermetal Dielectric) 평탄화

Cell Block

. 종래의 SOG(Spin-on-Glass, Oxide) 증착 후 평면 식각하는 평탄화 공정을 대체

3) 얕은 Trench 격리(STI; Shallow Trench Isolation) 공정

. Trench를 이용한 소자의 격리 방법을 이용하여 종래의 LOCOS(Local Oxidation

of Silicon) 공정을 대체하기 위해서는 얕은 Trench 형성 후 Trench 내부에 절연

물질을 채워 넣어야 하는데, (앞 Slide의 우측 아래 그림) 이 때 충전된 재료 중

Trench 상부에 덮인 잉여층의 절연 재료는 CMP 공정을 통해 제거하게 된다

Figure 평탄화 공정 후의 거의 존재하지 않는 전체 단차

(Dielectrics Deposition & CMP)

Introduction to Semiconductor Industry Copyright by DHLee 2013 Spring

Dept. of SCEE, Kukdong University

You might also like

- 이동통신공학 3장Document11 pages이동통신공학 3장Chaehyung LimNo ratings yet

- A Study On SCR-Based ESD Protection Circuit With PMOSDocument5 pagesA Study On SCR-Based ESD Protection Circuit With PMOSTanuj KumarNo ratings yet

- 전자 2Document5 pages전자 2ZeusNo ratings yet

- 236 Da 943530622700 BDocument6 pages236 Da 943530622700 B이재훈No ratings yet

- Application of Plating Simulation For PCB and Pakaging ProcessDocument7 pagesApplication of Plating Simulation For PCB and Pakaging Process권대현No ratings yet

- Study On Transformer Saturation in Isolated Full-Bridge DC-DC ConvertersDocument8 pagesStudy On Transformer Saturation in Isolated Full-Bridge DC-DC ConvertersArmandinho CaveroNo ratings yet

- 기초반도체 (제5장반도체의도전현상)Document26 pages기초반도체 (제5장반도체의도전현상)fourier76100% (3)

- Fet StudyDocument12 pagesFet Studyfourier76100% (5)

- 4-2-2.전력 수송Document8 pages4-2-2.전력 수송jmpark070803No ratings yet

- 전자부품 가이드북2-저항기Document10 pages전자부품 가이드북2-저항기K SiriusNo ratings yet

- 전자부품 가이드북Document14 pages전자부품 가이드북K SiriusNo ratings yet

- 01 - 전자부품의 기초 지식Document11 pages01 - 전자부품의 기초 지식K SiriusNo ratings yet

- Adaptive Current Control of Power LEDs Using Half-Bridge LLC Resonant ConverterDocument6 pagesAdaptive Current Control of Power LEDs Using Half-Bridge LLC Resonant ConverterArmando Cavero MirandaNo ratings yet

- Sample - Basic Electromagnetics KoreanDocument64 pagesSample - Basic Electromagnetics KoreanHyun Deog YooNo ratings yet

- 03 - 전원회로에서의 부품 선택 방법Document11 pages03 - 전원회로에서의 부품 선택 방법K SiriusNo ratings yet

- 마이크로파공학 중간대비 (CYP) - A+문제Document7 pages마이크로파공학 중간대비 (CYP) - A+문제dfasNo ratings yet

- 광모듈 기본교육 (20231127)Document22 pages광모듈 기본교육 (20231127)ttr0426No ratings yet

- 전자부품 가이드북3-인덕터, 발진자Document10 pages전자부품 가이드북3-인덕터, 발진자K SiriusNo ratings yet

- 04 신호를다루는아날로그회로의부품선택방법Document15 pages04 신호를다루는아날로그회로의부품선택방법K SiriusNo ratings yet

- 전자부품 가이드북Document12 pages전자부품 가이드북K SiriusNo ratings yet

- 06 - 칩 저항Document13 pages06 - 칩 저항K SiriusNo ratings yet

- OTDR의 이해Document15 pagesOTDR의 이해Joonki YunNo ratings yet

- 제 3장 MOSFET 증폭기의 주파수 응답Document7 pages제 3장 MOSFET 증폭기의 주파수 응답E석ᄒNo ratings yet

- Modelling and Transient Analysis of A 3-Phase Multi-Layer HTS Coaxial Cable Using PSCAD - EMTDCDocument6 pagesModelling and Transient Analysis of A 3-Phase Multi-Layer HTS Coaxial Cable Using PSCAD - EMTDCphieuxuatkhoNo ratings yet

- 광모듈 기본교육 (20231127)Document22 pages광모듈 기본교육 (20231127)ttr0426No ratings yet

- 전자부품 가이드북1-콘덴서Document16 pages전자부품 가이드북1-콘덴서K SiriusNo ratings yet

- 공정 변수에 따른 비정질 인듐갈륨징크옥사이드 산화물 반도체 트랜지스터의 전기적 특성 연구Document4 pages공정 변수에 따른 비정질 인듐갈륨징크옥사이드 산화물 반도체 트랜지스터의 전기적 특성 연구강민/전자공학과No ratings yet

- Analysis of Radar Cross Section For Naval Vessels With Metamaterials and Radar Absorbing MaterialsDocument7 pagesAnalysis of Radar Cross Section For Naval Vessels With Metamaterials and Radar Absorbing MaterialsanhtrinhndNo ratings yet

- PCB 설계 노하우1Document14 pagesPCB 설계 노하우1예상영No ratings yet

- Analysis of Radar Cross Section For Advanced Naval VesselsDocument8 pagesAnalysis of Radar Cross Section For Advanced Naval VesselsanhtrinhndNo ratings yet

- 반도체물성과소자11장Document54 pages반도체물성과소자11장이하람[학생](공과대학 정보전자신소재공학과)No ratings yet

- Chap21 - 전류와 직류 및 교류 회로Document33 pagesChap21 - 전류와 직류 및 교류 회로오승민No ratings yet

- Deff - Dloss - Development of Planar Transformer and SiC Based 3 KW High Power Density DC-DC Converter For Electric VehiclesDocument8 pagesDeff - Dloss - Development of Planar Transformer and SiC Based 3 KW High Power Density DC-DC Converter For Electric VehiclesMarcelo Flavio GuepfrihNo ratings yet

- Galloping Phenomenon and Analysis Natural Frequency For Conductor Transmission LineDocument2 pagesGalloping Phenomenon and Analysis Natural Frequency For Conductor Transmission Line임종윤No ratings yet

- 투명 산화물 반도체의 개요 및 응용Document8 pages투명 산화물 반도체의 개요 및 응용강민/전자공학과No ratings yet

- Electrical Properties of Organic PVA Gate Insulator Film on ITO - Glass Substrates 참고논문1Document5 pagesElectrical Properties of Organic PVA Gate Insulator Film on ITO - Glass Substrates 참고논문1이하람[학생](공과대학 정보전자신소재공학과)No ratings yet

- The Measurement of Electromagnetic Wave in Power Cable Tunnel of Underground Utility TunnelDocument7 pagesThe Measurement of Electromagnetic Wave in Power Cable Tunnel of Underground Utility TunnelTien Dung PhanNo ratings yet

- Chapter 2. RLC BasicsDocument15 pagesChapter 2. RLC Basics최시온No ratings yet

- 전력Document8 pages전력fourier76No ratings yet

- 5장 1 P n Junctions (2018)Document34 pages5장 1 P n Junctions (2018)장대호No ratings yet

- 02 (1) .보청기의 구조와 기능Document24 pages02 (1) .보청기의 구조와 기능entgo8282No ratings yet

- 04 CMP 1Document9 pages04 CMP 1왕짱셔영No ratings yet

- Pipeline Coating Defect DetectionDocument38 pagesPipeline Coating Defect Detection이선엽No ratings yet

- 제3장지중송전선로Document47 pages제3장지중송전선로picjyNo ratings yet

- 07 - 노이즈 대책 부품과 회로 보호 부품Document10 pages07 - 노이즈 대책 부품과 회로 보호 부품K SiriusNo ratings yet

- 전력공학 요약Document4 pages전력공학 요약Seonho KimNo ratings yet

- 전력공학 요약Document4 pages전력공학 요약Seonho KimNo ratings yet

- The Design of Wireless Power Transmission System For Charging Lithium Ion BatteryDocument43 pagesThe Design of Wireless Power Transmission System For Charging Lithium Ion BatteryArmando Cavero MirandaNo ratings yet

- 2016-17646 - 고두용 - 재료의 전기적, 광학적 성질Document7 pages2016-17646 - 고두용 - 재료의 전기적, 광학적 성질이찬형No ratings yet

- 무엇이 전자현미경의 분해능 제한을 결정하는가Document2 pages무엇이 전자현미경의 분해능 제한을 결정하는가jungjh3711No ratings yet

- 221015 국가 7급 2차 전자회로-나 - 240121 - 153610Document5 pages221015 국가 7급 2차 전자회로-나 - 240121 - 153610qkrwlscjf12No ratings yet

- 221015 국가 7급 2차 전자회로-나Document5 pages221015 국가 7급 2차 전자회로-나qkrwlscjf12No ratings yet

- Textbook: Fundamentals of Engineering Electromagnetics' by Dr. ChengDocument163 pagesTextbook: Fundamentals of Engineering Electromagnetics' by Dr. Cheng김은총No ratings yet

- 전자부품 가이드북Document13 pages전자부품 가이드북K SiriusNo ratings yet

- JW - Chap21 - 전류와 직류 및 교류 회로Document31 pagesJW - Chap21 - 전류와 직류 및 교류 회로ghdtjdqja8No ratings yet

- 전자부품 가이드북5-고주파대응 부품Document12 pages전자부품 가이드북5-고주파대응 부품K SiriusNo ratings yet

- Korean FTTH Market AnalysisDocument29 pagesKorean FTTH Market AnalysisIan Yeon100% (5)

- Lecture 1 NtroductiomDocument29 pagesLecture 1 Ntroductiom2554759No ratings yet

- Hardkernel ODROID 공개자료Document192 pagesHardkernel ODROID 공개자료Joseph KymmNo ratings yet