Professional Documents

Culture Documents

(Video Title) : FPGA Design For Embedded Systems

Uploaded by

Al AminOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

(Video Title) : FPGA Design For Embedded Systems

Uploaded by

Al AminCopyright:

Available Formats

FPGA Design for Embedded

[Video Title]

Systems

FPGA Design for Embedded Systems

Hardware Description

[Instructor Name(s)]

Languages for Logic Design

[Department Name]

Copyright © 2019 University of Colorado

Objectives

• Explore the history of VHDL

[Video Title] • Methods for learning VHDL

• Syntax and practice

Copyright © 2019 University of Colorado

What is VHDL?

• VHDL is a programming language

[Video Title] • VHDL is structured to

• Describe

• Model (Simulate)

• Synthesize (Translate) into digital electronics

• VHDL has abstraction levels

• Transistor (AND, Flip-Flop)

• Complete System (Hierarchy Levels)

Copyright © 2019 University of Colorado

What is VHDL?

• VHDL is an IEEE standard

• V = VHSIC

[Video Title] • VHSIC = Very High Speed Integrated Circuit

• HDL = Hardware Description Language

• VHDL was a project sponsored by the US

Government and the Air Force which

began in 1980

References: Dr. Yaser Khalifa, 2003/09/17, Introduction to VHDL.

Available: www.engr.newpaltz.edu/~khalify/VHDL.pdf Copyright © 2019 University of Colorado

Learning to “Speak” VHDL

• Strategies for learning any language

• Reduction (Basic elements)

[Video Title] • Immersion (Simulation, Synthesis)

• Repetition (Practice)

• First phrases

• Start with useful phrases (Skeleton)

• Deconstruct “grammar” (syntax) elements

Copyright © 2019 University of Colorado

VHDL Keywords

• Reserved words (short list)

• Can not be used as identifiers

• Ex. do not use “access” as a bus name

access after alias all attribute block

body buffer bus constant exit file

for function generic group in is

label loop mod new next null

of on open out range rem

return signal shared then to type

until use variable wait while with

Reference : Bryan Mealy, Fabrizio Tappero, 2012/01/13,

FREE RANGE VHDL : freerangefactory.org

Copyright © 2019 University of Colorado

Example: 4-bit Comparator in VHDL

A

B

Result

Copyright © 2019 University of Colorado

VHDL Modeling

• Structural modeling (Gate-level)

• Library defined primitive gates (and2/or2)

• Boolean, bitwise logical (and/or)

• Library user defined functions (and17)

• Dataflow modeling

• Use assignment and select statements

• Behavioral modeling

• Use assignments within a process

• process(A, B) , sensitivity list of A, B signals

Copyright © 2019 University of Colorado

4-bit Comparator – Structural Description

-- Use standard IEEE library

library IEEE;

use IEEE.std_logic_1164.all;

-- Entity

[Video Title]

entity Comparator is port (

A,B : in std_logic_vector(3 downto 0);

Result : out std_logic);

end Comparator;

use work.gatespkg.all;

-- Architecture

-- Structural gate description

architecture struct of Comparator is

signal x : std_logic_vector(3 downto 0);

begin

u3: xnor2 port map (A(3), B(3), X(3));

u2: xnor2 port map (A(2), B(2), X(2));

u1: xnor2 port map (A(1), B(1), X(1));

u0: xnor2 port map (A(0), B(0), X(0));

u4: and4 port map (X(3), X(2), X(1), X(0), Result);

end struct;

Copyright © 2019 University of Colorado

4-bit Comparator – Boolean Description

-- Use standard IEEE library

library IEEE;

use IEEE.std_logic_1164.all;

-- Entity

entity Comparator is port (

A,B : in std_logic_vector(3 downto 0);

Result : out std_logic);

end Comparator;

-- Architecture

-- Boolean logic description

architecture bool of Comparator is

begin

Result <= not(A(3) xor B(3)) and

not(A(2) xor B(2)) and

not(A(1) xor B(1)) and

not(A(0) xor B(0));

end bool;

Copyright © 2019 University of Colorado

4-bit Comparator – Dataflow Description

-- Use standard IEEE library

library IEEE;

use IEEE.std_logic_1164.all;

-- Entity

entity Comparator is port (

A,B : in std_logic_vector(3 downto 0);

Result : out std_logic);

end Comparator;

-- Architecture

-- Dataflow description

architecture dataflow of Comparator is

begin

Result <= '1' when (A=B) else '0';

end dataflow;

Copyright © 2019 University of Colorado

4-bit Comparator – Behavioral Description

-- Use standard IEEE library

library IEEE;

use IEEE.std_logic_1164.all;

-- Entity

entity Comparator is port (

A,B : in std_logic_vector(3 downto 0);

Result : out std_logic);

end Comparator;

-- Architecture

-- Behavioral description

architecture behavioral of Comparator is

begin

CompareProcess : process(A, B)

begin

if (A=B) then

Result <= '1';

else

Result <= '0';

end if;

end process CompareProcess;

end behavioral;

Copyright © 2019 University of Colorado

Summary

• History and definition of VHDL

• An approach to learning VHDL, involving

assimilation of vocabulary, phrases and

syntax

• Initial design examples : 4-bit comparator

• Structural, Boolean, Dataflow, Behavioral

Copyright © 2019 University of Colorado

You might also like

- VHDL LabDocument50 pagesVHDL LabAnuNo ratings yet

- Lab No: 1 Introduction To Verilog (Gate-Level Modeling, Data-Flow Modeling and Behavioral Modeling)Document3 pagesLab No: 1 Introduction To Verilog (Gate-Level Modeling, Data-Flow Modeling and Behavioral Modeling)MaleehaBabarNo ratings yet

- VLSI and OFC Lab2016 PDFDocument63 pagesVLSI and OFC Lab2016 PDFsandeep_hriturajNo ratings yet

- Verilog1 MaterialDocument45 pagesVerilog1 Materialroopa_kothapalliNo ratings yet

- Verilog 1Document45 pagesVerilog 1Arthur AguilarNo ratings yet

- Digital Design Using VHDL: Using Xilinx'S Tool For Synthesis and Modelsim For VerificationDocument24 pagesDigital Design Using VHDL: Using Xilinx'S Tool For Synthesis and Modelsim For Verificationabhimicky23No ratings yet

- HDL CombinacionalDocument64 pagesHDL CombinacionalMohammad Nizam100% (1)

- Comm 471: Digital Circuit Design Lab1Document31 pagesComm 471: Digital Circuit Design Lab1Mina AdelNo ratings yet

- CMOS Technology and Verilog HDL BasicsDocument11 pagesCMOS Technology and Verilog HDL BasicsUnique ProNo ratings yet

- Jaypee University of Engineering & Technology, Guna Deparment of Computer Science & EngineeringDocument7 pagesJaypee University of Engineering & Technology, Guna Deparment of Computer Science & EngineeringAmit SharmaNo ratings yet

- Digital Design Using VHDL: Reem Ibrahim, PH.DDocument21 pagesDigital Design Using VHDL: Reem Ibrahim, PH.DZeyad AymanNo ratings yet

- ECE VHDL Verilog Lab Manual SemesterDocument133 pagesECE VHDL Verilog Lab Manual Semesterchiranjeevee02No ratings yet

- VerilogDocument44 pagesVerilogTharun kondaNo ratings yet

- Design language overview for software and hardwareDocument53 pagesDesign language overview for software and hardwareshreyaNo ratings yet

- VHDL - Intro and Syntax - VLSI Design Using VHDL Training - Internshala VTCDocument2 pagesVHDL - Intro and Syntax - VLSI Design Using VHDL Training - Internshala VTCadityaNo ratings yet

- Start HereDocument16 pagesStart HeresweetupriyaNo ratings yet

- Introduction to VHDL (IntroDocument8 pagesIntroduction to VHDL (IntroAbdul RajakNo ratings yet

- Introduction to VHDL Lab 2Document8 pagesIntroduction to VHDL Lab 2Jawath BinaNo ratings yet

- Verilog Chapter 3: Modules and Hierarchical StructureDocument24 pagesVerilog Chapter 3: Modules and Hierarchical Structurecuong03No ratings yet

- A Comprehensive TutorialDocument119 pagesA Comprehensive TutorialMayank KamraNo ratings yet

- DD&CO Full Lab ManualDocument45 pagesDD&CO Full Lab ManualHarshitha SinghNo ratings yet

- Practical - 1. VHDL Introduction: Design FlowDocument162 pagesPractical - 1. VHDL Introduction: Design FlowNilesh Kantilal PatelNo ratings yet

- VHDL Lecture 1 - Simulation and Hardware DescriptionDocument78 pagesVHDL Lecture 1 - Simulation and Hardware DescriptionSOHAN DEBNATHNo ratings yet

- VHDL Lecture Series-IDocument21 pagesVHDL Lecture Series-IParag ParandkarNo ratings yet

- Vls I Lab Manual 2021Document58 pagesVls I Lab Manual 2021shilpakesavNo ratings yet

- VLSI - VHDL Hi RanjithDocument77 pagesVLSI - VHDL Hi RanjithmjayasanthiNo ratings yet

- Basic of FPGA ConstructionDocument6 pagesBasic of FPGA Constructionamyth_316No ratings yet

- VHDL Introduction to Entity and ArchitectureDocument28 pagesVHDL Introduction to Entity and ArchitectureTiga LeungNo ratings yet

- The Art of FPGA ConstructionDocument15 pagesThe Art of FPGA Constructionwilliam.barcellosNo ratings yet

- Masamb Electronics Systems Pvt. Ltd. Verilog HDL for DummiesDocument132 pagesMasamb Electronics Systems Pvt. Ltd. Verilog HDL for DummiesparagupsNo ratings yet

- 04 - Introduction to VHDLDocument39 pages04 - Introduction to VHDLJorge ReyNo ratings yet

- VHDL FinalDocument152 pagesVHDL FinalManish YadavNo ratings yet

- Hardware Description Language: B. RamamurthyDocument19 pagesHardware Description Language: B. Ramamurthysoumya vollalaNo ratings yet

- U-1 Overview of HDLDocument14 pagesU-1 Overview of HDLDEEPA KUNWARNo ratings yet

- Introduction To VHDL: Unit-1Document59 pagesIntroduction To VHDL: Unit-1Tilak RajputNo ratings yet

- 02.-Introduction VHDL ProgrammingDocument71 pages02.-Introduction VHDL ProgrammingFarias Ben JaNo ratings yet

- Vlsi Design LabDocument21 pagesVlsi Design LabAbhinav GargNo ratings yet

- Module - 5 Introduction To VHDL 5.1: ObjectivesDocument14 pagesModule - 5 Introduction To VHDL 5.1: Objectivesabhilash gowdaNo ratings yet

- Vlsi VHDLDocument22 pagesVlsi VHDLsamiularefin2000No ratings yet

- EE8351 Digital Logic Circuits: S.S.Harish Department of EEEDocument33 pagesEE8351 Digital Logic Circuits: S.S.Harish Department of EEEkkr kkrNo ratings yet

- Programmable Logic Design With VHDLDocument198 pagesProgrammable Logic Design With VHDLDaniel CornelioNo ratings yet

- Experiment 5 Title: Write VHDL Code For The Logic Gates and Simulate ItDocument7 pagesExperiment 5 Title: Write VHDL Code For The Logic Gates and Simulate ItVidya SagvekarNo ratings yet

- OOPS UNIT 4 Two MarksDocument6 pagesOOPS UNIT 4 Two MarksRayna EzhilNo ratings yet

- HDL Manual 2018 19 UpdatedDocument59 pagesHDL Manual 2018 19 UpdatedNisha TNo ratings yet

- Chapter 4Document57 pagesChapter 4Hao XiaoNo ratings yet

- Dalvik Virtual MachineDocument27 pagesDalvik Virtual Machineint0No ratings yet

- Prelim Module5 - BDocument7 pagesPrelim Module5 - BCelimen, John Renz C.No ratings yet

- CMEN722 Tutorial On Lecture 2 & 3 Digital System Design With VHDLDocument14 pagesCMEN722 Tutorial On Lecture 2 & 3 Digital System Design With VHDLSayiTisanShalomNo ratings yet

- C Language QR v2Document17 pagesC Language QR v2sadariahNo ratings yet

- Verilog HDL: A Solution For EverybodyDocument30 pagesVerilog HDL: A Solution For EverybodyLKNo ratings yet

- VHDL LectureDocument90 pagesVHDL LectureWendhz ÜüNo ratings yet

- Lecture 1-VHDLDocument15 pagesLecture 1-VHDLSultanus Salehin ,152431No ratings yet

- Circuit and System Design: Verilog Hardware Description LanguageDocument132 pagesCircuit and System Design: Verilog Hardware Description LanguagePhước MinhNo ratings yet

- Chapter 3Document29 pagesChapter 3Kiran GunasegaranNo ratings yet

- VHDL 101: Everything you Need to Know to Get StartedFrom EverandVHDL 101: Everything you Need to Know to Get StartedRating: 2.5 out of 5 stars2.5/5 (2)

- Digital Integrated Circuit Design Using Verilog and SystemverilogFrom EverandDigital Integrated Circuit Design Using Verilog and SystemverilogRating: 3 out of 5 stars3/5 (4)

- ORACLE PL/SQL Interview Questions You'll Most Likely Be AskedFrom EverandORACLE PL/SQL Interview Questions You'll Most Likely Be AskedRating: 5 out of 5 stars5/5 (1)

- Java/J2EE Interview Questions You'll Most Likely Be Asked: Job Interview Questions SeriesFrom EverandJava/J2EE Interview Questions You'll Most Likely Be Asked: Job Interview Questions SeriesNo ratings yet

- Orca Share Media1543907563876Document43 pagesOrca Share Media1543907563876Al AminNo ratings yet

- Preparation Summary For EEE Job Exams Taken by BUETDocument9 pagesPreparation Summary For EEE Job Exams Taken by BUETAl Amin100% (2)

- I'm Your Name: HelloDocument1 pageI'm Your Name: HelloAl AminNo ratings yet

- Your Name: Company, Location - Job TitleDocument1 pageYour Name: Company, Location - Job TitleGOVIND KUMARNo ratings yet

- Microelectronic - Circuits - Sedra - Smith - 7th - SOLUTIONS - MANUAL PDFDocument500 pagesMicroelectronic - Circuits - Sedra - Smith - 7th - SOLUTIONS - MANUAL PDFTiếnLộc Nguyễn79% (19)

- El G 4139 LN 3 OscillatorsDocument31 pagesEl G 4139 LN 3 OscillatorsashishmanyanNo ratings yet

- Problem Solving On D C Machines PDFDocument16 pagesProblem Solving On D C Machines PDFSelvaraj ParamasivanNo ratings yet

- Artificial Neural Network Trained Self-Tuning Pid Controller As A Cyber Security Protective Measure in Power GridDocument12 pagesArtificial Neural Network Trained Self-Tuning Pid Controller As A Cyber Security Protective Measure in Power GridAl AminNo ratings yet

- New Doc 2019-04-12 00.25.54Document20 pagesNew Doc 2019-04-12 00.25.54Al AminNo ratings yet

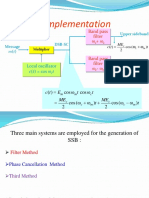

- Transmitters and Receivers: A Session For "Electronics and Telecommunications" A Fairfield University E-CourseDocument19 pagesTransmitters and Receivers: A Session For "Electronics and Telecommunications" A Fairfield University E-CourseAl AminNo ratings yet

- NMOS - Inverter - PDF Version 1Document50 pagesNMOS - Inverter - PDF Version 1Al AminNo ratings yet

- (Video Title) : FPGA Design For Embedded SystemsDocument8 pages(Video Title) : FPGA Design For Embedded SystemsAl AminNo ratings yet

- (Video Title) : FPGA Design For Embedded SystemsDocument9 pages(Video Title) : FPGA Design For Embedded SystemsAl AminNo ratings yet

- (Video Title) : FPGA Design For Embedded SystemsDocument15 pages(Video Title) : FPGA Design For Embedded SystemsAl AminNo ratings yet

- Combinational Logic Design 1Document31 pagesCombinational Logic Design 1jocansino4496No ratings yet

- Class 4Document19 pagesClass 4Al AminNo ratings yet

- (Video Title) : FPGA Design For Embedded SystemsDocument13 pages(Video Title) : FPGA Design For Embedded SystemsAl AminNo ratings yet

- (Sadiku) Practice Problem Solution PDFDocument176 pages(Sadiku) Practice Problem Solution PDFShakil Ahmed61% (140)

- Class 2 (B)Document40 pagesClass 2 (B)Al AminNo ratings yet

- Chapter 2Document82 pagesChapter 2Kavitha Selvaraj50% (2)

- Class - 6 - Pulse Modulation - 1Document29 pagesClass - 6 - Pulse Modulation - 1Al AminNo ratings yet

- Class 5 NoiseDocument14 pagesClass 5 NoiseAl AminNo ratings yet

- Class 5Document9 pagesClass 5Al AminNo ratings yet

- Lecture 5 and 6 Mist SpecialDocument26 pagesLecture 5 and 6 Mist SpecialGaffar KhanNo ratings yet

- Manual RouterBoard RB433Document11 pagesManual RouterBoard RB433Kike_PonsVidal0% (1)

- 74HC164 74HCT164: 1. General DescriptionDocument17 pages74HC164 74HCT164: 1. General DescriptionTDFRIOGRANDENo ratings yet

- 8085 Microprocessor Solutions Manual GaonkarDocument3 pages8085 Microprocessor Solutions Manual GaonkarChayanika Barman0% (1)

- Module 3:the Memory System: Courtesy: Text Book: Carl Hamacher 5 EditionDocument73 pagesModule 3:the Memory System: Courtesy: Text Book: Carl Hamacher 5 EditionRajkumarNo ratings yet

- Sheet 1Document6 pagesSheet 1Elsayed Hassan EmarahNo ratings yet

- PCB STACK UP LAYERS AND COMPONENTSDocument41 pagesPCB STACK UP LAYERS AND COMPONENTSLeonardo Garcia0% (1)

- EHB322E Digital Electronic Circuits Midterm Ii: 1) Consider A Boolean Function 8k 24kDocument3 pagesEHB322E Digital Electronic Circuits Midterm Ii: 1) Consider A Boolean Function 8k 24kfurkan çelikNo ratings yet

- I2C Communication Protocol TutorialDocument8 pagesI2C Communication Protocol TutorialKenet Naray Rosales100% (2)

- Boolean Algebra and Logic SimplificationDocument79 pagesBoolean Algebra and Logic SimplificationAmitava Sarder100% (1)

- How to program your access card for Hu satellite TVDocument8 pagesHow to program your access card for Hu satellite TVriadelectro100% (1)

- Siddharth Uni UG BCA Syllabus PDFDocument41 pagesSiddharth Uni UG BCA Syllabus PDFShyamdeen Maurya100% (2)

- Module 7: Memory Interfacing: Cs/Ece/Eee/Instr F241 - Microprocessor Programming & InterfacingDocument4 pagesModule 7: Memory Interfacing: Cs/Ece/Eee/Instr F241 - Microprocessor Programming & InterfacingsanaullahNo ratings yet

- The Dma Chip 8237aDocument24 pagesThe Dma Chip 8237aatorresh090675No ratings yet

- Design of Fast Dadda Multiplier Using Vedic Mathematics: Sathish@svce - Ac.inDocument8 pagesDesign of Fast Dadda Multiplier Using Vedic Mathematics: Sathish@svce - Ac.inSohini RoyNo ratings yet

- Manuel S. Enverga University Foundation: Granted Autonomous StatusDocument4 pagesManuel S. Enverga University Foundation: Granted Autonomous StatusRonaldo MaañoNo ratings yet

- Update to Promate display panel specificationsDocument3 pagesUpdate to Promate display panel specificationsIonescu CristinaNo ratings yet

- Cs302 Assignment 2 SolutionDocument2 pagesCs302 Assignment 2 Solutionaamir shahzadNo ratings yet

- Verilog Notes (John Wawrzynek)Document26 pagesVerilog Notes (John Wawrzynek)h.moradmand4458No ratings yet

- Solutions: Solution 5.1Document14 pagesSolutions: Solution 5.1Pînzaru GheorgheNo ratings yet

- Trademarks: Mainboard User's ManualDocument42 pagesTrademarks: Mainboard User's ManualjonnyprNo ratings yet

- RTL Verilog Navabi PDFDocument294 pagesRTL Verilog Navabi PDFSiva chowdaryNo ratings yet

- B.Tech Digital Circuits & Systems Subject NotesDocument15 pagesB.Tech Digital Circuits & Systems Subject NotesAyush KavariyaNo ratings yet

- Lec04 - Types of RegistersDocument17 pagesLec04 - Types of RegistersBilal ImranNo ratings yet

- Setupapi Dev LogDocument546 pagesSetupapi Dev LogFriedrich Kurniawan Moja100% (1)

- Debug Port and ITPDocument70 pagesDebug Port and ITPpukymotto100% (1)

- LogDocument8 pagesLogsalam911No ratings yet

- DSP Seminar-ArchitectureDocument15 pagesDSP Seminar-ArchitectureanuNo ratings yet

- DRDODocument21 pagesDRDOAyush AgarwalNo ratings yet

- Universal Shift Register1Document25 pagesUniversal Shift Register1sandeep_03671% (7)

- Class 4 Computer Assignment June2010Document5 pagesClass 4 Computer Assignment June2010veebaNo ratings yet