Professional Documents

Culture Documents

Width of PMOS in CMOS Is 333.33nm And, W/L Ratio 2.77: Ans: For VDD 1.3V

Width of PMOS in CMOS Is 333.33nm And, W/L Ratio 2.77: Ans: For VDD 1.3V

Uploaded by

Akash Hiremath0 ratings0% found this document useful (0 votes)

12 views10 pagesThe document describes the design and simulation of 1-bit and 2-bit adders. It includes schematics of a full adder, 1-bit adder simulation, propagation delay and power calculations for 1-bit adder, schematic of a 2-bit adder using full adders, its simulation output, and propagation delay and power calculations for the 2-bit adder. The maximum propagation delay for the 1-bit adder is 52.435ps with power dissipation of 285.6782μW, while for the 2-bit adder it is 217.04ps with power of 484.938μW.

Original Description:

VLSI Digital Assignment

Original Title

VLSI DA3

Copyright

© © All Rights Reserved

Available Formats

PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentThe document describes the design and simulation of 1-bit and 2-bit adders. It includes schematics of a full adder, 1-bit adder simulation, propagation delay and power calculations for 1-bit adder, schematic of a 2-bit adder using full adders, its simulation output, and propagation delay and power calculations for the 2-bit adder. The maximum propagation delay for the 1-bit adder is 52.435ps with power dissipation of 285.6782μW, while for the 2-bit adder it is 217.04ps with power of 484.938μW.

Copyright:

© All Rights Reserved

Available Formats

Download as PDF, TXT or read online from Scribd

0 ratings0% found this document useful (0 votes)

12 views10 pagesWidth of PMOS in CMOS Is 333.33nm And, W/L Ratio 2.77: Ans: For VDD 1.3V

Width of PMOS in CMOS Is 333.33nm And, W/L Ratio 2.77: Ans: For VDD 1.3V

Uploaded by

Akash HiremathThe document describes the design and simulation of 1-bit and 2-bit adders. It includes schematics of a full adder, 1-bit adder simulation, propagation delay and power calculations for 1-bit adder, schematic of a 2-bit adder using full adders, its simulation output, and propagation delay and power calculations for the 2-bit adder. The maximum propagation delay for the 1-bit adder is 52.435ps with power dissipation of 285.6782μW, while for the 2-bit adder it is 217.04ps with power of 484.938μW.

Copyright:

© All Rights Reserved

Available Formats

Download as PDF, TXT or read online from Scribd

You are on page 1of 10

Akash Dayanand Hiremath

18BEC0361

1.

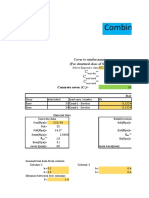

Ans: for VDD=1.3V

333.33

Width of PMOS in CMOS is 333.33nm And, W/L ratio= = 2.77

120

Akash Dayanand Hiremath

18BEC0361

Full Adder(1bit adder) Schematic

Akash Dayanand Hiremath

18BEC0361

Full Adder Symbol

Akash Dayanand Hiremath

18BEC0361

Full Adder Simulation Schematic,

Akash Dayanand Hiremath

18BEC0361

Output of Full Adder,

Akash Dayanand Hiremath

18BEC0361

Sum Fall Delay:

Tpdf = (50.75-50.74402) ns = 5.98 ps

Sum Rise Delay:

Tpdr = (100.25-100.24962) ns = 0.38 ps

TOTAL PROPAGATION DELAY of Sum Ds= (Tpdf+ Tpdr)/2= (5.98+0.38)/2 = 3.18 ps

Carry Fall Delay:

Tpdf = (50.75-50.80656) ns = 56.56 ps

Carry Rise Delay:

Tpdr = (100.25-100.29831) ns = 48.31 ps

TOTAL PROPAGATION DELAY of Carry Dc= (Tpdf+ Tpdr)/2= (56.56+48.31)/2 = 52.435 ps

Therefore, TOTAL PROPAGATION DELAY = max(Ds,Dc) = 52.435 ps

And, Total Power dissipated = 285.6782 µW

Akash Dayanand Hiremath

18BEC0361

2-bit Adder Schematic using Full Adder Symbol

Akash Dayanand Hiremath

18BEC0361

Output of 2-bit Adder,

Akash Dayanand Hiremath

18BEC0361

S0 Fall Delay:

Tpdf = (150.75-50.78066) ns = 30.66 ps

S0 Rise Delay:

Tpdr = (50.75-50.9019) ns = 151.9 ps

TOTAL PROPAGATION DELAY of Sum Ds0= (Tpdf+ Tpdr)/2= (30.66+151.9)/2 = 91.28 ps

S1 Fall Delay:

Tpdf = (50.75-50.766581) ns = 15.81 ps

S1 Rise Delay:

Tpdr = (100.25-100.45123) ns = 201.23 ps

TOTAL PROPAGATION DELAY of Sum Ds= (Tpdf+ Tpdr)/2= (15.81+201.23)/2 = 217.04 ps

Carry Fall Delay:

Tpdf = (50.75-50.83525) ns = 85.25 ps

Carry Rise Delay:

Tpdr = (100.25-100.35939) ns = 109.39 ps

TOTAL PROPAGATION DELAY of Carry Dc= (Tpdf+ Tpdr)/2= (85.25+109.39)/2 = 194.64 ps

Akash Dayanand Hiremath

18BEC0361

Therefore, TOTAL PROPAGATION DELAY = max(Ds0,Ds1,Dc) = 217.04 ps

And, Total Power dissipated = 484.938 µW

You might also like

- DLD Project Report CompleteDocument10 pagesDLD Project Report CompleteAMMAD MAHMOODNo ratings yet

- Akash Dayanand Hiremath 18BEC0361Document11 pagesAkash Dayanand Hiremath 18BEC0361Akash HiremathNo ratings yet

- Vlsi Da1 PDFDocument4 pagesVlsi Da1 PDFAkash HiremathNo ratings yet

- Height of MAC Above Ground, FT: S V 1.2 LOF VDocument20 pagesHeight of MAC Above Ground, FT: S V 1.2 LOF VJonathan CruzNo ratings yet

- UEE Assignments 1,2,3Document11 pagesUEE Assignments 1,2,3Kaone OsupileNo ratings yet

- Timber DesignDocument62 pagesTimber DesignLovely Brecio CalixtroNo ratings yet

- Q5. Member and Joint StressesDocument8 pagesQ5. Member and Joint StressesJames PriceNo ratings yet

- Exercises Belt Drives 3Document14 pagesExercises Belt Drives 3ZIZIPHO MNTUMNINo ratings yet

- ExCoté - 121219 - SolutionDocument6 pagesExCoté - 121219 - Solutionnikko verquinNo ratings yet

- Transmission Line DesignDocument16 pagesTransmission Line DesignManoj Sunchauri100% (2)

- Conexion Columna - PedestalDocument5 pagesConexion Columna - PedestalAlejandro OspinaNo ratings yet

- The University of Jordan: Optical Communication & LaserDocument5 pagesThe University of Jordan: Optical Communication & LaserhasssanNo ratings yet

- Thermodynamic CalculationDocument10 pagesThermodynamic CalculationAnilNo ratings yet

- Solutions Manual Internal Combustion Engines: Applied Thermosciences ch07Document15 pagesSolutions Manual Internal Combustion Engines: Applied Thermosciences ch07swastik jenaNo ratings yet

- Study:Screen Output: Result SummaryDocument31 pagesStudy:Screen Output: Result SummaryRamkumarNo ratings yet

- 125 X 125 X 10 Use Two Angle BarDocument1 page125 X 125 X 10 Use Two Angle BarNebu BildanNo ratings yet

- Concorde LG AnalysisDocument16 pagesConcorde LG AnalysisChris AntoniadesNo ratings yet

- ELX303 - Past Paper - May 2019 - Solutions PDFDocument12 pagesELX303 - Past Paper - May 2019 - Solutions PDFEmmanuel LazoNo ratings yet

- PDF 1692430940631Document3 pagesPDF 1692430940631Maths loveNo ratings yet

- Beam DesignDocument21 pagesBeam DesignKent XyrellNo ratings yet

- E Crane FoundationDocument1 pageE Crane FoundationPriodeep ChowdhuryNo ratings yet

- Previous Next Prep FindDocument1 pagePrevious Next Prep Findaliceblair707No ratings yet

- Design of Purlins and TrussesDocument46 pagesDesign of Purlins and TrussesWarrenPresBerdugo100% (1)

- Line Length (M) Bearing AB BC CD DE Unknown EA Unknown: Given The Tabulated Data Below, Determine The Unknown QuantitiesDocument6 pagesLine Length (M) Bearing AB BC CD DE Unknown EA Unknown: Given The Tabulated Data Below, Determine The Unknown QuantitiesJoshua Onin OlivenzaNo ratings yet

- Transmission and Distribution DesignDocument31 pagesTransmission and Distribution DesignER.Master Ajay RimalNo ratings yet

- Quiz 2: Due: February 7, 2021Document10 pagesQuiz 2: Due: February 7, 2021Theodore TolmanNo ratings yet

- Workbook Workbook Workbook Workbook Workbook: Try Yourself QuestionsDocument14 pagesWorkbook Workbook Workbook Workbook Workbook: Try Yourself QuestionsarunNo ratings yet

- Basic GKDocument7 pagesBasic GKSIVAPATHASEKARANNo ratings yet

- Refrigeration and Air Condition Homework and Experiment N°19Document2 pagesRefrigeration and Air Condition Homework and Experiment N°19Alicia M Benitez BNo ratings yet

- Cascode Amplifier: PART 1: Sizing ChartDocument9 pagesCascode Amplifier: PART 1: Sizing ChartAhmad KamalNo ratings yet

- Second CheckingDocument12 pagesSecond CheckingKing Cyruz PabloNo ratings yet

- Voltage Drop and Balancing of LoadsDocument26 pagesVoltage Drop and Balancing of LoadsLaurence PilienNo ratings yet

- Uvvis Spectroscopy: Case Study - Azobenzene E/Z IsomersDocument13 pagesUvvis Spectroscopy: Case Study - Azobenzene E/Z IsomersGressya ShavanaNo ratings yet

- ESE-2018 Mains Test Series: Mechanical Engineering Test No: 11Document38 pagesESE-2018 Mains Test Series: Mechanical Engineering Test No: 11VivekMishraNo ratings yet

- Recitation#3 Solution 1 8Document11 pagesRecitation#3 Solution 1 8William AlikisNo ratings yet

- Workshop CalculationDocument8 pagesWorkshop CalculationAnonymous 43pDZuRNo ratings yet

- Tugas 1Document21 pagesTugas 1Dinanurika FitrianaNo ratings yet

- Degine of 2 Stage CMOs Opamp......Document14 pagesDegine of 2 Stage CMOs Opamp......Vinay MishraNo ratings yet

- Optimization HWDocument6 pagesOptimization HWAnthony ParkNo ratings yet

- Design of Tension Member: If Arranged in Chain Bolting Enter Pitch and Gauge Distance As ZeroDocument5 pagesDesign of Tension Member: If Arranged in Chain Bolting Enter Pitch and Gauge Distance As ZeroPrasad SamantNo ratings yet

- Presentation1 - Lab 5Document24 pagesPresentation1 - Lab 5VenkateshPatnalaNo ratings yet

- d75d7 t780 Industrial Electronics n4 Memo Apr 2019Document6 pagesd75d7 t780 Industrial Electronics n4 Memo Apr 2019mdxlivepsyNo ratings yet

- Eee Exam 3solutionDocument9 pagesEee Exam 3solutionIsaac DmNo ratings yet

- Hat Section - Cold Formed - DSMDocument3 pagesHat Section - Cold Formed - DSMAmrar AbdelazizNo ratings yet

- Summary Elbow 2 PSB A MinusDocument1 pageSummary Elbow 2 PSB A Minusaditya kokoNo ratings yet

- Bridge PortionDocument16 pagesBridge PortionNagara SelvarajNo ratings yet

- Diseño de Vigas Continuas Carga - VerticalDocument119 pagesDiseño de Vigas Continuas Carga - Verticalvanessa pinosNo ratings yet

- Lecture 5 BisaresDocument6 pagesLecture 5 BisaresTopher Palma0% (1)

- Combined Footing Design ES en 2015Document24 pagesCombined Footing Design ES en 2015Dino AbdelaNo ratings yet

- Solution To Tutorial 1, 2, 3, & 4Document19 pagesSolution To Tutorial 1, 2, 3, & 4Pearlyn Tiko TeoNo ratings yet

- DesignDocument13 pagesDesignAnshulGuptaNo ratings yet

- Mosfet Power Dissipation CalculationDocument8 pagesMosfet Power Dissipation CalculationDinesh DangiNo ratings yet

- ME463 - Lab Exercise 1: Design of V-BeltDocument4 pagesME463 - Lab Exercise 1: Design of V-BeltJoshua OliverNo ratings yet

- Department of Electrical EngineeringDocument9 pagesDepartment of Electrical EngineeringArslan ArshadNo ratings yet

- Beam 1 and 2Document7 pagesBeam 1 and 2christinemangahas5No ratings yet

- Full Thermodynamics For Engineers Si Edition 1St Edition Kroos Solutions Manual Online PDF All ChapterDocument44 pagesFull Thermodynamics For Engineers Si Edition 1St Edition Kroos Solutions Manual Online PDF All Chapterbeckymcnally977023100% (1)

- MD INC AZ TVD VS N/S E/W: EjercicioDocument9 pagesMD INC AZ TVD VS N/S E/W: EjerciciorodrigoNo ratings yet

- Andrei PogiDocument3 pagesAndrei PogiRaven Justine BalilaNo ratings yet

- Acdc - Ac Generator - Lecture Notes 7Document53 pagesAcdc - Ac Generator - Lecture Notes 7Cllyan ReyesNo ratings yet

- Chapter 6 Problems Solutions: 6.1 (A) Synchronous Speed For 60-Hz Excitation Is Given by (6.12)Document25 pagesChapter 6 Problems Solutions: 6.1 (A) Synchronous Speed For 60-Hz Excitation Is Given by (6.12)PedroPerezLirolaNo ratings yet

- Ripple Carry and Carry Lookahead Addition and Subtraction CircuitsDocument19 pagesRipple Carry and Carry Lookahead Addition and Subtraction CircuitsSurya KanthNo ratings yet

- Skee 2263 Final Exam 1920-2 SDocument19 pagesSkee 2263 Final Exam 1920-2 SNG JIAN RONG A20EE0177No ratings yet

- Co 4&5 Questionbank SE23Document4 pagesCo 4&5 Questionbank SE23Rajeshwari R PNo ratings yet

- Computer Architecture Lab: Name - Roll - 12100119111 Section - (B) Computer Science EngineeringDocument71 pagesComputer Architecture Lab: Name - Roll - 12100119111 Section - (B) Computer Science EngineeringSankhadeep ChakrabartiNo ratings yet

- Talafy 2020Document11 pagesTalafy 2020Vani YamaniNo ratings yet

- Constructing A Binary CalculatorDocument10 pagesConstructing A Binary Calculatormusa ahmedNo ratings yet

- Digital Principels and System DesignDocument53 pagesDigital Principels and System Designnofeelingrahul100% (1)

- DLD GTU Question Bank: Chapter-1 Binary SystemDocument5 pagesDLD GTU Question Bank: Chapter-1 Binary Systemnirav34No ratings yet

- Verilog ExercisesheetDocument6 pagesVerilog ExercisesheetFionna ImmaculateNo ratings yet

- Department of Biomedical Engineering CSE-221L - Digital Logic DesignDocument8 pagesDepartment of Biomedical Engineering CSE-221L - Digital Logic DesignMUHAMMAD ARSLANNo ratings yet

- Half Adder: Lab Experiment # 13Document6 pagesHalf Adder: Lab Experiment # 13Saad khanNo ratings yet

- Register Transfer and MicrooperationsDocument18 pagesRegister Transfer and MicrooperationsShivam RaiNo ratings yet

- Mips AluDocument27 pagesMips AluoromosNo ratings yet

- 9Document10 pages9Sachin RathodNo ratings yet

- Introduction To CMOS VLSI Design (E158) Lecture 16: Datapath Functional UnitsDocument26 pagesIntroduction To CMOS VLSI Design (E158) Lecture 16: Datapath Functional UnitsAnil KumarNo ratings yet

- Lecture2 Chapter4 - BCD To Excess-3 Code Converter DesignDocument19 pagesLecture2 Chapter4 - BCD To Excess-3 Code Converter DesignAyesha HussainNo ratings yet

- Convert Gray Code 101011 Into Its Binary Equivalent. Gray Code: 1 0 1 0 1 1 Binary Code: 1 1 0 0 1 0Document23 pagesConvert Gray Code 101011 Into Its Binary Equivalent. Gray Code: 1 0 1 0 1 1 Binary Code: 1 1 0 0 1 0khadarbasha.n nNo ratings yet

- A Very Fast and Low Power Carry Select Adder CircuitDocument4 pagesA Very Fast and Low Power Carry Select Adder CircuitKanaga VaratharajanNo ratings yet

- EE537-Spring 2020 Digital Integrated Circuit Design Instructor: Engr. Dr. Nasir MohyuddinDocument2 pagesEE537-Spring 2020 Digital Integrated Circuit Design Instructor: Engr. Dr. Nasir Mohyuddinrao rehNo ratings yet

- Csci 136 Computer Architecture IIDocument28 pagesCsci 136 Computer Architecture IIcristopherNo ratings yet

- LSU EE 3755 - Fall 2012 - Computer Organization Verilog Notes 4 - Synthesis Under ConstructionDocument20 pagesLSU EE 3755 - Fall 2012 - Computer Organization Verilog Notes 4 - Synthesis Under ConstructionMerupu DebbaNo ratings yet

- Experiment No - Ripple Carry Full AdderDocument3 pagesExperiment No - Ripple Carry Full AdderNikhil PawarNo ratings yet

- Maj2-202-T102 - KeyDocument9 pagesMaj2-202-T102 - KeymirzabaaNo ratings yet

- hw6 Solutions PDFDocument13 pageshw6 Solutions PDFJohn Jeshurun SamonteNo ratings yet

- Digital Logic Design Lab 02 ReportDocument12 pagesDigital Logic Design Lab 02 ReportUmer huzaifaNo ratings yet

- Register Transfer and Microperations Part 1Document13 pagesRegister Transfer and Microperations Part 1Mohammed Al-RahmaweeNo ratings yet

- 4-Bit Carry Look Ahead Adder: Abstract - An Adder Is An Essential Part of The CentralDocument4 pages4-Bit Carry Look Ahead Adder: Abstract - An Adder Is An Essential Part of The CentralShahriar MahmudNo ratings yet

- Question BankDocument9 pagesQuestion BankNiyas AhamedNo ratings yet

- 4-Bit Carry Look Ahead AdderDocument5 pages4-Bit Carry Look Ahead AdderluqmansulymanNo ratings yet