Professional Documents

Culture Documents

Hiperfet Power Mosfets Isoplus247 Ixfr 4N100Q V 1000 V I 3.5 A R 3.0 T 200Ns

Uploaded by

طبعيعزيزالنفسOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Hiperfet Power Mosfets Isoplus247 Ixfr 4N100Q V 1000 V I 3.5 A R 3.0 T 200Ns

Uploaded by

طبعيعزيزالنفسCopyright:

Available Formats

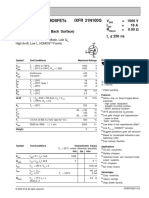

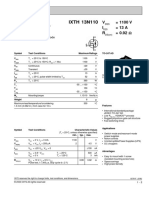

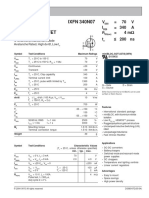

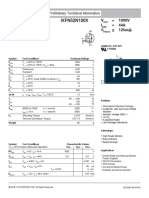

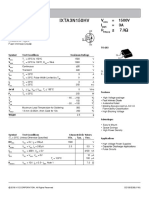

HiPerFETTM Power MOSFETs IXFR 4N100Q VDSS = 1000 V

ISOPLUS247TM ID25 = 3.5 A

RDS(on) = 3.0 Ω

(Electrically Isolated Backside)

trr ≤ 200ns

N-Channel Enhancement Mode

Avalanche Rated, Low Qg, High dv/dt

Preliminary Data

Symbol Test Conditions Maximum Ratings ISOPLUS 247TM

E153432

VDSS TJ = 25°C to 150°C 1000 V

VDGR TJ = 25°C to 150°C; RGS = 1 MΩ 1000 V

VGS Continuous ±20 V

VGSM Transient ±30 V Isolated backside*

ID25 TC = 25°C 3.5 A

IDM TC = 25°C, Note 1 16 A

IAR TC = 25°C 4 A G = Gate D = Drain

S = Source

EAR TC = 25°C 20 mJ

EAS TC = 25°C 700 mJ * Patent pending

dv/dt IS ≤ IDM, di/dt ≤ 100 A/µs, VDD ≤ VDSS 5 V/ns

TJ ≤ 150°C, RG = 2 Ω

PD TC = 25°C 80 W Features

z

Silicon chip on Direct-Copper-Bond

TJ -55 ... +150 °C

substrate

TJM 150 °C - High power dissipation

Tstg -55 ... +150 °C - Isolated mounting surface

- 2500V electrical isolation

TL 1.6 mm (0.063 in.) from case for 10 s 300 °C z

Low drain to tab capacitance(<30pF)

VISOL 50/60 Hz, RMS t = 1 min 2500 V~ z

Low RDS (on) HDMOSTM process

z

Weight 5 g Rugged polysilicon gate cell structure

z

Rated for Unclamped Inductive Load

Switching (UIS)

z

Fast intrinsic Rectifier

Symbol Test Conditions Characteristic Values Applications

z

(TJ = 25°C, unless otherwise specified) DC-DC converters

min. typ. max. z

Battery chargers

z

VDSS VGS = 0 V, ID = 1mA 1000 V Switched-mode and resonant-mode

power supplies

VGS(th) VDS = VGS, ID = 1.5 mA 3.0 5.0 V z

DC choppers

z

IGSS VGS = ±20 VDC, VDS = 0 ±100 nA AC motor control

IDSS VDS = VDSS TJ = 25°C 50 µA Advantages

VGS = 0 V TJ = 125°C 1 mA z

Easy assembly

z

RDS(on) VGS = 10 V, ID = IT 3.0 Ω Space savings

Notes 2, 3 z

High power density

© 2002 IXYS All rights reserved DS98860A(12/02)

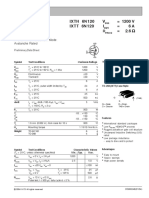

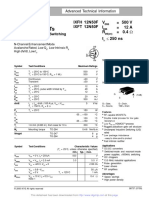

IXFR 4N100Q

Symbol Test Conditions Characteristic Values

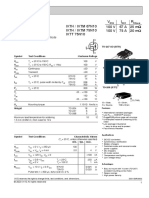

ISOPLUS 247TM Outline

(TJ = 25°C, unless otherwise specified)

min. typ. max.

gfs V DS = 10 V; ID = IT Notes 2, 3 1.5 2.5 S

Ciss 1050 pF

Coss VGS = 0 V, VDS = 25 V, f = 1 MHz 120 pF

Crss 30 pF

td(on) 17 ns

tr VGS = 10 V, VDS = 0.5 • VDSS, ID = IT 15 ns

td(off) RG = 2 Ω (External), Notes 2, 3 32 ns

Terminals: 1 - Gate

tf 18 ns 2 - Drain (Collector)

3 - Source (Emitter)

4 - Drain (Collector)

Qg(on) 39 nC

Dim. Millimeter Inches

Qgs VGS = 10 V, VDS = 0.5 • VDSS, ID = IT 9 nC Min. Max. Min. Max.

Notes 2, 3 A 4.83 5.21 .190 .205

Qgd 22 nC A1 2.29 2.54 .090 .100

A2 1.91 2.16 .075 .085

RthJC 1.57 K/W b 1.14 1.40 .045 .055

b1 1.91 2.13 .075 .084

b2 2.92 3.12 .115 .123

RthCK 0.15 K/W

C 0.61 0.80 .024 .031

D 20.80 21.34 .819 .840

E 15.75 16.13 .620 .635

e 5.45 BSC .215 BSC

L 19.81 20.32 .780 .800

L1 3.81 4.32 .150 .170

Source-Drain Diode Characteristic Values

Q 5.59 6.20 .220 0.244

(TJ = 25°C, unless otherwise specified) R 4.32 4.83 .170 .190

Symbol Test Conditions min. typ. max.

IS VGS = 0 V 4 A See IXFH4N100Q data sheet for

Characterisitic curves.

ISM Repetitive; Note 1 16 A

VSD IF = IS, VGS = 0 V, Notes 2, 3 1.5 V

t rr 250 ns

QRM 0.52 µC

IF = 50A,-di/dt = 100 A/µs, VR = 100 V

IRM 1.8 A

Note: 1. Pulse width limited by TJM

2. Pulse test, t ≤ 300 µs, duty cycle d ≤ 2 %

3. IT = 2 A

IXYS reserves the right to change limits, test conditions, and dimensions.

IXYS MOSFETs and IGBTs are covered by one or more of the following U.S. patents: 4,835,592 4,881,106 5,017,508 5,049,961 5,187,117 5,486,715 6,306,728B1

4,850,072 4,931,844 5,034,796 5,063,307 5,237,481 5,381,025

You might also like

- 978-0393617542 Research MethodsDocument18 pages978-0393617542 Research MethodsReccebacaNo ratings yet

- Ixys S A0008598295 1-2273062Document6 pagesIxys S A0008598295 1-2273062birricaNo ratings yet

- Transiator - 10N100 PDocument6 pagesTransiator - 10N100 Pivanaldo tavaresNo ratings yet

- Littelfuse Discrete Mosfets N-Channel Standard Ixt 6n120 Datasheet PDFDocument5 pagesLittelfuse Discrete Mosfets N-Channel Standard Ixt 6n120 Datasheet PDFalllim88No ratings yet

- Hiperfet Power Mosfets Isoplus247 Ixfr 70N15: (Electrically Isolated Backside)Document3 pagesHiperfet Power Mosfets Isoplus247 Ixfr 70N15: (Electrically Isolated Backside)William moreNo ratings yet

- Ixfh 12N100FDocument2 pagesIxfh 12N100FAnonymous lQyR2IWNo ratings yet

- DatasheetDocument5 pagesDatasheetanggaNo ratings yet

- IXFH40N50Q2Document5 pagesIXFH40N50Q2gustavo jesus JimenezNo ratings yet

- IXFN38N100Q2 DatasheetzDocument4 pagesIXFN38N100Q2 DatasheetzРаушан СалмахамедовNo ratings yet

- Ixfn110N60P3: V 600V I 90A Polar3 Hiperfet Power MosfetDocument5 pagesIxfn110N60P3: V 600V I 90A Polar3 Hiperfet Power MosfetCristhian CairaNo ratings yet

- IXTH13N110Document3 pagesIXTH13N110Morteza JafarzadehNo ratings yet

- Ixfk40N90P Ixfx40N90P: V 900V I 40A 210M T 300Ns Polar Power Mosfet HiperfetDocument4 pagesIxfk40N90P Ixfx40N90P: V 900V I 40A 210M T 300Ns Polar Power Mosfet Hiperfetnildo137 SANTOSNo ratings yet

- Ixta TP56N15TDocument5 pagesIxta TP56N15TPablo AllosiaNo ratings yet

- Hiperrf Power Mosfets: Ixfh 12N50F Ixft 12N50FDocument2 pagesHiperrf Power Mosfets: Ixfh 12N50F Ixft 12N50FdtramirNo ratings yet

- Hiperfet Power Mosfets Q-Class Ixfn 27N80Q V 800 V I 27 A 320 MDocument2 pagesHiperfet Power Mosfets Q-Class Ixfn 27N80Q V 800 V I 27 A 320 MJosephSyNo ratings yet

- Igbt 050A, 1200v, Ixyh50n120c3Document6 pagesIgbt 050A, 1200v, Ixyh50n120c3Manuel SierraNo ratings yet

- Littelfuse Discrete MOSFETs N-Channel HiPerFETs IX-1856371Document7 pagesLittelfuse Discrete MOSFETs N-Channel HiPerFETs IX-1856371basheer almetwakelNo ratings yet

- Ixys S A0006610714 1-2272993Document6 pagesIxys S A0006610714 1-2272993basheer almetwakelNo ratings yet

- Standard Power MOSFET: N-Channel Enhancement ModeDocument5 pagesStandard Power MOSFET: N-Channel Enhancement ModetvsamsungjpNo ratings yet

- TP3N120 DatasheetDocument1 pageTP3N120 DatasheetAdvance CNC TechnologiesNo ratings yet

- Ixgh48N60B3D1: Genx3 600V Igbt With DiodeDocument7 pagesIxgh48N60B3D1: Genx3 600V Igbt With DiodevalidaeNo ratings yet

- High Voltage Power Mosfets: Ixta 3N120 Ixtp 3N120Document4 pagesHigh Voltage Power Mosfets: Ixta 3N120 Ixtp 3N120Man DarkNo ratings yet

- IXGR120N60BDocument5 pagesIXGR120N60BAndré CrowleyNo ratings yet

- Genx3 600V Igbt With Diode Ixgh48N60C3D1: V 600V I 48A V T 38NsDocument7 pagesGenx3 600V Igbt With Diode Ixgh48N60C3D1: V 600V I 48A V T 38NsBuitinės Technikos RemontasNo ratings yet

- Megamos Fet: Irfp 470 V 500 V I 24 A R 0.23Document2 pagesMegamos Fet: Irfp 470 V 500 V I 24 A R 0.23Plat RNo ratings yet

- Standard Power MOSFET: IRFP 254 V 250 V I 23 A R 0.14Document2 pagesStandard Power MOSFET: IRFP 254 V 250 V I 23 A R 0.14Fran Javi Vila DiazNo ratings yet

- Ixgr 60N60C2Document6 pagesIxgr 60N60C2isaiasvaNo ratings yet

- 100N50P IXFB Power Mosfet PDFDocument5 pages100N50P IXFB Power Mosfet PDFHưng HQNo ratings yet

- 50N60C3D1Document7 pages50N60C3D1ali ülküNo ratings yet

- Ixys S A0005444474 1-2272941Document5 pagesIxys S A0005444474 1-2272941karndis kanthaNo ratings yet

- Littelfuse Discrete MOSFETs N-Channel Ultra Juncti-1856493Document8 pagesLittelfuse Discrete MOSFETs N-Channel Ultra Juncti-1856493basheer almetwakelNo ratings yet

- XPT Igbt 600V Genx3 W/ Diode Ixxh50N60B3D1: V 600V I 50A V T 135NsDocument7 pagesXPT Igbt 600V Genx3 W/ Diode Ixxh50N60B3D1: V 600V I 50A V T 135Nsali ülküNo ratings yet

- IXFH20N85XDocument6 pagesIXFH20N85XNana Dwi WahanaNo ratings yet

- Megamos Fet: V I R 100 V 67 A 25 M 100 V 75 A 20 M Ixth / Ixtm 67N10 Ixth / Ixtm 75N10 Ixtt 75N10Document4 pagesMegamos Fet: V I R 100 V 67 A 25 M 100 V 75 A 20 M Ixth / Ixtm 67N10 Ixth / Ixtm 75N10 Ixtt 75N10nithinmundackal3623No ratings yet

- IX-1856538Document7 pagesIX-1856538faridNo ratings yet

- Hiperfet Power Mosfets Q-Class: V 1000 V I 4 A R 3.0 T 250 Ns Ixfa 4N100Q Ixfp 4N100QDocument5 pagesHiperfet Power Mosfets Q-Class: V 1000 V I 4 A R 3.0 T 250 Ns Ixfa 4N100Q Ixfp 4N100QSigitusmantoro-jks UsmantoroNo ratings yet

- Ixtq52n30p Ixtt52n30pDocument5 pagesIxtq52n30p Ixtt52n30pinfo.wenamericaNo ratings yet

- Ixfk100n65x2 100a 650v N Kanal Mosfet To264 DatasheetDocument6 pagesIxfk100n65x2 100a 650v N Kanal Mosfet To264 Datasheetbasheer almetwakelNo ratings yet

- 20N50Document4 pages20N50raveendraNo ratings yet

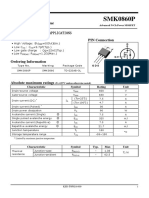

- SMK1060P: Switching Regulator ApplicationsDocument8 pagesSMK1060P: Switching Regulator ApplicationsEdmundo VázquezNo ratings yet

- Hiperfet Power Mosfets: Ixfh14N80 Ixfh15N80Document6 pagesHiperfet Power Mosfets: Ixfh14N80 Ixfh15N80LowayNo ratings yet

- IXFN73N30 IXYSCorporationDocument4 pagesIXFN73N30 IXYSCorporationpuji yatmiNo ratings yet

- Hiperfet Power Mosfets: V I R Ixfh/Ixfm 11 N80 800 V 11 A 0.95 Ixfh/Ixfm 13 N80 800 V 13 A 0.80 T 250 NsDocument4 pagesHiperfet Power Mosfets: V I R Ixfh/Ixfm 11 N80 800 V 11 A 0.95 Ixfh/Ixfm 13 N80 800 V 13 A 0.80 T 250 NsZdravko OberanNo ratings yet

- High Current Megamos Fet: Ixtk 120N25 V 250 V I 120 A 20 MDocument6 pagesHigh Current Megamos Fet: Ixtk 120N25 V 250 V I 120 A 20 MMohamed belhasanNo ratings yet

- High Current Megamos Fet: Ixtk 120N25 V 250 V I 120 A 20 MDocument6 pagesHigh Current Megamos Fet: Ixtk 120N25 V 250 V I 120 A 20 MMohamed belhasanNo ratings yet

- 27M - 650V Sic Cascode - Uj3C065030T3S Description: Maximum RatingsDocument10 pages27M - 650V Sic Cascode - Uj3C065030T3S Description: Maximum RatingsАндрей ПоляковNo ratings yet

- Truesemi-TSD5N65M C382376Document10 pagesTruesemi-TSD5N65M C382376carlos riveraNo ratings yet

- HPA600R760MB Silicon N-Channel Power MOSFET: General DescriptionDocument10 pagesHPA600R760MB Silicon N-Channel Power MOSFET: General DescriptionlfnoseNo ratings yet

- SLW9N90C: 900V N-Channel MOSFETDocument7 pagesSLW9N90C: 900V N-Channel MOSFETJavier VelasquezNo ratings yet

- Littelfuse Discrete MOSFETs N-Channel Linear IXT 110N20 Datasheet PDFDocument6 pagesLittelfuse Discrete MOSFETs N-Channel Linear IXT 110N20 Datasheet PDFRace Automotive ElectronicsNo ratings yet

- NDS351AN N-Channel Logic Level Enhancement Mode Field Effect TransistorDocument6 pagesNDS351AN N-Channel Logic Level Enhancement Mode Field Effect TransistorStefania FerrarioNo ratings yet

- S2PF380N65R: N-Channel 650V Enhancement Mode Power MOSFETDocument8 pagesS2PF380N65R: N-Channel 650V Enhancement Mode Power MOSFETMaikel Borges IglesiasNo ratings yet

- CM 03 XDocument5 pagesCM 03 Xfrancisval20100% (1)

- SMK0860P: Switching Regulator ApplicationsDocument8 pagesSMK0860P: Switching Regulator ApplicationsBilier Diaz CabreraNo ratings yet

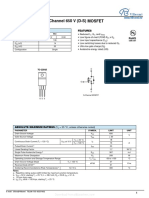

- N-Channel 0 V (D-S) Mosfet: Features Product SummaryDocument8 pagesN-Channel 0 V (D-S) Mosfet: Features Product SummaryErasmo Franco SNo ratings yet

- Hiperfet Power MosfetsDocument4 pagesHiperfet Power MosfetsMamadou djibril BaNo ratings yet

- UF3C065040K3S Data SheetDocument11 pagesUF3C065040K3S Data Sheetsultaniwahid240No ratings yet

- hv32hd 9dyDocument6 pageshv32hd 9dyFernando SotoNo ratings yet

- 0 TPQDT 8 ZT 8 GKF 9 GF 0 R 4 KZ 366 K 2 KyDocument6 pages0 TPQDT 8 ZT 8 GKF 9 GF 0 R 4 KZ 366 K 2 Kyniw7777No ratings yet

- Tikkun Kisay HaShemDocument47 pagesTikkun Kisay HaShemYochananMauritzHummasti100% (1)

- MBenz SLK350 R171 272 RepairDocument1,922 pagesMBenz SLK350 R171 272 RepairJavier ViudezNo ratings yet

- 3286306Document5 pages3286306Sanjit OracleTrainingNo ratings yet

- Docs Grails Org 4 0 0 Guide Single HTMLDocument296 pagesDocs Grails Org 4 0 0 Guide Single HTMLlicface13No ratings yet

- Philips Cdr775Document50 pagesPhilips Cdr775Tomasz SkrzypińskiNo ratings yet

- Pengaruh PH Ekstraksi Terhadap Rendemen, Sifat Fisiko-Kimia Dan Fungsional Konsentrat Protein KACANG GUDE (Cajanus Cajan (L.) Millsp.)Document11 pagesPengaruh PH Ekstraksi Terhadap Rendemen, Sifat Fisiko-Kimia Dan Fungsional Konsentrat Protein KACANG GUDE (Cajanus Cajan (L.) Millsp.)Rezaa RezNo ratings yet

- Too Early! by Anton Pavlovich ChekhovDocument4 pagesToo Early! by Anton Pavlovich Chekhovapi-19787590No ratings yet

- Sheet - PDF 3Document4 pagesSheet - PDF 3Nazar JabbarNo ratings yet

- Calydracomfort PiDocument16 pagesCalydracomfort PiionNo ratings yet

- 5.1 CompleteDocument11 pages5.1 Completenyanmoemyat2010No ratings yet

- Tea Board of India PDFDocument18 pagesTea Board of India PDFDebasish RazNo ratings yet

- Naaladiyar: Watch Free MoviesDocument6 pagesNaaladiyar: Watch Free MoviesVijayaLakshmi IyerNo ratings yet

- Walkie Talkie - 10 Codes - CommUSADocument1 pageWalkie Talkie - 10 Codes - CommUSASakthi VasuNo ratings yet

- Cornelia - Mima Maxey (1933) PDFDocument97 pagesCornelia - Mima Maxey (1933) PDFrodrigo estrasulasNo ratings yet

- Saes TABLEDocument13 pagesSaes TABLERiyaz BasheerNo ratings yet

- Brunswick Manual Preinstalacion GSXDocument33 pagesBrunswick Manual Preinstalacion GSXroberto dominguezNo ratings yet

- Segment Reporting Decentralized Operations and Responsibility Accounting SystemDocument34 pagesSegment Reporting Decentralized Operations and Responsibility Accounting SystemalliahnahNo ratings yet

- Eating Well: Snacks For 1-4 Year OldsDocument42 pagesEating Well: Snacks For 1-4 Year OldsAndreea AndreiNo ratings yet

- Intro To StarsDocument37 pagesIntro To StarsENo ratings yet

- 12 - Chepter 5Document11 pages12 - Chepter 5KhaireddineNo ratings yet

- Pricelist LV Siemens 2019 PDFDocument96 pagesPricelist LV Siemens 2019 PDFBerlianiNo ratings yet

- Aeroacoustic Optimization of Wind Turbine Airfoils by Combining Thermographic and Acoustic Measurement DataDocument4 pagesAeroacoustic Optimization of Wind Turbine Airfoils by Combining Thermographic and Acoustic Measurement DatamoussaouiNo ratings yet

- IIRDocument2 pagesIIRJagan FaithNo ratings yet

- MikroC PRO For DsPIC30Document9 pagesMikroC PRO For DsPIC30ivcal20No ratings yet

- Organizational Behavior Exam 2 Practice QuestionsDocument1 pageOrganizational Behavior Exam 2 Practice QuestionsSydney EverettNo ratings yet

- معالجات ستاذ يزنDocument11 pagesمعالجات ستاذ يزنammerNo ratings yet

- Capital MarketDocument5 pagesCapital MarketBalamanichalaBmcNo ratings yet

- MaekawaDocument2 pagesMaekawabhaskar_chintakindiNo ratings yet

- Research ProposalDocument2 pagesResearch Proposalsmh9662No ratings yet