Professional Documents

Culture Documents

Fdpc8016S: Powertrench Power Clip 25V Asymmetric Dual N-Channel Mosfet

Uploaded by

RDOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Fdpc8016S: Powertrench Power Clip 25V Asymmetric Dual N-Channel Mosfet

Uploaded by

RDCopyright:

Available Formats

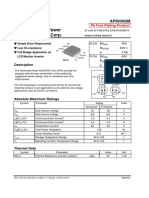

FDPC8016S PowerTrench® Power Clip

October 2013

FDPC8016S

PowerTrench® Power Clip

25V Asymmetric Dual N-Channel MOSFET

Features General Description

Q1: N-Channel This device includes two specialized N-Channel MOSFETs in a

Max rDS(on) = 3.8 mΩ at VGS = 10 V, ID = 20 A dual package. The switch node has been internally connected to

Max rDS(on) = 4.7 mΩ at VGS = 4.5 V, ID = 18 A enable easy placement and routing of synchronous buck

converters. The control MOSFET (Q1) and synchronous

Q2: N-Channel

SyncFETTM (Q2) have been designed to provide optimal power

Max rDS(on) = 1.4 mΩ at VGS = 10 V, ID = 35 A efficiency.

Max rDS(on) = 1.7 mΩ at VGS = 4.5 V, ID = 32 A

Applications

Low inductance packaging shortens rise/fall times, resulting in

lower switching losses Computing

MOSFET integration enables optimum layout for lower circuit Communications

inductance and reduced switch node ringing General Purpose Point of Load

RoHS Compliant

PIN1 PIN1 PAD10

V+(HSD)

HSG LSG HSG LSG

GR SW GR SW

SW

PAD9

GND(LSS) SW

V+ V+ SW

V+ SW V+ SW

Top Power Clip 5X6 Bottom

Pin Name Description Pin Name Description Pin Name Description

1 HSG High Side Gate 3,4,10 V+(HSD) High Side Drain 8 LSG Low Side Gate

2 GR Gate Return 5,6,7 SW Switching Node, Low Side Drain 9 GND(LSS) Low Side Source

MOSFET Maximum Ratings TA = 25 °C unless otherwise noted

Symbol Parameter Q1 Q2 Units

VDS Drain to Source Voltage 25Note5 25 V

VGS Gate to Source Voltage ±12 ±12 V

Drain Current -Continuous TC = 25 °C 60 100

ID -Continuous TA = 25 °C 20Note1a 35Note1b A

-Pulsed TA = 25 °C (Note 4) 75 140

EAS Single Pulse Avalanche Energy (Note 3) 73 216 mJ

Power Dissipation for Single Operation TC = 25 °C 21 42

PD W

Power Dissipation for Single Operation TA = 25 °C 2.1Note1a 2.3 Note1b

TJ, TSTG Operating and Storage Junction Temperature Range -55 to +150 °C

Thermal Characteristics

RθJC Thermal Resistance, Junction to Case 6.0 3.0

RθJA Thermal Resistance, Junction to Ambient 60Note1a 55Note1b °C/W

RθJA Thermal Resistance, Junction to Ambient 130Note1c 120Note1d

©2013 Fairchild Semiconductor Corporation 1 www.fairchildsemi.com

FDPC8016S Rev.C7

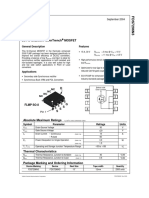

FDPC8016S PowerTrench® Power Clip

Package Marking and Ordering Information

Device Marking Device Package Reel Size Tape Width Quantity

05OD/15OD FDPC8016S Power Clip 56 13 ” 12 mm 3000 units

Electrical Characteristics TJ = 25 °C unless otherwise noted

Symbol Parameter Test Conditions Type Min Typ Max Units

Off Characteristics

ID = 250 μA, VGS = 0 V Q1 25

BVDSS Drain to Source Breakdown Voltage V

ID = 1 mA, VGS = 0 V Q2 25

ΔBVDSS Breakdown Voltage Temperature ID = 250 μA, referenced to 25 °C Q1 24

mV/°C

ΔTJ Coefficient ID = 10 mA, referenced to 25 °C Q2 28

VDS = 20 V, VGS = 0 V Q1 1 μA

IDSS Zero Gate Voltage Drain Current

VDS = 20 V, VGS = 0 V Q2 500 μA

VGS = 12 V/-8 V, VDS= 0 V Q1 ±100 nA

IGSS Gate to Source Leakage Current

VGS = 12 V/-8 V, VDS= 0 V Q2 ±100 nA

On Characteristics

VGS = VDS, ID = 250 μA Q1 0.8 1.3 2.5

VGS(th) Gate to Source Threshold Voltage V

VGS = VDS, ID = 1 mA Q2 1.1 1.5 2.5

ΔVGS(th) Gate to Source Threshold Voltage ID = 250 μA, referenced to 25 °C Q1 -4

mV/°C

ΔTJ Temperature Coefficient ID = 10 mA, referenced to 25 °C Q2 -3

VGS = 10V, ID = 20 A 2.8 3.8

VGS = 4.5 V, ID = 18 A Q1 3.4 4.7

VGS = 10 V, ID = 20 A,TJ =125 °C 3.9 5.3

rDS(on) Drain to Source On Resistance mΩ

VGS = 10V, ID = 35 A 1.1 1.4

VGS = 4.5 V, ID = 32 A Q2 1.3 1.7

VGS = 10 V, ID = 35 A ,TJ =125 °C 1.5 1.9

VDS = 5 V, ID = 20 A Q1 182

gFS Forward Transconductance S

VDS = 5 V, ID = 35 A Q2 241

Dynamic Characteristics

Q1 1695 2375

Ciss Input Capacitance Q1: pF

Q2 4715 6600

VDS = 13 V, VGS = 0 V, f = 1 MHZ

Q1 495 710

Coss Output Capacitance pF

Q2 1195 1675

Q2:

VDS = 13 V, VGS = 0 V, f = 1 MHZ Q1 54 100

Crss Reverse Transfer Capacitance pF

Q2 159 290

Q1 0.1 0.4 1.2

Rg Gate Resistance Ω

Q2 0.1 0.5 1.5

Switching Characteristics

Q1 8 16

td(on) Turn-On Delay Time ns

Q2 13 24

Q1:

Q1 2 10

tr Rise Time VDD = 13 V, ID = 20 A, RGEN = 6 Ω ns

Q2 4 10

Q2: Q1 24 38

td(off) Turn-Off Delay Time ns

Q2 38 61

VDD = 13 V, ID = 35 A, RGEN = 6 Ω

Q1 2 10

tf Fall Time ns

Q2 3 10

Q1 25 35

Qg Total Gate Charge VGS = 0 V to 10 V nC

Q1 Q2 67 94

V = 13 V, ID Q1 11 16

Qg Total Gate Charge VGS = 0 V to 4.5 V DD nC

= 20 A Q2 31 44

Q2 Q1 3.4

Qgs Gate to Source Gate Charge VDD = 13 V, ID nC

Q2 10

= 35 A Q1 2.2

Qgd Gate to Drain “Miller” Charge nC

Q2 6.3

©2013 Fairchild Semiconductor Corporation 2 www.fairchildsemi.com

FDPC8016S Rev.C7

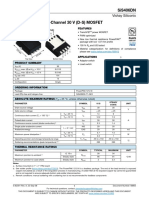

FDPC8016S PowerTrench® Power Clip

Electrical Characteristics TJ = 25 °C unless otherwise noted

Symbol Parameter Test Conditions Type Min Typ Max Units

Drain-Source Diode Characteristics

VGS = 0 V, IS = 20 A (Note 2) Q1 0.8 1.2

VSD Source to Drain Diode Forward Voltage V

VGS = 0 V, IS = 35 A (Note 2) Q2 0.8 1.2

Q1 Q1 25 40

trr Reverse Recovery Time ns

IF = 20 A, di/dt = 100 A/μs Q2 33 53

Q2 Q1 10 20

Qrr Reverse Recovery Charge nC

IF = 35 A, di/dt = 200 A/μs Q2 31 50

Notes:

1.RθJA is determined with the device mounted on a 1 in2 pad 2 oz copper pad on a 1.5 x 1.5 in. board of FR-4 material. RθJC is guaranteed by design while RθCA is determined by

the user's board design.

b. 55 °C/W when mounted on

a. 60 °C/W when mounted on

a 1 in2 pad of 2 oz copper

a 1 in2 pad of 2 oz copper

SF

SS

SS

SF

DS

DF

DS

DF

G

G

c. 130 °C/W when mounted on a d. 120 °C/W when mounted on a

minimum pad of 2 oz copper minimum pad of 2 oz copper

SF

SS

DS

DF

G

SF

SS

DF

DS

G

2 Pulse Test: Pulse Width < 300 μs, Duty cycle < 2.0%.

3. Q1 :EAS of 73 mJ is based on starting TJ = 25 oC; N-ch: L = 3 mH, IAS = 7 A, VDD = 30 V, VGS = 10 V. 100% test at L= 0.1 mH, IAS = 24 A.

Q2: EAS of 216 mJ is based on starting TJ = 25 oC; N-ch: L = 3 mH, IAS = 12 A, VDD = 25 V, VGS = 10 V. 100% test at L= 0.1 mH, IAS = 39 A.

4. Pulsed Id limited by junction temperature, td<=10 us. Please refer to SOA curve for more details.

5. The continuous VDS rating is 25 V; However, a pulse of 30 V peak voltage for no longer than 100 ns duration at 600 KHz frequency can be applied.

©2013 Fairchild Semiconductor Corporation 3 www.fairchildsemi.com

FDPC8016S Rev.C7

FDPC8016S PowerTrench® Power Clip

Typical Characteristics (Q1 N-Channel) TJ = 25°C unless otherwise noted

75 5

VGS = 10 V PULSE DURATION = 80 μs

DRAIN TO SOURCE ON-RESISTANCE

DUTY CYCLE = 0.5% MAX

60 4

ID, DRAIN CURRENT (A)

VGS = 2.5 V

VGS = 4.5 V

NORMALIZED

45 3

VGS = 3.5 V

VGS = 3 V

30 2 VGS = 3 V

VGS = 2.5 V

15 1

PULSE DURATION = 80 μs

VGS = 3.5 V VGS = 4.5 V VGS = 10 V

DUTY CYCLE = 0.5% MAX

0 0

0.0 0.2 0.4 0.6 0.8 1.0 0 15 30 45 60 75

VDS, DRAIN TO SOURCE VOLTAGE (V) ID, DRAIN CURRENT (A)

Figure 1. On Region Characteristics Figure 2. Normalized On-Resistance

vs. Drain Current and Gate Voltage

1.6 12

ID = 20 A PULSE DURATION = 80 μs

DRAIN TO SOURCE ON-RESISTANCE

1.5

SOURCE ON-RESISTANCE (mΩ)

VGS = 10 V DUTY CYCLE = 0.5% MAX

1.4 9

rDS(on), DRAIN TO

ID = 20 A

1.3

NORMALIZED

1.2

6

1.1

TJ = 125 oC

1.0

3

0.9

TJ = 25 oC

0.8

0.7 0

-75 -50 -25 0 25 50 75 100 125 150 1 2 3 4 5 6 7 8 9 10

TJ, JUNCTION TEMPERATURE (oC) VGS, GATE TO SOURCE VOLTAGE (V)

Figure 3. Normalized On Resistance Figure 4. On-Resistance vs. Gate to

vs. Junction Temperature Source Voltage

75 100

PULSE DURATION = 80 μs

IS, REVERSE DRAIN CURRENT (A)

VDS = 5 V VGS = 0 V

DUTY CYCLE = 0.5% MAX

60 10

ID, DRAIN CURRENT (A)

45 1

TJ = 150 oC

TJ = 150 oC TJ = 25 oC

30 0.1

TJ = 25 oC

15 0.01

TJ = -55 oC

TJ = -55 oC

0 0.001

1.0 1.5 2.0 2.5 3.0 0.0 0.2 0.4 0.6 0.8 1.0

VGS, GATE TO SOURCE VOLTAGE (V) VSD, BODY DIODE FORWARD VOLTAGE (V)

Figure 5. Transfer Characteristics Figure 6. Source to Drain Diode

Forward Voltage vs. Source Current

©2013 Fairchild Semiconductor Corporation 4 www.fairchildsemi.com

FDPC8016S Rev.C7

FDPC8016S PowerTrench® Power Clip

Typical Characteristics (Q1 N-Channel) TJ = 25°C unless otherwise noted

10 10000

VGS, GATE TO SOURCE VOLTAGE (V)

ID = 20 A

8

VDD = 13 V

CAPACITANCE (pF)

1000 Ciss

6

VDD = 10 V

Coss

4

VDD = 15 V 100

2 f = 1 MHz

VGS = 0 V Crss

0 10

0 6 12 18 24 30 0.1 1 10 25

Qg, GATE CHARGE (nC) VDS, DRAIN TO SOURCE VOLTAGE (V)

Figure 7. Gate Charge Characteristics Figure 8. Capacitance vs. Drain

to Source Voltage

30 70

60

IAS, AVALANCHE CURRENT (A)

ID, DRAIN CURRENT (A)

TJ = 25 oC

50

10 VGS = 10 V

40

TJ = 100 oC

VGS = 4.5 V

30

20

TJ = 125 oC o

RθJC = 6.0 C/W

10

1 0

0.001 0.01 0.1 1 10 100 25 50 75 100 125 150

o

tAV, TIME IN AVALANCHE (ms) TC, CASE TEMPERATURE ( C)

Figure 9. Unclamped Inductive Figure 10. Maximum Continuous Drain

Switching Capability Current vs. Case Temperature

500 5000

P(PK), PEAK TRANSIENT POWER (W)

SINGLE PULSE

100 o

RθJC = 6.0 C/W

ID, DRAIN CURRENT (A)

10 μs 1000 o

TC = 25 C

10 100 μs

THIS AREA IS

LIMITED BY rDS(on)

1 ms 100

SINGLE PULSE 10 ms

1 TJ = MAX RATED DC

RθJC = 6.0 oC/W

CURVE BENT TO

TC = 25 oC MEASURED DATA

0.1 10

-5 -4 -3 -2 -1

0.1 1 10 80 10 10 10 10 10 1

VDS, DRAIN to SOURCE VOLTAGE (V) t, PULSE WIDTH (sec)

Figure 11. Forward Bias Safe Figure 12. Single Pulse Maximum

Operating Area Power Dissipation

©2013 Fairchild Semiconductor Corporation 5 www.fairchildsemi.com

FDPC8016S Rev.C7

FDPC8016S PowerTrench® Power Clip

Typical Characteristics (Q1 N-Channel) TJ = 25°C unless otherwise noted

2

r(t), NORMALIZED EFFECTIVE TRANSIENT

DUTY CYCLE-DESCENDING ORDER

1

D = 0.5

THERMAL RESISTANCE

0.2 PDM

0.1

0.05

0.02

0.1 t1

0.01

t2

NOTES:

SINGLE PULSE ZθJC (t) = r(t) x RθJc

RθJC = 6.0 oC/W

DUTY FACTOR: D = t1/ t2

0.01 TJ -TC = PDM x ZθJC(t)

0.005

-5 -4 -3 -2 -1

10 10 10 10 10 1

t, RECTANGULAR PULSE DURATION (sec)

Figure 13. Junction-to-Case Transient Thermal Response Curve

©2013 Fairchild Semiconductor Corporation 6 www.fairchildsemi.com

FDPC8016S Rev.C7

FDPC8016S PowerTrench® Power Clip

Typical Characteristics (Q2 N-Channel) TJ = 25 °C unless otherwise noted

140 6.0

DRAIN TO SOURCE ON-RESISTANCE

VGS = 10 V PULSE DURATION = 80 μs

120 VGS = 2.5 V DUTY CYCLE = 0.5% MAX

VGS = 4.5 V

ID, DRAIN CURRENT (A)

100 4.5

VGS = 3.5 V

NORMALIZED

80 VGS = 3 V

3.0

60 VGS = 2.5 V VGS = 3 V

40

1.5

20 PULSE DURATION = 80 μs

DUTY CYCLE = 0.5% MAX VGS = 3.5 V VGS = 4.5 V VGS = 10 V

0 0.0

0.0 0.2 0.4 0.6 0.8 0 20 40 60 80 100 120 140

VDS, DRAIN TO SOURCE VOLTAGE (V) ID, DRAIN CURRENT (A)

Figure 14. On- Region Characteristics Figure 15. Normalized on-Resistance vs. Drain

Current and Gate Voltage

1.6 5

ID = 35 A PULSE DURATION = 80 μs

DRAIN TO SOURCE ON-RESISTANCE

1.5

SOURCE ON-RESISTANCE (mΩ)

VGS = 10 V DUTY CYCLE = 0.5% MAX

4

1.4

ID = 35 A

rDS(on), DRAIN TO

1.3

NORMALIZED

3

1.2

1.1

2

1.0 TJ = 125 oC

0.9 1

0.8 TJ = 25 oC

0.7 0

-75 -50 -25 0 25 50 75 100 125 150 1 2 3 4 5 6 7 8 9 10

TJ, JUNCTION TEMPERATURE (oC) VGS, GATE TO SOURCE VOLTAGE (V)

Figure 16. Normalized On-Resistance Figure 17. On-Resistance vs. Gate to

vs. Junction Temperature Source Voltage

140 200

100

IS, REVERSE DRAIN CURRENT (A)

VDS = 5 V VGS = 0 V

120

TJ = 25 oC 10

ID, DRAIN CURRENT (A)

100

TJ = 125 oC

TJ = 125 oC

80 1

TJ = -55 oC

60 TJ = 25 oC

0.1

40

TJ = -55 oC

0.01

20 PULSE DURATION = 80 μs

DUTY CYCLE = 0.5% MAX

0 0.001

1 2 3 4 0.0 0.2 0.4 0.6 0.8 1.0

VGS, GATE TO SOURCE VOLTAGE (V) VSD, BODY DIODE FORWARD VOLTAGE (V)

Figure 18. Transfer Characteristics Figure 19. Source to Drain Diode

Forward Voltage vs. Source Current

©2013 Fairchild Semiconductor Corporation 7 www.fairchildsemi.com

FDPC8016S Rev.C7

FDPC8016S PowerTrench® Power Clip

Typical Characteristics (Q2 N-Channel) TJ = 25°C unless otherwise noted

10 10000

VGS, GATE TO SOURCE VOLTAGE (V)

ID = 35 A

8 Ciss

VDD = 13 V

CAPACITANCE (pF)

1000

6

Coss

VDD = 10 V

4

VDD = 15 V 100

f = 1 MHz Crss

2

VGS = 0 V

0 10

0 20 40 60 80 0.1 1 10 25

Qg, GATE CHARGE (nC) VDS, DRAIN TO SOURCE VOLTAGE (V)

Figure 20. Gate Charge Characteristics Figure 21. Capacitance vs. Drain

to Source Voltage

50 160

140

IAS, AVALANCHE CURRENT (A)

TJ = 25 oC ID, DRAIN CURRENT (A)

120

VGS = 10 V

100

10

TJ = 100 oC 80

Limited by Package

60

o

RθJC = 3.0 C/W VGS = 4.5 V

TJ = 125 oC 40

20

1 0

0.001 0.01 0.1 1 10 100 1000 25 50 75 100 125 150

o

tAV, TIME IN AVALANCHE (ms) TC, CASE TEMPERATURE ( C)

Figure 22. Unclamped Inductive Figure 23. Maximum Continuous Drain

Switching Capability Current vs. Case Temperature

1000 10000

SINGLE PULSE

P(PK), PEAK TRANSIENT POWER (W)

o

RθJC = 3.0 C/W

10 μs

ID, DRAIN CURRENT (A)

100 TC = 25 C

o

1000

100 μs

10 THIS AREA IS

LIMITED BY rDS(on) 1 ms

10 ms 100

SINGLE PULSE

1 TJ = MAX RATED DC

RθJC = 3.0 oC/W

CURVE BENT TO

TC = 25 oC MEASURED DATA

0.1 10

-5 -4 -3 -2 -1

0.1 1 10 80 10 10 10 10 10 1

VDS, DRAIN to SOURCE VOLTAGE (V) t, PULSE WIDTH (sec)

Figure 24. Forward Bias Safe Figure 25. Single Pulse Maximum

Operating Area Power Dissipation

©2013 Fairchild Semiconductor Corporation 8 www.fairchildsemi.com

FDPC8016S Rev.C7

FDPC8016S PowerTrench® Power Clip

Typical Characteristics (Q2 N-Channel) TJ = 25 °C unless otherwise noted

2

r(t), NORMALIZED EFFECTIVE TRANSIENT

DUTY CYCLE-DESCENDING ORDER

1

D = 0.5

THERMAL RESISTANCE

0.2

0.1 PDM

0.05

0.1 0.02

0.01

t1

t2

NOTES:

ZθJC (t) = r(t) x RθJc

0.01 SINGLE PULSE RθJC = 3.0 oC/W

DUTY FACTOR: D = t1/ t2

TJ -TC = PDM x ZθJC(t)

0.003

-5 -4 -3 -2 -1

10 10 10 10 10 1

t, RECTANGULAR PULSE DURATION (sec)

Figure 26. Junction-to-Case Transient Thermal Response Curve

©2013 Fairchild Semiconductor Corporation 9 www.fairchildsemi.com

FDPC8016S Rev.C7

FDPC8016S PowerTrench® Power Clip

Typical Characteristics (continued)

SyncFETTM Schottky body diode

Characteristics

Fairchild’s SyncFETTM process embeds a Schottky diode in Schottky barrier diodes exhibit significant leakage at high tem-

parallel with PowerTrench® MOSFET. This diode exhibits similar perature and high reverse voltage. This will increase the power

characteristics to a discrete external Schottky diode in parallel in the device.

with a MOSFET. Figure 27 shows the reverses recovery

characteristic of the FDPC8016S.

-2

40 10

IDSS, REVERSE LEAKAGE CURRENT (A)

35

30 -3 TJ = 125 oC

10

25 TJ = 100 oC

CURRENT (A)

20 -4

di / dt = 200 A/μS 10

15

10

-5

5 10

TJ = 25 oC

0

-6

-5 10

50 100 150 200 250 300 350 400 0 5 10 15 20 25

TIME (ns) VDS, REVERSE VOLTAGE (V)

Figure 27. FDPC8016S SyncFETTM Body Figure 28. SyncFETTM Body Diode Reverse

Diode Reverse Recovery Characteristic Leakage vs. Drain-source Voltage

©2013 Fairchild Semiconductor Corporation 10 www.fairchildsemi.com

FDPC8016S Rev.C7

FDPC8016S PowerTrench® Power Clip

Dimensional Outline and Pad Layout

5.00

4.56

4.20

5.10 A

0.10 C 4.90

2X 1.27

PKG

B 4 3 2 1

CL

3.30

4 1

2.48

2.08

1.01

6.60

6.10 0.00 0.40

PKG CL 5.90 2.65 0.83

1.43

1.98

2.48

0.82

3.30

PIN #1 5 8 0.10 C 5 6 7 8

2X

INDICATOR TOP VIEW 0.75

SEE

1.01

1.53

0.00

1.08

1.48

1.53

2.29

DETAIL A

RECOMMENDED LAND PATTERN

SIDE VIEW

0.10 C A B

3.15±.05 0.05 C

3.81

1.27

0.51

5 6 7 8

0.65±.05 1.57±.05

NOTES: UNLESS OTHERWISE SPECIFIED

0.65±.05

2.46±.05

1.37±.05 A) DOES NOT FULLY CONFORM TO

0.53±.05 JEDEC REGISTRATION, MO-229,

0.91±.05 DATED 11/2001.

B) ALL DIMENSIONS ARE IN

0.48±.05

0.49±.05 MILLIMETERS.

4 3 2 1

C) DIMENSIONS DO NOT INCLUDE

0.51±.05 BURRS OR MOLD FLASH. MOLD

3.90±.05

FLASH OR BURRS DOES NOT

4.22±.05

EXCEED 0.10MM.

5.00±.05

D) DIMENSIONING AND TOLERANCING

BOTTOM VIEW PER ASME Y14.5M-1994.

E) DRAWING FILE NAME:

0.10 C

0.08 C

C

0.80 0.30 0.05

0.70 0.20 0.00

SEATING

PLANE

(SCALE: 2X)

©2013 Fairchild Semiconductor Corporation 11 www.fairchildsemi.com

FDPC8016S Rev.C7

FDPC8016S PowerTrench® Power Clip

TRADEMARKS

The following includes registered and unregistered trademarks and service marks, owned by Fairchild Semiconductor and/or its global subsidiaries, and is not

intended to be an exhaustive list of all such trademarks.

AccuPower™ F-PFS™ Sync-Lock™

AX-CAP®* FRFET® ® tm

®*

®

BitSiC™ Global Power ResourceSM PowerTrench

Build it Now™ GreenBridge™ PowerXS™

TinyBoost®

CorePLUS™ Green FPS™ Programmable Active Droop™

® TinyBuck®

CorePOWER™ Green FPS™ e-Series™ QFET

TinyCalc™

CROSSVOLT™ Gmax™ QS™

TinyLogic®

CTL™ GTO™ Quiet Series™

TINYOPTO™

Current Transfer Logic™ IntelliMAX™ RapidConfigure™

TinyPower™

DEUXPEED® ISOPLANAR™ ™ TinyPWM™

Dual Cool™ Marking Small Speakers Sound Louder

TinyWire™

EcoSPARK® and Better™ Saving our world, 1mW/W/kW at a time™

TranSiC™

EfficentMax™ MegaBuck™ SignalWise™

TriFault Detect™

ESBC™ MICROCOUPLER™ SmartMax™

TRUECURRENT®*

MicroFET™ SMART START™

® μSerDes™

MicroPak™ Solutions for Your Success™

®

Fairchild ® MicroPak2™ SPM

Fairchild Semiconductor® MillerDrive™ STEALTH™

MotionMax™ SuperFET® UHC®

FACT Quiet Series™

® mWSaver ®

SuperSOT™-3 Ultra FRFET™

FACT

OptoHiT™ SuperSOT™-6 UniFET™

FAST®

OPTOLOGIC® SuperSOT™-8 VCX™

FastvCore™

OPTOPLANAR ®

SupreMOS ® VisualMax™

FETBench™

SyncFET™ VoltagePlus™

FPS™

XS™

*Trademarks of System General Corporation, used under license by Fairchild Semiconductor.

DISCLAIMER

FAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE

RELIABILITY, FUNCTION, OR DESIGN. FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY

PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS.

THESE SPECIFICATIONS DO NOT EXPAND THE TERMS OF FAIRCHILD’S WORLDWIDE TERMS AND CONDITIONS, SPECIFICALLY THE WARRANTY

THEREIN, WHICH COVERS THESE PRODUCTS.

LIFE SUPPORT POLICY

FAIRCHILD’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE

EXPRESS WRITTEN APPROVAL OF FAIRCHILD SEMICONDUCTOR CORPORATION.

As used here in:

1. Life support devices or systems are devices or systems which, (a) are 2. A critical component in any component of a life support, device, or

intended for surgical implant into the body or (b) support or sustain life, system whose failure to perform can be reasonably expected to cause

and (c) whose failure to perform when properly used in accordance with the failure of the life support device or system, or to affect its safety or

instructions for use provided in the labeling, can be reasonably effectiveness.

expected to result in a significant injury of the user.

ANTI-COUNTERFEITING POLICY

Fairchild Semiconductor Corporation’s Anti-Counterfeiting Policy. Fairchild’s Anti-Counterfeiting Policy is also stated on our external website,

www.Fairchildsemi.com, under Sales Support.

Counterfeiting of semiconductor parts is a growing problem in the industry. All manufactures of semiconductor products are experiencing counterfeiting of their

parts. Customers who inadvertently purchase counterfeit parts experience many problems such as loss of brand reputation, substandard performance, failed

application, and increased cost of production and manufacturing delays. Fairchild is taking strong measures to protect ourselves and our customers from the

proliferation of counterfeit parts. Fairchild strongly encourages customers to purchase Fairchild parts either directly from Fairchild or from Authorized Fairchild

Distributors who are listed by country on our web page cited above. Products customers buy either from Fairchild directly or from Authorized Fairchild

Distributors are genuine parts, have full traceability, meet Fairchild’s quality standards for handing and storage and provide access to Fairchild’s full range of

up-to-date technical and product information. Fairchild and our Authorized Distributors will stand behind all warranties and will appropriately address and

warranty issues that may arise. Fairchild will not provide any warranty coverage or other assistance for parts bought from Unauthorized Sources. Fairchild is

committed to combat this global problem and encourage our customers to do their part in stopping this practice by buying direct or from authorized distributors.

PRODUCT STATUS DEFINITIONS

Definition of Terms

Datasheet Identification Product Status Definition

Datasheet contains the design specifications for product development. Specifications

Advance Information Formative / In Design may change in any manner without notice.

Datasheet contains preliminary data; supplementary data will be published at a later

Preliminary First Production date. Fairchild Semiconductor reserves the right to make changes at any time without

notice to improve design.

Datasheet contains final specifications. Fairchild Semiconductor reserves the right to

No Identification Needed Full Production

make changes at any time without notice to improve the design.

Datasheet contains specifications on a product that is discontinued by Fairchild

Obsolete Not In Production

Semiconductor. The datasheet is for reference information only.

Rev. I66

©2013 Fairchild Semiconductor Corporation 12 www.fairchildsemi.com

FDPC8016S Rev.C7

You might also like

- Medical Equipment List for District HospitalDocument60 pagesMedical Equipment List for District Hospitalramesh100% (1)

- Introduction To CommerceDocument30 pagesIntroduction To Commerceapi-24690719591% (11)

- Father Dámaso: María Clara Quotes in Noli Me TangereDocument11 pagesFather Dámaso: María Clara Quotes in Noli Me TangereSilver ArgentNo ratings yet

- Swancor 901 Data SheetDocument2 pagesSwancor 901 Data SheetErin Guillermo33% (3)

- Fdpc5018Sg: Powertrench Power Clip 30V Asymmetric Dual N-Channel MosfetDocument12 pagesFdpc5018Sg: Powertrench Power Clip 30V Asymmetric Dual N-Channel MosfetDima RozhencovNo ratings yet

- Fdms7698: N-Channel Powertrench MosfetDocument7 pagesFdms7698: N-Channel Powertrench MosfetAdrian Kim BabelaNo ratings yet

- Fdmc6679Az: P-Channel Powertrench MosfetDocument7 pagesFdmc6679Az: P-Channel Powertrench MosfetMahmoud ElrefaeyNo ratings yet

- Fdms7682: N-Channel Powertrench MosfetDocument8 pagesFdms7682: N-Channel Powertrench MosfetGustavo RodriguezNo ratings yet

- WSF3013Document10 pagesWSF3013Abu SaeedNo ratings yet

- FDMC7692: N-Channel Power Trench MosfetDocument6 pagesFDMC7692: N-Channel Power Trench MosfetHerdhis VegaNo ratings yet

- 2424 FDMS86300Document7 pages2424 FDMS86300Ivkan MarsovskiNo ratings yet

- Irf 9410Document7 pagesIrf 9410FaisaludinNo ratings yet

- 232 11643 0 Irf7105Document10 pages232 11643 0 Irf7105Natal2i2No ratings yet

- Integrado So8 IRF7309PbFDocument8 pagesIntegrado So8 IRF7309PbFjuanlopezzzz843No ratings yet

- 2SK3353Document5 pages2SK3353Minh PhamNo ratings yet

- Onsemiconductor Fds6679az Datasheets 0664Document6 pagesOnsemiconductor Fds6679az Datasheets 0664Yohandris FernandezNo ratings yet

- Fdc658Ap: Single P-Channel Logic Level Powertrench Mosfet - 30V, - 4A, 50MDocument5 pagesFdc658Ap: Single P-Channel Logic Level Powertrench Mosfet - 30V, - 4A, 50MfaberjetNo ratings yet

- K3377 NecDocument4 pagesK3377 NecsergeyNo ratings yet

- Fds6679Az P-Channel Powertrench Mosfet: - 30V, - 13A, 9M General Description FeaturesDocument6 pagesFds6679Az P-Channel Powertrench Mosfet: - 30V, - 13A, 9M General Description FeaturesEdgxr DxnielNo ratings yet

- FDS6679AZ DatasheetDocument6 pagesFDS6679AZ DatasheetMarivaldo NascimentoNo ratings yet

- P-Channel 60 V (D-S) MOSFET: Features Product SummaryDocument9 pagesP-Channel 60 V (D-S) MOSFET: Features Product SummaryMie Hijau Tanpa PengawetNo ratings yet

- SOP-8 Plastic-Encapsulate MOSFETS: N and P-Channel Enhancement Mode Power MOSFETDocument8 pagesSOP-8 Plastic-Encapsulate MOSFETS: N and P-Channel Enhancement Mode Power MOSFETFabian NestorNo ratings yet

- Irf 7416 GPBFDocument9 pagesIrf 7416 GPBFKrista TranNo ratings yet

- APM4548K: Features Pin DescriptionDocument13 pagesAPM4548K: Features Pin DescriptionMauricio MartinNo ratings yet

- Infineon IRF7416 DataSheet v01 01 enDocument10 pagesInfineon IRF7416 DataSheet v01 01 enGiancarlo Figueroa OyolaNo ratings yet

- Infineon-IRF7316-DataSheet-v01_01-ENDocument8 pagesInfineon-IRF7316-DataSheet-v01_01-ENPoon Electronic Training CentreNo ratings yet

- Integrado So8 IRF7316PbFDocument7 pagesIntegrado So8 IRF7316PbFjuanlopezzzz843No ratings yet

- Irf8707Pbf-1: Hexfet Power MosfetDocument9 pagesIrf8707Pbf-1: Hexfet Power MosfetPablo LloveraNo ratings yet

- FDMC 8884Document7 pagesFDMC 8884Kholit LitNo ratings yet

- Advanced Power Electronics Corp.: DescriptionDocument4 pagesAdvanced Power Electronics Corp.: DescriptionAbdul HadiNo ratings yet

- Fds4435Bz: P-Channel Powertrench MosfetDocument6 pagesFds4435Bz: P-Channel Powertrench MosfetKevin TateNo ratings yet

- SM1F03NSK SinopowerDocument11 pagesSM1F03NSK SinopowerleandroNo ratings yet

- AP0503GMT-HF DatasheetDocument4 pagesAP0503GMT-HF DatasheetAisya NurcahyaNo ratings yet

- SM4802DSK: Features Pin DescriptionDocument12 pagesSM4802DSK: Features Pin DescriptionRobson SilvaNo ratings yet

- FDMS3600S FairchildSemiconductorDocument16 pagesFDMS3600S FairchildSemiconductorvinuNo ratings yet

- NTP18N06 DDocument8 pagesNTP18N06 DKhan KakaNo ratings yet

- Onsemi FairchildDocument6 pagesOnsemi Fairchildpratik gautamNo ratings yet

- CBE6030LDocument8 pagesCBE6030LgdiliogNo ratings yet

- Data SheetDocument4 pagesData SheetVibhor KumarNo ratings yet

- FDMS0310AS FairchildSemiconductorDocument8 pagesFDMS0310AS FairchildSemiconductorThisal DamsikaNo ratings yet

- SM3316NSQG SinopowerDocument12 pagesSM3316NSQG SinopowerAndrey RossiNo ratings yet

- Apm4500 PDFDocument13 pagesApm4500 PDFFlavianoSilvaNo ratings yet

- Advanced Power Electronics Corp.: AP4511GMDocument7 pagesAdvanced Power Electronics Corp.: AP4511GMTuchilo ViorelNo ratings yet

- 9T16GH MOSFET CANAL N SMDDocument4 pages9T16GH MOSFET CANAL N SMDVictorManuelBernalBlancoNo ratings yet

- Irf 7403Document9 pagesIrf 7403Макс БелыйNo ratings yet

- Ap4n2r1mt V1Document6 pagesAp4n2r1mt V1Mar GaoNo ratings yet

- Advanced Power Electronics Corp.: DescriptionDocument4 pagesAdvanced Power Electronics Corp.: DescriptionGioVoTamNo ratings yet

- SSM 9930 MDocument8 pagesSSM 9930 Mtechnic repairNo ratings yet

- Fdc642P: Single P-Channel 2.5V Specified Powertrench MosfetDocument5 pagesFdc642P: Single P-Channel 2.5V Specified Powertrench MosfetdistefanoNo ratings yet

- Fairchild - Semiconductor FDMC8884 DatasheetDocument7 pagesFairchild - Semiconductor FDMC8884 DatasheetmirandowebsNo ratings yet

- Irf 9952Document10 pagesIrf 9952Acido CinicoNo ratings yet

- Fdd9407L - F085: N-Channel Logic Level Powertrench MosfetDocument7 pagesFdd9407L - F085: N-Channel Logic Level Powertrench Mosfetonis1 onis1No ratings yet

- SM4337NSKP Datasheet PDFDocument10 pagesSM4337NSKP Datasheet PDFJohn InfinityNo ratings yet

- AOSP21357Document5 pagesAOSP21357Carlos Roman MonkadaNo ratings yet

- Datasheet - HK Ap9930gm 1021318Document7 pagesDatasheet - HK Ap9930gm 1021318Wardana Herna AksaniNo ratings yet

- General Description Product Summary: 30V N-Channel SRFETDocument6 pagesGeneral Description Product Summary: 30V N-Channel SRFETwillys borjaNo ratings yet

- Generation V Technology Ultra Low On-Resistance Dual P-Channel Mosfet Surface Mount Available in Tape & Reel Dynamic DV/DT Rating Fast SwitchingDocument7 pagesGeneration V Technology Ultra Low On-Resistance Dual P-Channel Mosfet Surface Mount Available in Tape & Reel Dynamic DV/DT Rating Fast SwitchingMohammed BariNo ratings yet

- FDS7296N3 - 30V N-Channel PowerTrench MOSFETDocument7 pagesFDS7296N3 - 30V N-Channel PowerTrench MOSFETLangllyNo ratings yet

- Advanced Power Electronics Corp.: AP9T16GH/JDocument4 pagesAdvanced Power Electronics Corp.: AP9T16GH/JLucas GuzmanNo ratings yet

- Sis406Dn: Vishay SiliconixDocument13 pagesSis406Dn: Vishay SiliconixIvo MFNo ratings yet

- SM3317NSQA: Features Pin DescriptionDocument13 pagesSM3317NSQA: Features Pin DescriptionvannadioNo ratings yet

- General Description Product Summary: 30V P-Channel MOSFETDocument5 pagesGeneral Description Product Summary: 30V P-Channel MOSFETStoica VictorNo ratings yet

- 2SK4212Document7 pages2SK4212asohas77No ratings yet

- C Exercise Example3Document7 pagesC Exercise Example3RDNo ratings yet

- PD 06 Algorithms Practice AnswerDocument8 pagesPD 06 Algorithms Practice AnswerRDNo ratings yet

- C Exercise Example5Document4 pagesC Exercise Example5RDNo ratings yet

- PD 10 SelfTypeDocument7 pagesPD 10 SelfTypeRDNo ratings yet

- Computer Organization Exercise Answer5Document7 pagesComputer Organization Exercise Answer5RDNo ratings yet

- Computer Organization Exercise Answer8Document6 pagesComputer Organization Exercise Answer8RDNo ratings yet

- AND8327/D Stability Analysis in Multiple Loop Systems: Prepared by Christophe Basso, Stéphanie Conseil, Nicolas CyrDocument16 pagesAND8327/D Stability Analysis in Multiple Loop Systems: Prepared by Christophe Basso, Stéphanie Conseil, Nicolas CyrRDNo ratings yet

- Received May 3, 2010 First Revision Oct 7, 2010 Second Revision Jan 28, 2011 Third Revision Apr 28, 2011 Accepted May 4, 2011Document16 pagesReceived May 3, 2010 First Revision Oct 7, 2010 Second Revision Jan 28, 2011 Third Revision Apr 28, 2011 Accepted May 4, 2011RDNo ratings yet

- AC-AC Converters Circuit Control and Waveform AnalysisDocument55 pagesAC-AC Converters Circuit Control and Waveform AnalysisRDNo ratings yet

- The Influence of Online Product Reviews On Consumer Purchase Intentions: The Moderating Roles of Cognitive Need and Product KnowledgeDocument4 pagesThe Influence of Online Product Reviews On Consumer Purchase Intentions: The Moderating Roles of Cognitive Need and Product KnowledgeRDNo ratings yet

- MCP601/1R/2/3/4: 2.7V To 6.0V Single Supply CMOS Op AmpsDocument34 pagesMCP601/1R/2/3/4: 2.7V To 6.0V Single Supply CMOS Op AmpsMohan RajNo ratings yet

- Fdpc8016S: Powertrench Power Clip 25V Asymmetric Dual N-Channel MosfetDocument12 pagesFdpc8016S: Powertrench Power Clip 25V Asymmetric Dual N-Channel MosfetRDNo ratings yet

- Cyntec Co., LTD.: Power Choke Coil PIMB051H TypeDocument4 pagesCyntec Co., LTD.: Power Choke Coil PIMB051H TypeRDNo ratings yet

- Improve High-Current Sensing Accuracy with Optimized Pad LayoutDocument3 pagesImprove High-Current Sensing Accuracy with Optimized Pad LayoutRDNo ratings yet

- Low profile power choke coil for DC/DC convertersDocument3 pagesLow profile power choke coil for DC/DC convertersRDNo ratings yet

- Specification For Approval: Page 1 of 8Document8 pagesSpecification For Approval: Page 1 of 8RDNo ratings yet

- Verilog Primer SlidesDocument42 pagesVerilog Primer SlidesRDNo ratings yet

- High performance power choke coil for DC/DC convertersDocument3 pagesHigh performance power choke coil for DC/DC convertersRDNo ratings yet

- Electric Power System, Syllabus - Fall 2016Document3 pagesElectric Power System, Syllabus - Fall 2016RDNo ratings yet

- Snap-On EEDM504D ManualDocument15 pagesSnap-On EEDM504D ManualSnafu168No ratings yet

- Parts of The CellDocument3 pagesParts of The Cellapi-308745623No ratings yet

- Jesus Uplifts The PoorDocument10 pagesJesus Uplifts The Poor명연우No ratings yet

- Literature Review Sustainable DevelopmentDocument5 pagesLiterature Review Sustainable DevelopmentJade NelsonNo ratings yet

- HDFC Life InsuranceDocument12 pagesHDFC Life Insurancesaswat mohantyNo ratings yet

- KOLHAN UNIVERSITY B.Sc Zoology Semester I Exam 2021 Provisional Marks CardDocument2 pagesKOLHAN UNIVERSITY B.Sc Zoology Semester I Exam 2021 Provisional Marks CardSmritiNo ratings yet

- PDDDocument88 pagesPDDapi-336689769No ratings yet

- IB Chemistry 1 SL QuestionsDocument36 pagesIB Chemistry 1 SL QuestionsCamilla0% (3)

- Food Hydrocolloids: Long Chen, Yaoqi Tian, Yuxiang Bai, Jinpeng Wang, Aiquan Jiao, Zhengyu JinDocument11 pagesFood Hydrocolloids: Long Chen, Yaoqi Tian, Yuxiang Bai, Jinpeng Wang, Aiquan Jiao, Zhengyu JinManoel Divino Matta Jr.No ratings yet

- Sri Venkateswara Caterers Tiffin MenuDocument4 pagesSri Venkateswara Caterers Tiffin MenuJPDGLNo ratings yet

- Sixth CommandmentDocument26 pagesSixth CommandmentJewel Anne RentumaNo ratings yet

- DS 20180208 SG10 12KTL-M Datasheet V10 ENDocument2 pagesDS 20180208 SG10 12KTL-M Datasheet V10 ENRavi Ranjan VermaNo ratings yet

- CIE IGCSE BiologyDocument25 pagesCIE IGCSE Biologytgdzbspikio.comNo ratings yet

- The Good NurseDocument2 pagesThe Good NurseKiela Therese LabroNo ratings yet

- Drugs MnemonicsDocument6 pagesDrugs MnemonicsDarrylJavier100% (1)

- Lucy Mayienga CV RecentDocument3 pagesLucy Mayienga CV Recentlucy.mayiengaNo ratings yet

- Steam Blowing - Disturbance Factor Discusstion2 PDFDocument5 pagesSteam Blowing - Disturbance Factor Discusstion2 PDFchem_taNo ratings yet

- Department of Education Region X-Northern Mindanao 3rd Quarter Exam Cookery SY 2022-2023Document10 pagesDepartment of Education Region X-Northern Mindanao 3rd Quarter Exam Cookery SY 2022-2023SORAHAYDA ENRIQUEZNo ratings yet

- Alkana-1Document61 pagesAlkana-1ayundhaNo ratings yet

- Harman/kardon: Onyx Studio 3Document36 pagesHarman/kardon: Onyx Studio 3Thai Lam100% (1)

- BG 370 Operation & Maintenance ManualDocument32 pagesBG 370 Operation & Maintenance ManualRamasubramanian SankaranarayananNo ratings yet

- The Death Penalty-Literature ReviewDocument4 pagesThe Death Penalty-Literature Reviewapi-582834189No ratings yet

- Under The Oak Tree Part 2Document94 pagesUnder The Oak Tree Part 2suakasenaNo ratings yet

- Guide To Rural England - ShropshireDocument54 pagesGuide To Rural England - ShropshireTravel Publishing100% (2)

- SvagreementDocument28 pagesSvagreementRowena RayosNo ratings yet

- 17 Subcon RequirementsDocument38 pages17 Subcon RequirementsMohammed MinhajNo ratings yet