Professional Documents

Culture Documents

I V V V: PD F(S) VCO (T) (T) (T) (T)

Uploaded by

Helder CruzOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

I V V V: PD F(S) VCO (T) (T) (T) (T)

Uploaded by

Helder CruzCopyright:

Available Formats

DEPARTAMENTO DE ENGENHARIA ELECTROTÉCNICA

3º TESTE DE ELECTRÓNICA III (2012/2013)

3 DE JUNHO DE 2013 – SALA 1.17 EDIFÍCIO VII

17:00/18:15H

PROBLEM 1:

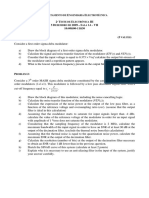

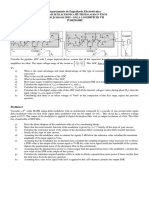

Consider a second order PLL with the block diagram depicted in Figure 1. The frequency of the

input frequency is 100 Mrad.s-1. Consider that the output frequency of the VCO as a function of the

( )

141 + 1 − e −2⋅( vc − 4V ) × 19 if vc > 4 V

control voltage is given by: ωOUT ( vc ) = 1 + 40 × ( vc − 0.5 ) if 0.5V < vc ≤ 4V [Mrad/s]

1 if vc ≤ 0.5V

ωi I (t) v (t) v (t)

d c

out

PD F(s) VCO

v (t)

in ωout

Figura 1: Block diagram of the PLL

a) Determine the linear model of the VCO for the input frequency value (represent in a graph the

VCO characteristic).

b) Draw the circuit of a 3-state phase-frequency detector with a charge pump current of 10 µA and

determine its linear model.

c) Considering that the loop filter (F(s)) has a pole and a zero, suggest a circuit that is capable of

implementing this transfer function, justify your answer by calculating the circuit transfer

function.

d) Explain why the static phase error of the PLL with this phase detector is 0.

e) Calculate the closed loop transfer function of the PLL and calculate the values of the

components of the loop filter in order to obtain a closed loop bandwidth of 0.1 Mrad/s and a

closed loop system critically damped.

f) Determine the lock-in range of the PLL assuming that the input signal frequency changes slowly

and that the maximum output voltage of the charge pump circuit is 4.5V.

g) If the input signal frequency of the PLL changes from 100 Mrad/s to 150 Mrad/s what is the new

value for the closed loop bandwidth of the PLL?

h) Explain how you would modify the PLL block diagram of figure 1 in order for the PLL to

produce an output frequency equal to 100 Mrad/s from an input frequency equal to 10 Mrad/s.

Calculate any new parameter value of the new block diagram.

You might also like

- Bootstrapping Your Op Amp Yields Wide Voltage Swings: DesignfeatureDocument8 pagesBootstrapping Your Op Amp Yields Wide Voltage Swings: DesignfeatureNishant_s123No ratings yet

- Op AmpDocument57 pagesOp AmpDivyanshu Yadav100% (1)

- Operational Amplifiers NewDocument20 pagesOperational Amplifiers NewLester Garcia100% (1)

- OscillatorsDocument90 pagesOscillatorsYesNo ratings yet

- Op Amp AssignmentDocument10 pagesOp Amp AssignmentJuan-Wian CoetzerNo ratings yet

- Boost Converter CourseworkDocument21 pagesBoost Converter Courseworkoopeoluwa_1No ratings yet

- CMOS Digital Integrated Circuits Analysis and Design 4th Edition Kang Solutions Manual DownloadDocument23 pagesCMOS Digital Integrated Circuits Analysis and Design 4th Edition Kang Solutions Manual DownloadRodolfo Wilson100% (28)

- PLL Intro 594a s05Document46 pagesPLL Intro 594a s05jaberyemeniNo ratings yet

- CHAPTER 2 - Oscillator PDFDocument26 pagesCHAPTER 2 - Oscillator PDFMuhd Deen0% (2)

- Rabaey Dig ElectronicsDocument4 pagesRabaey Dig ElectronicsRahul AgarwalNo ratings yet

- Scans of CircuitsDocument7 pagesScans of CircuitsTyler AbercicleNo ratings yet

- Phase Locked Loop: DT T M K TDocument3 pagesPhase Locked Loop: DT T M K ThimeshemraanNo ratings yet

- ELEC3400 Signal Processing Course NotesDocument68 pagesELEC3400 Signal Processing Course NotesCallan Fair BearNo ratings yet

- Jntu Hyd 2 2ece PDC Set 2Document18 pagesJntu Hyd 2 2ece PDC Set 2Krishna RamaNo ratings yet

- Lab 1 PDFDocument4 pagesLab 1 PDFTanmay KumarNo ratings yet

- DC-DC ConverterDocument6 pagesDC-DC ConverterAlecsandra RusuNo ratings yet

- ProblemSet5Solutions PDFDocument4 pagesProblemSet5Solutions PDFIván MartínezNo ratings yet

- Problem Solving of Power ElectronicsDocument4 pagesProblem Solving of Power ElectronicsAlca Li100% (1)

- 1DRDO Aptitude Paper Sept 2008Document13 pages1DRDO Aptitude Paper Sept 2008ML NarasimhamNo ratings yet

- EE 214 Electric Circuits Laboratory: Midterm Examination April 15, 2002Document11 pagesEE 214 Electric Circuits Laboratory: Midterm Examination April 15, 2002Yavuz SahbazNo ratings yet

- Circuit Theory-Ii: Ms. Mariam GulDocument10 pagesCircuit Theory-Ii: Ms. Mariam GulMuhammad ImranNo ratings yet

- Introduction 2Document14 pagesIntroduction 2mwasa28No ratings yet

- Study of Analog Phase-Locked Loop (APLL) : Exercise 9Document10 pagesStudy of Analog Phase-Locked Loop (APLL) : Exercise 9جمال سينغNo ratings yet

- Ministry of Science and Technology Department of Technical and Vocational EducationDocument17 pagesMinistry of Science and Technology Department of Technical and Vocational Educationdeepshikhasharma230191No ratings yet

- PLL TutorialDocument46 pagesPLL Tutorialnucleur_13No ratings yet

- Lab 8: VCO & Frequency Modulation: EE-321: Communication Systems Spring 2017Document8 pagesLab 8: VCO & Frequency Modulation: EE-321: Communication Systems Spring 2017OmerNo ratings yet

- LCA Assignment 1 Spring 2023Document6 pagesLCA Assignment 1 Spring 2023Huzaifa Pervaiz MayoNo ratings yet

- Power Electronics Questions AnswersDocument59 pagesPower Electronics Questions AnswersPascal UZABAKIRIHONo ratings yet

- Linear Verse NonlinearDocument25 pagesLinear Verse NonlinearAnonymous fiIjnBNo ratings yet

- P04 Com para Tors SolDocument8 pagesP04 Com para Tors SolAsza ShahizaNo ratings yet

- Rahman Tutorial 1Document5 pagesRahman Tutorial 1John Wanyoike MakauNo ratings yet

- GATE EE 2010 With SolutionsDocument49 pagesGATE EE 2010 With SolutionsKumar GauravNo ratings yet

- DRDO Question Paper ECE 2008Document12 pagesDRDO Question Paper ECE 2008nagaNo ratings yet

- Switch Mode Power Supply (SMPS) Topologies (Part II)Document108 pagesSwitch Mode Power Supply (SMPS) Topologies (Part II)Willie WalkerNo ratings yet

- RC Circuit - 2019Document3 pagesRC Circuit - 2019thanhtoan2901No ratings yet

- Electronic and Communication 2010::: Firstranker'S ChoiceDocument14 pagesElectronic and Communication 2010::: Firstranker'S ChoiceUtkarsh JainNo ratings yet

- 2-EE-Objective Paper-II-2010 PDFDocument20 pages2-EE-Objective Paper-II-2010 PDFyash97140% (1)

- Elk221 Homework 1 2020-2021Document1 pageElk221 Homework 1 2020-2021here I amNo ratings yet

- HB Conversion MatrixDocument10 pagesHB Conversion MatrixanonNo ratings yet

- EEC110A Win 2010 Final Exam: Name: ID #Document35 pagesEEC110A Win 2010 Final Exam: Name: ID #Zoro ZhaoNo ratings yet

- ps6 - Phase Detector PDFDocument4 pagesps6 - Phase Detector PDFjlissa5262No ratings yet

- MAE307 Applied Electronics (Spring 2015) Mid-Term Exam Class: A B Student ID: Name: Problem 1 (30 PTS)Document3 pagesMAE307 Applied Electronics (Spring 2015) Mid-Term Exam Class: A B Student ID: Name: Problem 1 (30 PTS)limjunbeomNo ratings yet

- Lecture 1 - Filters and Time ResponseDocument13 pagesLecture 1 - Filters and Time ResponseAfonso AlbuquerqueNo ratings yet

- 6002x FinalReview S2012 CleanDocument80 pages6002x FinalReview S2012 CleanGemini GntNo ratings yet

- Alternating Current RC Circuits: 1 ObjectivesDocument9 pagesAlternating Current RC Circuits: 1 ObjectivesgopalgeniusNo ratings yet

- Vco WDocument8 pagesVco Wapi-3725139No ratings yet

- GATE EE 2008 With SolutionsDocument60 pagesGATE EE 2008 With SolutionsAbhishek Mohan67% (3)

- GATE EE 2004 With Solutions PDFDocument57 pagesGATE EE 2004 With Solutions PDFharshdce60No ratings yet

- Basic Definition: Diode Clamping CircuitsDocument6 pagesBasic Definition: Diode Clamping Circuitsالزهور لخدمات الانترنيتNo ratings yet

- RP 2Document7 pagesRP 2Masood AlamNo ratings yet

- ECE 221 - AC Circuit and System Lab: Lab 8: Pulse Amplitude Modulation (PAM) and Pulse Code Modulation (PCM)Document16 pagesECE 221 - AC Circuit and System Lab: Lab 8: Pulse Amplitude Modulation (PAM) and Pulse Code Modulation (PCM)api-595474257No ratings yet

- Irg 4 PC 50 UDocument9 pagesIrg 4 PC 50 Uteam_madNo ratings yet

- Power Electronics Exam II SimulationsDocument10 pagesPower Electronics Exam II SimulationsjoocemachineNo ratings yet

- Review of Power Electronics-Chapter - 6Document17 pagesReview of Power Electronics-Chapter - 6ee mce dataNo ratings yet

- CircuitsII SH1Document4 pagesCircuitsII SH1aymanabuzNo ratings yet

- Angle / Exponential Modulation: Lecture-4 FM Demodulation Using PLLDocument4 pagesAngle / Exponential Modulation: Lecture-4 FM Demodulation Using PLLGopi Chand ChowdaryNo ratings yet

- Analog Electronics Practice QuestionsDocument19 pagesAnalog Electronics Practice Questionssharma_rockstarNo ratings yet

- IRG4PC50S: Features Features Features Features FeaturesDocument8 pagesIRG4PC50S: Features Features Features Features FeaturesPerica RakićNo ratings yet

- Experiment #5 Pulse Response of Simple RC & RL CircuitsDocument11 pagesExperiment #5 Pulse Response of Simple RC & RL CircuitsAhmed HamoudaNo ratings yet

- Chapter - 06Document20 pagesChapter - 06CemalNo ratings yet

- Lab Test 2003-QuizDocument7 pagesLab Test 2003-Quiztoufik bendibNo ratings yet

- Melbourne School of Engineering ELEN30009 Electrical Network Analysis & Design Semester 1, 2017Document34 pagesMelbourne School of Engineering ELEN30009 Electrical Network Analysis & Design Semester 1, 2017RogerNo ratings yet

- Electrical and Electronic Principles 3 Checkbook: The Checkbook SeriesFrom EverandElectrical and Electronic Principles 3 Checkbook: The Checkbook SeriesNo ratings yet

- Fundamentals of Electronics 3: Discrete-time Signals and Systems, and Quantized Level SystemsFrom EverandFundamentals of Electronics 3: Discrete-time Signals and Systems, and Quantized Level SystemsNo ratings yet

- The Spectral Theory of Toeplitz Operators. (AM-99), Volume 99From EverandThe Spectral Theory of Toeplitz Operators. (AM-99), Volume 99No ratings yet

- UntitledDocument1 pageUntitledHelder CruzNo ratings yet

- The ADC Requires 3 Conversion Steps, One Per Output Bit.: F F B - F B - F B - F B - FDocument2 pagesThe ADC Requires 3 Conversion Steps, One Per Output Bit.: F F B - F B - F B - F B - FHelder CruzNo ratings yet

- D E E 2 T E III 5 D 2009 - S 1A - VII 10:00 00-11 30: Epartamento de Ngenharia LectrotécnicaDocument1 pageD E E 2 T E III 5 D 2009 - S 1A - VII 10:00 00-11 30: Epartamento de Ngenharia LectrotécnicaHelder CruzNo ratings yet

- UntitledDocument2 pagesUntitledHelder CruzNo ratings yet

- UntitledDocument1 pageUntitledHelder CruzNo ratings yet

- Problem 1 A) : Given Dout VNQ Z 1 Z Vin 1 DoutDocument5 pagesProblem 1 A) : Given Dout VNQ Z 1 Z Vin 1 DoutHelder CruzNo ratings yet

- Z V D F: Problem 1 A)Document5 pagesZ V D F: Problem 1 A)Helder CruzNo ratings yet

- 1 A) B) C) D)Document2 pages1 A) B) C) D)Helder CruzNo ratings yet

- Problem 1 A)Document5 pagesProblem 1 A)Helder CruzNo ratings yet

- Epartamento de Ngenharia Lectrotécnica º Este de Lectrónica E Unho de Alas E DifícioDocument1 pageEpartamento de Ngenharia Lectrotécnica º Este de Lectrónica E Unho de Alas E DifícioHelder CruzNo ratings yet

- 5 D J 2017 - S 1C E VII 17:00/18:15H - T: Departamento de Engenharia Electrotécnica 1 E E III / R 3 T 17:00/20:00H - EDocument2 pages5 D J 2017 - S 1C E VII 17:00/18:15H - T: Departamento de Engenharia Electrotécnica 1 E E III / R 3 T 17:00/20:00H - EHelder CruzNo ratings yet

- Epartamento de Ngenharia Lectrotécnica º Este de Lectrónica E Unho de ALA Difício ErsionDocument2 pagesEpartamento de Ngenharia Lectrotécnica º Este de Lectrónica E Unho de ALA Difício ErsionHelder CruzNo ratings yet

- 6.02 Nbits +1.76 25,84 DB: SNR V VDocument2 pages6.02 Nbits +1.76 25,84 DB: SNR V VHelder CruzNo ratings yet

- ADC Transfer Function: Vref 1VDocument5 pagesADC Transfer Function: Vref 1VHelder CruzNo ratings yet

- UntitledDocument1 pageUntitledHelder CruzNo ratings yet

- UntitledDocument1 pageUntitledHelder CruzNo ratings yet

- Ko1 10 Ko2 20: ωout vcDocument6 pagesKo1 10 Ko2 20: ωout vcHelder CruzNo ratings yet

- UntitledDocument2 pagesUntitledHelder CruzNo ratings yet

- UntitledDocument1 pageUntitledHelder CruzNo ratings yet

- 14 D J 2011 - S 3.9 E Viii 13:00/16:00H: Departamento de Engenharia Electrotécnica 1º E E IIIDocument2 pages14 D J 2011 - S 3.9 E Viii 13:00/16:00H: Departamento de Engenharia Electrotécnica 1º E E IIIHelder CruzNo ratings yet

- Digital To Analog Converters: Conversores de Sinal - 2022/2023 Nuno Paulino - DEEC-FCT/UNLDocument29 pagesDigital To Analog Converters: Conversores de Sinal - 2022/2023 Nuno Paulino - DEEC-FCT/UNLHelder CruzNo ratings yet

- UntitledDocument2 pagesUntitledHelder CruzNo ratings yet

- UntitledDocument1 pageUntitledHelder CruzNo ratings yet

- ELE 2603 AssignmentDocument16 pagesELE 2603 AssignmentハヤNo ratings yet

- Transistors TutorialDocument3 pagesTransistors Tutorialarness22No ratings yet

- Chap 5 2012Document34 pagesChap 5 2012Tshegofatso KgopaNo ratings yet

- The Transistor Amplifier..Document74 pagesThe Transistor Amplifier..Abian DavilaNo ratings yet

- Low Cost 150 Watt Amplifier CircuitDocument5 pagesLow Cost 150 Watt Amplifier CircuitJyothsna VayyalaNo ratings yet

- Question Bank-16 MarksDocument2 pagesQuestion Bank-16 MarksBala913No ratings yet

- Calculation of Upper and Lower Tripping Point PF Schmitt TrigerDocument6 pagesCalculation of Upper and Lower Tripping Point PF Schmitt TrigerAjay Kumar SinghNo ratings yet

- Electronics Ii: Engr. Ryann AlimuinDocument162 pagesElectronics Ii: Engr. Ryann AlimuinJulius RicardeNo ratings yet

- Unit 2 Differential AmplifierDocument3 pagesUnit 2 Differential AmplifierUmaNo ratings yet

- EE102 Electronic Engineering IIDocument29 pagesEE102 Electronic Engineering II211164 211164No ratings yet

- Ecl Logic FamilyDocument27 pagesEcl Logic Familyalex.waker.proNo ratings yet

- Op-Amp Comparator: Astable (Or Free-Running) Multivibrators Monostable MultivibratorsDocument5 pagesOp-Amp Comparator: Astable (Or Free-Running) Multivibrators Monostable MultivibratorsYuvaraj ShanNo ratings yet

- Operational Amplifier ApplicationsDocument15 pagesOperational Amplifier ApplicationsTanvir Ahmed MunnaNo ratings yet

- Wideband Reject FilterDocument10 pagesWideband Reject FiltermanaswiniNo ratings yet

- ES101Document3 pagesES101Sualé SualéNo ratings yet

- Damian Hall Assignment7 DctheoryDocument18 pagesDamian Hall Assignment7 DctheoryDamian HallNo ratings yet

- Sallen Key FilterDocument9 pagesSallen Key FilterKhaliq ShoaibNo ratings yet

- ECA Lab Manual-Sreedhar2Document119 pagesECA Lab Manual-Sreedhar2Veerendra KumarNo ratings yet

- Plate 2 Unijuction Unilateral Transistor (Marte)Document4 pagesPlate 2 Unijuction Unilateral Transistor (Marte)CloudFarmInnovations IncorporatedNo ratings yet

- GT100FV Adden 060628Document1 pageGT100FV Adden 060628DAN PARASCHIVESCUNo ratings yet

- Tda2003 Stereo Bridged Amplifier: Schematic To PCB Design: in Partial Fulfillment of The Requirements inDocument7 pagesTda2003 Stereo Bridged Amplifier: Schematic To PCB Design: in Partial Fulfillment of The Requirements inSiegrique Ceasar A. JalwinNo ratings yet

- Multistage AmplifiersDocument16 pagesMultistage AmplifiersM. Ahmad RazaNo ratings yet

- Electronic Circuit Design-Ii Lab: Experiment No. 1: Common-Emitter Transistor AmplifierDocument7 pagesElectronic Circuit Design-Ii Lab: Experiment No. 1: Common-Emitter Transistor AmplifierMohsin AliNo ratings yet

- Experiment E1.07 Differential AmplifierDocument16 pagesExperiment E1.07 Differential AmplifierMohd FuadNo ratings yet