Professional Documents

Culture Documents

Untitled

Uploaded by

Helder CruzCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Untitled

Uploaded by

Helder CruzCopyright:

Available Formats

DEPARTAMENTO DE ENGENHARIA

ELECTROTÉCNICA

2º TESTE DE ELECTRÓNICA III

23 DE MAIO DE 2018 – SALA 4.8 ED. VIII

15H30-16H45

VERSION A

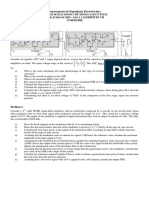

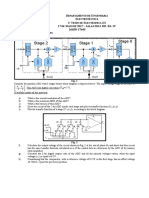

PROBLEM 1: A/D CONVERTERS

Vref /2

-Vref /2

b2.F21 F11 b2.F21 b1.F20 F10 b1.F20

FS 2C C C

vx

vin + 3

SAR Logic dout

-

Fig. 1

Consider the SAR ADC with 3 bits of resolution whose block diagram is depicted above. The input voltage

Vref Vref

range of the ADC is 2 , 2 . (Vref=1 V).

(Carefully justify all the answers)

a) Calculate the value of the lsb voltage of this ADC

b) Draw the ideal transfer function of this ADC

c) What should be the resolution of the ADC, if a SNR value of 30dB is desired for an input signal

with amplitude of 62mV?

d) What is the number of steps required to obtain the correct output code? (do not consider the

sampling step in your answer)

e) Calculate the expression of the charge in the capacitors (vx node) at the end of the sampling

phase (Fs=F11=F10=1) as a function of vin

f) Calculate the expression of the charge in the capacitors (vx node) at the end of the first

conversion step (F21=F10=1) as a function of Vref, vin and b2.

g) Using charge conservation, calculate the expression of vx at the end of the first conversion step,

as a function of Vref, vin and b2

h) Calculate the expression of the charge in the capacitors (vx node) at the end of the second

conversion step (F21=F20=1) as a function of Vref, vin, b1 and b2.

i) Using charge conservation calculate the expression of vx at the end of the second conversion

step, as a function of Vref, vin, b1 and b2

j) Considering that vin=0.2V calculate the values of vx and dout at the end of each of the 3

conversion steps.

k) What is the effect of an offset voltage in the comparator in the transfer function of this ADC,

justify your answer.

DEPARTAMENTO DE ENGENHARIA

ELECTROTÉCNICA

2º TESTE DE ELECTRÓNICA III

23 DE MAIO DE 2018 – SALA 4.8 ED. VIII

15H30-16H45

VERSION B

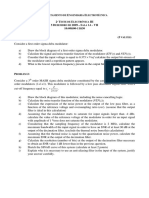

PROBLEM 1: A/D CONVERTERS

Vref /2

-Vref /2

b2.F21 F11 b2.F21 b1.F20 F10 b1.F20

FS 2C C C

vx

vin + 3

SAR Logic dout

-

Fig. 2

Consider the SAR ADC with 3 bits of resolution whose block diagram is depicted above. The input voltage

Vref Vref

range of the ADC is 2 , 2 . (Vref=2 V).

(Carefully justify all the answers)

a) Calculate the value of the lsb voltage of this ADC

b) Draw the ideal transfer function of this ADC

c) What should be the resolution of the ADC, if a SNR value of 24dB is desired for an input signal

with amplitude of 62mV?

d) What is the number of steps required to obtain the correct output code? (do not consider the

sampling step in your answer)

e) Calculate the expression of the charge in the capacitors (vx node) at the end of the sampling

phase (Fs=F11=F10=1) as a function of vin

f) Calculate the expression of the charge in the capacitors (vx node) at the end of the first

conversion step (F21=F10=1) as a function of Vref, vin and b2.

g) Using charge conservation, calculate the expression of vx at the end of the first conversion step,

as a function of Vref, vin and b2

h) Calculate the expression of the charge in the capacitors (vx node) at the end of the second

conversion step (F21=F20=1) as a function of Vref, vin, b1 and b2.

i) Using charge conservation calculate the expression of vx at the end of the second conversion

step, as a function of Vref, vin, b1 and b2

j) Considering that vin=0.2V calculate the values of vx and dout at the end of each of the 3

conversion steps.

k) What is the effect of an offset voltage in the comparator in the transfer function of this ADC,

justify your answer.

You might also like

- UntitledDocument2 pagesUntitledHelder CruzNo ratings yet

- EXPERIMENT #2 Frequency Response of Common Emitter AmplierDocument6 pagesEXPERIMENT #2 Frequency Response of Common Emitter AmplierGhabriel Javier SembranoNo ratings yet

- Lab10 2011Document5 pagesLab10 2011Venkat RamananNo ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet

- 2022-2023-Tri 3-EEE1046-Tutorial 2Document4 pages2022-2023-Tri 3-EEE1046-Tutorial 2j2yshjzzsxNo ratings yet

- Digital To Analog Converter (Dac)Document3 pagesDigital To Analog Converter (Dac)Shimaa BarakatNo ratings yet

- Gateeasy D To A PDFDocument3 pagesGateeasy D To A PDFShubham kumarNo ratings yet

- Review 1 ManuvalDocument25 pagesReview 1 ManuvalvikasNo ratings yet

- 5 D J 2017 - S 1C E VII 17:00/18:15H - T: Departamento de Engenharia Electrotécnica 1 E E III / R 3 T 17:00/20:00H - EDocument2 pages5 D J 2017 - S 1C E VII 17:00/18:15H - T: Departamento de Engenharia Electrotécnica 1 E E III / R 3 T 17:00/20:00H - EHelder CruzNo ratings yet

- Saint Louis UniversityDocument8 pagesSaint Louis Universitynahj.fernandez69No ratings yet

- Multiple Feedback CircuitDocument7 pagesMultiple Feedback CircuitbelmontNo ratings yet

- Electronics Design MOSFETDocument14 pagesElectronics Design MOSFETbhanuNo ratings yet

- Laboratory Experiment 4 Frequency ResponseDocument10 pagesLaboratory Experiment 4 Frequency ResponseFrodolfre Reginald LazoNo ratings yet

- A. DC Operation I. ObjectiveDocument9 pagesA. DC Operation I. ObjectivedummyNo ratings yet

- Eee334 Lab#1 Ltspice and Lab Orientation - Instruments and MeasurementsDocument9 pagesEee334 Lab#1 Ltspice and Lab Orientation - Instruments and Measurementsplaystation0% (1)

- Expt 3: Voltage Shunt Feedback Amplifier (2020)Document4 pagesExpt 3: Voltage Shunt Feedback Amplifier (2020)samarthNo ratings yet

- A. DC Operation I. ObjectiveDocument9 pagesA. DC Operation I. ObjectivedummyNo ratings yet

- Name - Section - : Lab 2 Coupling & Bypass CapacitorsDocument1 pageName - Section - : Lab 2 Coupling & Bypass Capacitorsusman---ali4585No ratings yet

- Frequency Response of A Single Stage RC Coupled AmplifierDocument26 pagesFrequency Response of A Single Stage RC Coupled AmplifierkanchankonwarNo ratings yet

- AD 20flash 20converterDocument7 pagesAD 20flash 20converterChú Cá ConNo ratings yet

- Analog IcDocument3 pagesAnalog IcPraveen kumarNo ratings yet

- Electronics MQP Ii Puc 2023-24Document4 pagesElectronics MQP Ii Puc 2023-24sanjaykashiNo ratings yet

- LC Lab Manual Svuce EceDocument116 pagesLC Lab Manual Svuce EcePMVamsiNo ratings yet

- ECEN650 Lab4Document22 pagesECEN650 Lab4huikwan.yang4386No ratings yet

- Tc320 Lab Manual - 2013Document68 pagesTc320 Lab Manual - 2013Guillermo Castillo MarmolNo ratings yet

- IC and ECAD LabDocument88 pagesIC and ECAD LabVeerayya JavvajiNo ratings yet

- Lab 3Document4 pagesLab 3J SarduaNo ratings yet

- Lab 4 - Differentiator & IntegratorDocument14 pagesLab 4 - Differentiator & IntegratorVickneswaran KalerwananNo ratings yet

- Lab 6 BJT DC and Ac Analysis BBN 10205 (Done)Document6 pagesLab 6 BJT DC and Ac Analysis BBN 10205 (Done)Zhamir ZhakwanNo ratings yet

- 6.334 Power Electronics: Mit OpencoursewareDocument4 pages6.334 Power Electronics: Mit OpencoursewareLocalized Prayer AppNo ratings yet

- University of Edinburgh College of Science and Engineering School of Engineering and ElectronicsDocument15 pagesUniversity of Edinburgh College of Science and Engineering School of Engineering and ElectronicsSyed Fasih Ur RehmanNo ratings yet

- EEE308 Midterm Fall 2023Document3 pagesEEE308 Midterm Fall 2023ANWAR SHADMANNo ratings yet

- Design and Analysis of Multistage Amplifier Configurations: ObjectiveDocument19 pagesDesign and Analysis of Multistage Amplifier Configurations: ObjectivePreet PatelNo ratings yet

- ConvertersDocument54 pagesConvertersyoboiiii649No ratings yet

- Design and Analysis of Multistage Amplifier Configurations: ObjectiveDocument12 pagesDesign and Analysis of Multistage Amplifier Configurations: ObjectivePreet PatelNo ratings yet

- Lab 6Document2 pagesLab 6Someshwar LakavathNo ratings yet

- ECD Lab 2 PDFDocument12 pagesECD Lab 2 PDFMaryam MahmoodNo ratings yet

- EC21101 Basic Electronics ES 2018Document4 pagesEC21101 Basic Electronics ES 2018Santanu KunduNo ratings yet

- TOBB University of Economics and TechnologyDocument4 pagesTOBB University of Economics and TechnologyBugrahan UstundagNo ratings yet

- Exam1 2014 Final SolutionDocument12 pagesExam1 2014 Final SolutionMohd Helmy Hakimie RozlanNo ratings yet

- Activity 3: Rectification 3.1 Program Outcomes (Pos) Addressed by The ActivityDocument34 pagesActivity 3: Rectification 3.1 Program Outcomes (Pos) Addressed by The ActivityDio RinNo ratings yet

- 03 Filter Circuits (FC)Document14 pages03 Filter Circuits (FC)Rawin SirichaisakulNo ratings yet

- Birla Institute of Technology and Science Pilani, Pilani Campus (Raj.)Document3 pagesBirla Institute of Technology and Science Pilani, Pilani Campus (Raj.)Arihant JainNo ratings yet

- Analog Electronic Circuit DesignDocument2 pagesAnalog Electronic Circuit DesignSPANDANNo ratings yet

- A General Approach For Optimizing Dynamic Response For Buck ConverterDocument10 pagesA General Approach For Optimizing Dynamic Response For Buck ConverterDiogo RodriguesNo ratings yet

- Folding ADCs ADIDocument12 pagesFolding ADCs ADINishit Shah100% (1)

- AEC Manuel For AutnomusDocument24 pagesAEC Manuel For Autnomusanon_648461124No ratings yet

- Synthesizer Design: File:///C - /raboch 1/Synth-Rs/Mc/Application Note Vco - HTM (1 of 2) (22.06.2003 21:34:54)Document55 pagesSynthesizer Design: File:///C - /raboch 1/Synth-Rs/Mc/Application Note Vco - HTM (1 of 2) (22.06.2003 21:34:54)Юра РукавишниковNo ratings yet

- Aec Lab ManualDocument61 pagesAec Lab ManualmedeepudeepikaNo ratings yet

- B1 Ece2002 50030 50290 50369Document4 pagesB1 Ece2002 50030 50290 50369NanduNo ratings yet

- Adv Power Electronics - Mid Semsester Examination - 01 - March 2021Document1 pageAdv Power Electronics - Mid Semsester Examination - 01 - March 2021Tushar SanwareyNo ratings yet

- HomeworkDocument4 pagesHomework1dmsrufNo ratings yet

- Exp Week 3 NEWDocument8 pagesExp Week 3 NEWJohn Mark Manalo RosalesNo ratings yet

- Experiment No. 02: RC Coupled Single Stage BJT Common Collector AmplifierDocument5 pagesExperiment No. 02: RC Coupled Single Stage BJT Common Collector AmplifierSajawal AliNo ratings yet

- AEC Lab ManualDocument70 pagesAEC Lab ManualRohan BoseNo ratings yet

- Lab Power AmplifierDocument4 pagesLab Power Amplifiernor asyiqinNo ratings yet

- ECD Lab 2Document5 pagesECD Lab 2hamzaNo ratings yet

- UntitledDocument1 pageUntitledHelder CruzNo ratings yet

- The ADC Requires 3 Conversion Steps, One Per Output Bit.: F F B - F B - F B - F B - FDocument2 pagesThe ADC Requires 3 Conversion Steps, One Per Output Bit.: F F B - F B - F B - F B - FHelder CruzNo ratings yet

- D E E 2 T E III 5 D 2009 - S 1A - VII 10:00 00-11 30: Epartamento de Ngenharia LectrotécnicaDocument1 pageD E E 2 T E III 5 D 2009 - S 1A - VII 10:00 00-11 30: Epartamento de Ngenharia LectrotécnicaHelder CruzNo ratings yet

- UntitledDocument2 pagesUntitledHelder CruzNo ratings yet

- UntitledDocument1 pageUntitledHelder CruzNo ratings yet

- Problem 1 A) : Given Dout VNQ Z 1 Z Vin 1 DoutDocument5 pagesProblem 1 A) : Given Dout VNQ Z 1 Z Vin 1 DoutHelder CruzNo ratings yet

- Z V D F: Problem 1 A)Document5 pagesZ V D F: Problem 1 A)Helder CruzNo ratings yet

- 1 A) B) C) D)Document2 pages1 A) B) C) D)Helder CruzNo ratings yet

- Problem 1 A)Document5 pagesProblem 1 A)Helder CruzNo ratings yet

- Epartamento de Ngenharia Lectrotécnica º Este de Lectrónica E Unho de Alas E DifícioDocument1 pageEpartamento de Ngenharia Lectrotécnica º Este de Lectrónica E Unho de Alas E DifícioHelder CruzNo ratings yet

- 5 D J 2017 - S 1C E VII 17:00/18:15H - T: Departamento de Engenharia Electrotécnica 1 E E III / R 3 T 17:00/20:00H - EDocument2 pages5 D J 2017 - S 1C E VII 17:00/18:15H - T: Departamento de Engenharia Electrotécnica 1 E E III / R 3 T 17:00/20:00H - EHelder CruzNo ratings yet

- Epartamento de Ngenharia Lectrotécnica º Este de Lectrónica E Unho de ALA Difício ErsionDocument2 pagesEpartamento de Ngenharia Lectrotécnica º Este de Lectrónica E Unho de ALA Difício ErsionHelder CruzNo ratings yet

- 6.02 Nbits +1.76 25,84 DB: SNR V VDocument2 pages6.02 Nbits +1.76 25,84 DB: SNR V VHelder CruzNo ratings yet

- ADC Transfer Function: Vref 1VDocument5 pagesADC Transfer Function: Vref 1VHelder CruzNo ratings yet

- I V V V: PD F(S) VCO (T) (T) (T) (T)Document1 pageI V V V: PD F(S) VCO (T) (T) (T) (T)Helder CruzNo ratings yet

- UntitledDocument1 pageUntitledHelder CruzNo ratings yet

- UntitledDocument1 pageUntitledHelder CruzNo ratings yet

- Ko1 10 Ko2 20: ωout vcDocument6 pagesKo1 10 Ko2 20: ωout vcHelder CruzNo ratings yet

- UntitledDocument1 pageUntitledHelder CruzNo ratings yet

- 14 D J 2011 - S 3.9 E Viii 13:00/16:00H: Departamento de Engenharia Electrotécnica 1º E E IIIDocument2 pages14 D J 2011 - S 3.9 E Viii 13:00/16:00H: Departamento de Engenharia Electrotécnica 1º E E IIIHelder CruzNo ratings yet

- Digital To Analog Converters: Conversores de Sinal - 2022/2023 Nuno Paulino - DEEC-FCT/UNLDocument29 pagesDigital To Analog Converters: Conversores de Sinal - 2022/2023 Nuno Paulino - DEEC-FCT/UNLHelder CruzNo ratings yet

- UntitledDocument1 pageUntitledHelder CruzNo ratings yet

- Ship Recognition Manual TOSDocument138 pagesShip Recognition Manual TOSCody Lees94% (17)

- Natal Chart Report PDFDocument17 pagesNatal Chart Report PDFAnastasiaNo ratings yet

- Learning Plans in The Context of The 21 ST CenturyDocument29 pagesLearning Plans in The Context of The 21 ST CenturyHaidee F. PatalinghugNo ratings yet

- Finding Targets PDFDocument9 pagesFinding Targets PDFSteve TangNo ratings yet

- DA-I Question Bank From Module 1-3 of PHY1701 Course, Winter Semester 2020-21Document6 pagesDA-I Question Bank From Module 1-3 of PHY1701 Course, Winter Semester 2020-21Likith MallipeddiNo ratings yet

- Car Parking DesignDocument6 pagesCar Parking Designcharler kinyuajNo ratings yet

- Zgouras Catherine Team Together 1 Teachers BookDocument257 pagesZgouras Catherine Team Together 1 Teachers Booknata86% (7)

- NGCP - Procedures and Requirements For Energy ProjectsDocument17 pagesNGCP - Procedures and Requirements For Energy ProjectspurplebasketNo ratings yet

- Namagunga Primary Boarding School: Primary Six Holiday Work 2021 EnglishDocument10 pagesNamagunga Primary Boarding School: Primary Six Holiday Work 2021 EnglishMonydit santinoNo ratings yet

- Lub OIl Flushing Procedure PDFDocument44 pagesLub OIl Flushing Procedure PDFSubrahmanyam100% (1)

- Matsusada DC-DC ConvertersDocument4 pagesMatsusada DC-DC ConvertersAP SinghNo ratings yet

- Dissertation MA History PeterRyanDocument52 pagesDissertation MA History PeterRyaneNo ratings yet

- Pascal Die Casting Machine SystemDocument20 pagesPascal Die Casting Machine Systemenascimento32No ratings yet

- Credit Card Authorization Form WoffordDocument1 pageCredit Card Authorization Form WoffordRaúl Enmanuel Capellan PeñaNo ratings yet

- College of Engineering Cagayan State UniversityDocument16 pagesCollege of Engineering Cagayan State UniversityErika Antonio GutierrezNo ratings yet

- 4 PDFDocument81 pages4 PDFMohammad K. NassouraNo ratings yet

- Pamphlet 89 Chlorine Scrubbing SystemsDocument36 pagesPamphlet 89 Chlorine Scrubbing Systemshfguavita100% (4)

- Chapter 3 - Methods of Circuit Analysis and Circuit TheoremsDocument125 pagesChapter 3 - Methods of Circuit Analysis and Circuit TheoremsNaim NizamNo ratings yet

- I.A.-1 Question Bank EM-3 (Answers)Document11 pagesI.A.-1 Question Bank EM-3 (Answers)UmmNo ratings yet

- HP Scanjet N9120 (Service Manual) PDFDocument394 pagesHP Scanjet N9120 (Service Manual) PDFcamilohto80% (5)

- ISO-50001-JK-WhiteDocument24 pagesISO-50001-JK-WhiteAgustinusDwiSusantoNo ratings yet

- SemDocument583 pagesSemMaria SantosNo ratings yet

- A Presentation On-: E-Paper TechnologyDocument19 pagesA Presentation On-: E-Paper TechnologyRevanth Kumar TalluruNo ratings yet

- Afa Coursework ExamplesDocument6 pagesAfa Coursework Examplesiuhvgsvcf100% (2)

- Module 1 Supply Chain Management in Hospitality IndustryDocument39 pagesModule 1 Supply Chain Management in Hospitality IndustryHazelyn BiagNo ratings yet

- Probability Theory - VaradhanDocument6 pagesProbability Theory - VaradhanTom HenNo ratings yet

- n4 HandoutDocument2 pagesn4 HandoutFizzerNo ratings yet

- Modular Heavy Duty Truck TransmissionDocument6 pagesModular Heavy Duty Truck Transmissionphucdc095041No ratings yet

- SQL and Hand BookDocument4 pagesSQL and Hand BookNaveen VuppalaNo ratings yet

- Practice Test - Math As A Language - MATHEMATICS IN THE MODERN WORLDDocument8 pagesPractice Test - Math As A Language - MATHEMATICS IN THE MODERN WORLDMarc Stanley YaoNo ratings yet