Professional Documents

Culture Documents

ASIC Design Flow

Uploaded by

srinathCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

ASIC Design Flow

Uploaded by

srinathCopyright:

Available Formats

VLSI DESIGN SHORT PAPER ARTICLE

Student Name Vattipelli Srinath

ID No. 2023H1400116H

Subject VLSI Design

Topic ASIC Design Flow

Theory and Background:

1. Introduction:

ASIC design's dynamic history, evolving from the 1960s, saw transformative

phases with VLSI in the 1980s and EDA tools in the 1990s. Pivotal moments, like the

shift to SoC architectures in the early 2000s, marked a sophistication turning point.

Today, ASIC design integrates AI, machine learning, and advanced processes. This

report explores ASIC design flow, highlighting historical milestones and current trends

shaping custom silicon. It delves into methodology intricacies, offering insights into

challenges and innovations defining its evolution, providing a foundation for future

intricacies.

2. What is an ASIC?

An ASIC is a custom-designed integrated circuit tailored for a specific

application, offering benefits like enhanced performance, reduced power consumption,

and smaller size compared to general-purpose ICs.ASICs are created to meet the unique

requirements of a specific application, providing advantages such as:

• High performance and power efficiency

• Compact size

• Cost-Effectiveness when produced in large production volumes

ASICs are commonly used in a variety of applications, including

telecommunications, consumer electronics, automotive systems, and more. They are

often employed in scenarios where performance, efficiency, and customization are

critical factors. The design process for ASICs is complex and involves creating a custom

chip layout optimized for the intended function. This design process is known as ASIC

design flow.

3. ASIC Design Flow:

The ASIC design flow is a comprehensive process that begins with capturing the

customer's requirements and culminates in the fabrication of a custom-designed

Application-Specific Integrated Circuit (ASIC).

In general, the ASIC design happens at the following stages.

1. RTL Design.

2. Logic Synthesis.

3. Physical Design.

3.1. RTL Design:

3.1.1. Requirements Definition: This initial step involves a thorough definition

of the specific functional requirements of the ASIC. This includes a detailed

specification of inputs, outputs, and the expected data processing capabilities.

3.1.2. Architecture Design: The overall architecture of the ASIC is conceived,

involving the creation of a high-level block diagram. This stage defines essential

aspects such as communication protocols and control mechanisms, setting the

blueprint for the chip's structure.

3.1.3. RTL Design: Register-Transfer Level (RTL) design involves specifying

the detailed behaviour of the ASIC using hardware description languages

(HDLs). Verilog or VHDL is employed to articulate the logic and data flow

within the chip, ensuring a comprehensive representation of its functionality.

3.1.4. Functional Verification: Rigorous testing and simulation techniques are

applied to verify the correctness of the RTL design. This step ensures that the

ASIC meets the specified functional requirements and operates as intended,

addressing potential issues before moving to the next stage.

3.2. Logic Synthesis:

3.2.1. Synthesis: The RTL code undergoes translation into a gate-level netlist.

This netlist serves as a detailed representation of the logic gates and their

interconnections, optimized for performance and area efficiency.

3.2.2. Equivalence Checking: To preserve the design intent, the equivalence

checking needs to be performed to check the logic equivalence. The equivalence

checking uses the formal verification techniques. The objective of the

equivalence checking is to verify the RTL design functionality.

3.2.3. DFT: Design for testability (DFT) is a technique which facilitates a design

to become testable after production. In this stage we put extra logic along with

the design logic during implementation process which helps post production

process. DFT will make the testing easy at post production process. At this stage

an ATPG (automatic test pattern generator) file will be generated.

3.3 Physical Design:

3.3.1. Floorplanning: The physical layout of the chip is meticulously planned

during this step. This process considers factors like block placement, power

distribution, and signal routing, determining the overall dimensions and resource

utilization of the chip.

3.3.2. Placement and Routing: Individual logic gates are physically placed on

the chip, and interconnecting wires are routed to establish connections. This step

optimizes the chip layout for timing and signal integrity, contributing to the

efficient physical implementation of the ASIC.

3.3.3. Physical Verification: The physical layout undergoes thorough scrutiny

for design rule checks (DRC) and layout versus schematic (LVS) verification.

This ensures that the physical implementation aligns with the design intent and

adheres to industry standards, maintaining the integrity of the ASIC.

3.3.4. Timing Analysis: Timing behaviour is analysed to ensure signals

propagate within specified clock cycles. This stage focuses on optimizing the

design for performance and meeting critical timing constraints.

3.3.5. Signoff: The final physical layout undergoes comprehensive review,

ensuring that all technical requirements are met. This step marks approval for the

fabrication process.

3.3.6. GDSII Generation: The final layout is exported in GDSII format, a

standardized file format essential for IC manufacturing. This file contains precise

descriptions of the chip's physical elements and their interconnections.

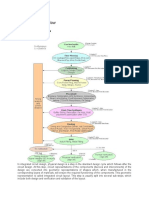

Flowchart:

a) RTL Design b) Logic Synthesis c) Physical Design

Applications of ASIC Design Flow:

1. Consumer Electronics: ASICs are extensively used in consumer electronics for

applications like custom processors, graphics processors, and specialized control

circuits.

2. Communications: In the telecommunications industry, ASICs play a crucial role

in the development of custom communication processors, networking

components, and signal processing units.

3. Automotive: ASIC design is integral to the automotive industry for creating

specialized chips used in engine control units, safety systems, infotainment, and

advanced driver assistance systems (ADAS).

4. Medical Electronics: ASICs are employed in medical devices for functions like

signal processing in imaging equipment, patient monitoring systems, and custom

integrated circuits for specific medical applications.

5. Aerospace and Defense: ASICs are utilized in aerospace and defense

applications for creating custom chips tailored to meet the specific requirements

of avionics, radar systems, communication systems, and navigation equipment.

6. Industrial Automation: In industrial settings, ASICs are used for control

systems, sensor interfaces, and other specialized functions to enhance automation

and efficiency.

7. Data Storage: ASICs are employed in data storage applications, such as custom

controllers for solid-state drives (SSDs), ensuring efficient storage.

8. IoT (Internet of Things): In the IoT ecosystem, ASICs are used to create

power-efficient and specialized chips for various connected devices, enabling

seamless communication and functionality.

Current Trends and Research on ASICs and its design flow:

1. Advanced Semiconductor Process Nodes: Ongoing research explores 3nm

and 5nm process nodes for enhanced chip miniaturization, boosting performance

and energy efficiency.

2. Compact and Power-Efficient Design: Emphasis on smaller, low-power

ASICs driven by innovations like FinFET and 3D stacking, meeting demands in

IoT and wearables.

3. Heterogeneous Computing: Integration of CPUs, GPUs, and DSPs on a single

chip for diverse task execution, aligning with AI and machine learning

requirements.

4. AI/ML Integration: AI algorithms optimize ASIC design tasks, from layout

design to performance prediction, improving efficiency and development speed.

5. Security and Privacy Integration: Specialized security ASICs with hardware-

level features (encryption, secure boot) respond to the increasing demand for data

protection.

6. Energy Efficiency and Sustainability: Focus on ASICs operating on

renewable sources (e.g., solar power) aligns with global sustainability goals.

7. Edge Computing: Tailored ASICs for distributed computing in edge

environments, facilitating real-time data processing closer to the data source.

References:

1. Smith, John. "ASIC Design: A Comprehensive Guide." Journal of

Electronics Engineering, vol. 25

2. Taraate, Vaibbhav. ASIC Design and Synthesis: RTL Design Using

Verilog. 2021.

3. Massimo Bombana, “Design Flow and Synthesis for ASICs: a case study”,

Design Automation Conference, IEEE, 1995.

4. Shetty, A. A. (2019). "ASIC Design Flow And Methodology – An

Overview," SSRG International Journal of Electrical and Electronics

Engineering (SSRG - IJEEE), Volume 6, Issue 7, July 2019.

5. V. Sahula, C. P. Ravikumar and Nagchoudhuri, Improvement of ASIC

Design Processes, Proceedings of 15th International IEEE conference on

VLSI design 2002

You might also like

- 3512 Throttle Position Error 91-8Document13 pages3512 Throttle Position Error 91-8harikrishnanpd3327100% (3)

- Dyna DM2800 SchematicsDocument4 pagesDyna DM2800 SchematicsRamon Hernandez100% (1)

- PROGRAMMING GUIDE 5-Tone Signaling IcomDocument25 pagesPROGRAMMING GUIDE 5-Tone Signaling IcomCiber Kraken100% (2)

- Transmission Lines: Steady-State OperationDocument30 pagesTransmission Lines: Steady-State OperationJihad HossainNo ratings yet

- IBM ASIC-SoC MethodologyDocument12 pagesIBM ASIC-SoC Methodologyghatakp2069No ratings yet

- Asic Design FlowDocument25 pagesAsic Design FlowKarishma PotnuruNo ratings yet

- Tanner ManualDocument60 pagesTanner ManualFahim Ahmed100% (1)

- VLSI Design Lab NewDocument48 pagesVLSI Design Lab NewJubin JainNo ratings yet

- VLSI Design Lab NewDocument45 pagesVLSI Design Lab NewmtariqanwarNo ratings yet

- Application - Specific.IC DesignFlowDocument8 pagesApplication - Specific.IC DesignFlowNandagopal SivakumarNo ratings yet

- ASIC Design Flow and Methodology - An OverviewDocument6 pagesASIC Design Flow and Methodology - An OverviewAhtasham KhokherNo ratings yet

- Chapter 5: Asics vs. PldsDocument13 pagesChapter 5: Asics vs. PldsLaxmanaa GajendiranNo ratings yet

- The Ibm Asic/Soc Methodology - A Recipe For First-Time SuccessDocument12 pagesThe Ibm Asic/Soc Methodology - A Recipe For First-Time Successjagmohan.nanawareNo ratings yet

- Design of Efficient AMBA AHB ArbiterDocument9 pagesDesign of Efficient AMBA AHB ArbiterVennapoosa Hemanth Kumar ReddyNo ratings yet

- UntitledDocument4 pagesUntitled291SWAYAM BEHERANo ratings yet

- Application Specific Integrated Circuits (ASICs) Design ProcessDocument26 pagesApplication Specific Integrated Circuits (ASICs) Design ProcessRamesh LakshmananNo ratings yet

- Vlsiphysicaldesign 150621074440 Lva1 App6891Document16 pagesVlsiphysicaldesign 150621074440 Lva1 App6891Æshok IncreĐible KingNo ratings yet

- VLSI Design Flow: The 8 Step Process for Creating Integrated CircuitsDocument3 pagesVLSI Design Flow: The 8 Step Process for Creating Integrated CircuitsSaurabh PorwalNo ratings yet

- ASICs KumarDocument47 pagesASICs Kumarmolugu kumaraswamyNo ratings yet

- Wipro System On ChipDocument11 pagesWipro System On Chipprodip7No ratings yet

- Introduction To ASIC TechnologyDocument6 pagesIntroduction To ASIC Technologyrpa projectNo ratings yet

- VLSI Design: An Introduction to IC TechnologyDocument59 pagesVLSI Design: An Introduction to IC TechnologyDr. Pullareddy AvulaNo ratings yet

- DSD LABDocument45 pagesDSD LABkumarravi955rNo ratings yet

- What Is An FPGA?: Figure 1: FPGA Block StructureDocument10 pagesWhat Is An FPGA?: Figure 1: FPGA Block Structureacer551100% (1)

- Physical DesignDocument12 pagesPhysical DesignPallavi ChNo ratings yet

- Vlsi Design FlowDocument7 pagesVlsi Design FlowAster RevNo ratings yet

- VLSI Physical Design andDocument23 pagesVLSI Physical Design andRajesh BathijaNo ratings yet

- Xilinx Glossary TermsDocument3 pagesXilinx Glossary TermsHarshithaNo ratings yet

- Issues and Strategies For The Physical Design of System-On-A-Chip AsicsDocument14 pagesIssues and Strategies For The Physical Design of System-On-A-Chip Asicskryptonites1234No ratings yet

- SocDocument49 pagesSocVarun ChauhanNo ratings yet

- VHDL NotesDocument40 pagesVHDL Notesangel_hunNo ratings yet

- Asic Bist Approach: Synthesis: A VHDLDocument10 pagesAsic Bist Approach: Synthesis: A VHDLgurudevmaneNo ratings yet

- PD FlowDocument6 pagesPD FlowUTtNo ratings yet

- Electronic Design AutomationDocument7 pagesElectronic Design Automationmia farrowNo ratings yet

- Automated Solution For Data Monitoring (Dashboard) of ASIC Design FlowDocument4 pagesAutomated Solution For Data Monitoring (Dashboard) of ASIC Design FlowseventhsensegroupNo ratings yet

- TKT-9627 Digital and Computer Systems Seminar: Closing The Gap Between ASIC & CustomDocument28 pagesTKT-9627 Digital and Computer Systems Seminar: Closing The Gap Between ASIC & CustomRoshan RajuNo ratings yet

- Application-Specific Integrated Circuit (ASIC) : Where Is It Found?Document2 pagesApplication-Specific Integrated Circuit (ASIC) : Where Is It Found?Hammad Ul HaqueNo ratings yet

- LECTURE 5: IEC61850 Standard For SCADADocument3 pagesLECTURE 5: IEC61850 Standard For SCADAYogesh BadheNo ratings yet

- International Journal of Engineering Research & Technology (IJERT) - Rambist Implementation From Avr For Regular Structured Embedded Cores In System-On-ChipDocument7 pagesInternational Journal of Engineering Research & Technology (IJERT) - Rambist Implementation From Avr For Regular Structured Embedded Cores In System-On-ChipDinesh KiranNo ratings yet

- Very Large Scale Integration (Vlsi)Document49 pagesVery Large Scale Integration (Vlsi)sayyioNo ratings yet

- Implementation of Serial Communication IP For Soc ApplicationsDocument4 pagesImplementation of Serial Communication IP For Soc ApplicationsInternational Journal of computational Engineering research (IJCER)No ratings yet

- Ice 311 AssignmentDocument6 pagesIce 311 AssignmentudayNo ratings yet

- Testability Expert System: SteedDocument1 pageTestability Expert System: SteedBijoy Kumar UpadhyayaNo ratings yet

- Deming Chen: Chapter 38, Design Automation For Microelectronics, Springer Handbook of AutomationDocument15 pagesDeming Chen: Chapter 38, Design Automation For Microelectronics, Springer Handbook of AutomationanilariNo ratings yet

- Digital Integrated Circuit (Ic) DesignDocument16 pagesDigital Integrated Circuit (Ic) DesignHoàng Đức KhảiNo ratings yet

- Anmol 2 NumbriDocument46 pagesAnmol 2 NumbriROUGH X YTNo ratings yet

- Physical Design Implementation of 32bit RISC Processor Using Synopsys ICC Primetime & StarRC XTDocument6 pagesPhysical Design Implementation of 32bit RISC Processor Using Synopsys ICC Primetime & StarRC XTFeroz AhmedNo ratings yet

- Designing of Telecommand System Using System On Chip Soc For Spacecraft Control ApplicationsDocument11 pagesDesigning of Telecommand System Using System On Chip Soc For Spacecraft Control ApplicationsIAEME PublicationNo ratings yet

- EEE 4232Document135 pagesEEE 4232MD. ASHIQUR RAHMAN 1602111No ratings yet

- System On Chip Design and ModellingDocument131 pagesSystem On Chip Design and ModellingGurram KishoreNo ratings yet

- VLSI SoC Design Using VerilogDocument47 pagesVLSI SoC Design Using VerilogROUGH X YTNo ratings yet

- A Digital Design Flow For Secure Integrated CircuitsDocument12 pagesA Digital Design Flow For Secure Integrated CircuitsMOHAMMAD AWAISNo ratings yet

- Physical Design FlowDocument42 pagesPhysical Design Flowelumalaianitha100% (1)

- System On ChipDocument11 pagesSystem On ChipAnonymous 4fXluvNo ratings yet

- Asic Design Flow:: Specification FloorplanDocument9 pagesAsic Design Flow:: Specification Floorplanp gangadhar KumarNo ratings yet

- VLSI Design Quick GuideDocument68 pagesVLSI Design Quick GuideMayur AgarwalNo ratings yet

- Literature review on ASIC implementation of superscalar RISC-V microprocessorDocument4 pagesLiterature review on ASIC implementation of superscalar RISC-V microprocessorATHIRA V RNo ratings yet

- Vlsi Cmos Interview Q&A Part-3Document7 pagesVlsi Cmos Interview Q&A Part-3harshaNo ratings yet

- Data Converter BIST Development Tools: Ian Grout, Thomas O'Shea and Jeffrey RyanDocument2 pagesData Converter BIST Development Tools: Ian Grout, Thomas O'Shea and Jeffrey Ryansarin.gaganNo ratings yet

- Whitepaper Substation Automation Schneider ElectricDocument5 pagesWhitepaper Substation Automation Schneider Electricsahil4INDNo ratings yet

- Vlsi Soc Design Using Verilog HDL: Training Report ONDocument46 pagesVlsi Soc Design Using Verilog HDL: Training Report ONROUGH X YTNo ratings yet

- Digital Electronics, Computer Architecture and Microprocessor Design PrinciplesFrom EverandDigital Electronics, Computer Architecture and Microprocessor Design PrinciplesNo ratings yet

- TERBARU Materi Ajar BARU ImelDocument28 pagesTERBARU Materi Ajar BARU ImelYukee LoeNo ratings yet

- DSFDocument3 pagesDSFJose Maria SantosNo ratings yet

- System Administration and Maintenance FQ1 FINAL MP2 PDFDocument3 pagesSystem Administration and Maintenance FQ1 FINAL MP2 PDFLollz AutidaNo ratings yet

- Vide O Surv Eill AnceDocument5 pagesVide O Surv Eill AncemartinosamigosNo ratings yet

- IEEE GLOBECOM 2016 Technical Program PDFDocument75 pagesIEEE GLOBECOM 2016 Technical Program PDFsolarisan6No ratings yet

- Y6630D Installation GuideDocument10 pagesY6630D Installation GuidemurtazasabirNo ratings yet

- Thermal Design and Analysis of An Air Cooled X-Band Active Phased Array Antenna-IRSI 17-004Document5 pagesThermal Design and Analysis of An Air Cooled X-Band Active Phased Array Antenna-IRSI 17-004Swadish KashyupNo ratings yet

- MNP Call Flow Routing and GSM HandoverDocument14 pagesMNP Call Flow Routing and GSM HandoverNitesh KumarNo ratings yet

- VSWR & Power Measurement Process On Anritsu Site MasterDocument4 pagesVSWR & Power Measurement Process On Anritsu Site MasterArvindNo ratings yet

- Ft2Dr/De: Main/Sub Firmware Update Instruction ManualDocument22 pagesFt2Dr/De: Main/Sub Firmware Update Instruction Manualprofesor Andres Felipe Gonzalez CoronadoNo ratings yet

- High-Power IGBT Modules For Industrial UseDocument5 pagesHigh-Power IGBT Modules For Industrial UseOmar AlhakimiNo ratings yet

- Physical Science Activity Sheet Quarter 2 - MELC 12 Week 5: Radio PulsesDocument6 pagesPhysical Science Activity Sheet Quarter 2 - MELC 12 Week 5: Radio PulsesTonet Competente100% (1)

- UntitledDocument9 pagesUntitledعسم ساماNo ratings yet

- Ma Nu Ale Microbe Tam 02 EngDocument39 pagesMa Nu Ale Microbe Tam 02 EngNevenko Arlov100% (3)

- FCT 8051 Development Board with 17 ModulesDocument2 pagesFCT 8051 Development Board with 17 ModulesDeepak KumbharNo ratings yet

- Philips 37 42 47mf437b 37 42 47pfl5432d 37 Chassis tpm2 0u La SM ET 1Document125 pagesPhilips 37 42 47mf437b 37 42 47pfl5432d 37 Chassis tpm2 0u La SM ET 1Randy EnersonNo ratings yet

- The Pentium 4 ArchitectureDocument5 pagesThe Pentium 4 ArchitectureDaniloMoceriNo ratings yet

- 1.5 A, Step-Up/Down/ Inverting Switching Regulators NCP3063, NCP3063B, NCV3063Document21 pages1.5 A, Step-Up/Down/ Inverting Switching Regulators NCP3063, NCP3063B, NCV3063cristianNo ratings yet

- 1159-2019 - IEEE Recommended Practice For Monitoring Electric Power QualityDocument15 pages1159-2019 - IEEE Recommended Practice For Monitoring Electric Power QualityEko SutjiptoNo ratings yet

- Switching Theory and Logic Design Lab (ETEC - 253)Document82 pagesSwitching Theory and Logic Design Lab (ETEC - 253)AmanNo ratings yet

- VLSI Testing & TestabilityDocument1 pageVLSI Testing & TestabilityDr. Lokesh Kumar BramhaneNo ratings yet

- Dxdiag LumionDocument43 pagesDxdiag LumionMANUEL ALEJANDRO CELEITA GONZALEZNo ratings yet

- Replacing Laptop Motherboard Super IO Chip ITE8987 - Page 2Document12 pagesReplacing Laptop Motherboard Super IO Chip ITE8987 - Page 2Marko MatićNo ratings yet

- Description Des Facilités ANG PDFDocument2,086 pagesDescription Des Facilités ANG PDFsalvadorNo ratings yet

- SSD Buying Guide - List July 21, 2020Document19 pagesSSD Buying Guide - List July 21, 2020MJ ServaNo ratings yet

- A Seminar Report On "Fluorescent Multilayer Disc": Prepared By: Shah Nilay K. 6 E.CDocument16 pagesA Seminar Report On "Fluorescent Multilayer Disc": Prepared By: Shah Nilay K. 6 E.CturakhiakrupaliNo ratings yet