Professional Documents

Culture Documents

Drmos BLN01G52 Aoz5311 RTX3070

Uploaded by

techgamebr85Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Drmos BLN01G52 Aoz5311 RTX3070

Uploaded by

techgamebr85Copyright:

Available Formats

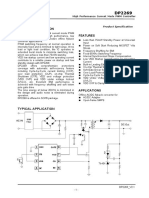

AOZ5311NQI

High-Current, High-Performance

DrMOS Power Module

General Description Features

The AOZ5311NQI is a high efficiency synchronous buck 2.5V to 20V power supply range

power stage module consisting of two asymmetrical 4.5V to 5.5V driver supply range

MOSFETs and an integrated driver. The MOSFETs are

50A continuous output current

individually optimized for operation in the synchronous

buck configuration. The High-Side MOSFET is optimized - Up to 80A for 10ms on pulse

to achieve low capacitance and gate charge for fast - Up to 120A for 10us on pulse

switching with low duty cycle operation. The Low-Side Up to 2MHz switching operation

MOSFET has ultra low ON resistance to minimize 3V / 5V PWM / Tri-State input compatible

conduction loss.

Under-Voltage lockout protection

The AOZ5311NQI uses a PWM input for accurate control SMOD# control for Diode Emulation / CCM operation

of the power MOSFETs switching activities, is compatible Low Profile 5x5 QFN-31L package

with 3V and 5V (CMOS) logic and supports Tri-State

PWM. Applications

A number of features are provided making the Memory and graphic cards

AOZ5311NQI a highly versatile power module. The boot- VRMs for motherboards

strap switch is integrated in the driver. The Low-Side

Point of load DC/DC converters

MOSFET can be driven into diode emulation mode to

provide asynchronous operation and improve light-load Video gaming console

performance. The pin-out is also optimized for low

parasitics, keeping their effects to a minimum.

Typical Application Circuit

2.5V ~ 20V

VIN

VCC BOOT

HS CBOOT CIN

THWN Driver

Driver PHASE

PWM Logic

DISB# L1 VOUT

Controller and VSWH

Delay

SMOD#

LS

Driver COUT

PWM

GL

AGND

VCC PVCC PGND

CVCC

5V CPVCC PGND

Rev. 1.0 May 2019 www.aosmd.com Page 1 of 17

Downloaded from: http://www.datasheetcatalog.com/

AOZ5311NQI

Ordering Information

Part Number Ambient Temperature Range Package Environmental

AOZ5311NQI -40°C to 125°C QFN5x5-31L RoHS

AOS Green Products use reduced levels of Halogens, and are also RoHS compliant.

Please visit www.aosmd.com/media/AOSGreenPolicy.pdf for additional information.

Pin Configuration

VSWH

VSWH

THWN

VSWH

DISB#

PGND

PVCC

GL

31 30 29 28 27 26 25 24

PWM 1 GL 23 VSWH

SMOD# 2 22 VSWH

PGND

VCC 3 21 VSWH

AGND 4 20 VSWH

BOOT 5 19 VSWH

NC 6 PGND 18 VSWH

PHASE 7 VIN 17 VSWH

VIN 8 16 VSWH

9 10 11 12 13 14 15

VIN

VIN

PGND

VIN

PGND

PGND

PGND

QFN5x5-31L

(Top View)

Rev. 1.0 May 2019 www.aosmd.com Page 2 of 17

Downloaded from: http://www.datasheetcatalog.com/

AOZ5311NQI

Pin Description

Pin Number Pin Name Pin Function

PWM input signal from the controller IC. When DISB#=0V, the internal resistor divider will be

1 PWM

disconnected and this pin will be at high impedance.

Pull low to enable Discontinuous Mode of Operation (DCM), Diode Emulation or Skip Mode.

2 SMOD#

There is an internal pull-down resistor to AGND.

5V Bias for Internal Logic Blocks. Ensure to position a 1µF MLCC directly between VCC and

3 VCC

AGND (Pin 4).

4 AGND Signal Ground.

High-Side MOSFET Gate Driver supply rail. Connect a 100nF ceramic capacitor between

5 BOOT

BOOT and the PHASE (Pin 7).

6 NC Internally connected to VIN paddle. It can be left floating (no connect) or tied to VIN.

7 PHASE This pin is dedicated for bootstrap capacitor AC return path connection from BOOT (Pin 5).

8, 9, 10, 11 VIN Power stage High Voltage Input (Drain connection of High-Side MOSFET).

12, 13, 14, 15 PGND Power Ground pin for power stage (Source connection of Low-Side MOSFET).

16,17,18,19, Switching node connected to the Source of High-Side MOSFET and the Drain of Low-Side

20,21,22, 23, VSWH MOSFET. These pins are used for Zero Cross Detection and Anti-Overlap Control as well as

24, 25, 26 main inductor terminal.

27 GL Low-Side MOSFET Gate connection. This is for test purposes only.

Power Ground pin for High-Side and Low-Side MOSFET Gate Drivers. Ensure to connect 1µF

28 PGND

directly between PGND and PVCC (Pin 29).

5V power rail for High-Side and Low-Side MOSFET gate drivers. Ensure to position a 1µF

29 PVCC

MLCC directly between PVCC to PGND (Pin 28).

Thermal warning indicator. This is an open−drain output. When the temperature at the driver

30 THWN

IC die reaches the Over Temperature Threshold, this pin is pulled low.

Output disable pin. When this pin is pulled to a logic low level, the IC is disabled. There is an

31 DISB#

internal pull−down resistor to AGND.

Rev. 1.0 May 2019 www.aosmd.com Page 3 of 17

Downloaded from: http://www.datasheetcatalog.com/

AOZ5311NQI

Functional Block Diagram

VCC PVCC BOOT VIN

SMOD# ZCD Select REF/BIAS

UVLO

HS

Level Shifter Gate

Driver

Boot HS

PHASE

Sequencing HS

Gate

And PHASE Check VSWH

Propagation Driver Logic

DISB# Enable

Delay Control

LS Control Logic

ZCD

VCC

ZCD Detect

PWM

LS Gate

Tri-State PVCC

PWM

PWM Tri-State LS

Logic Gate

Driver GL

Thermal

Monitor PGND

THWN AGND

Rev. 1.0 May 2019 www.aosmd.com Page 4 of 17

Downloaded from: http://www.datasheetcatalog.com/

AOZ5311NQI

Absolute Maximum Ratings Recommended Operating Conditions

Exceeding the Absolute Maximum ratings may damage the The device is not guaranteed to operate beyond the Maximum

device. Recommended Operating Conditions.

Parameter Rating Parameter Rating

Low Voltage Supply (VCC, PVCC) -0.3V to 7V High Voltage Supply (VIN) 2.5V to 20V

High Voltage Supply (VIN) -0.3V to 25V Low Voltage/ MOSFET Driver 4.5V to 5.5V

Supply (VCC, PVCC)

Control Inputs -0.3V to (VCC+0.3V)

(PWM, SMOD#, DISB#) Control Inputs 0V to VCC

(PWM, SMOD#, DISB#)

Output (THWN) -0.3V to (VCC+0.3V)

Output (THWN) 0V to VCC

Bootstrap Voltage DC -0.3V to 28V

(BOOT-PGND) Operating Frequency 200kHz to 2MHz

(1)

Bootstrap Voltage Transient -8V to 30V

(BOOT-PGND)

Bootstrap Voltage DC -0.3V to 7V

(BOOT-PHASE/VSWH)

BOOT Voltage Transient(1) -0.3V to 9V

(BOOT-PHASE/VSWH)

Switch Node Voltage DC -0.3V to 25V

(PHASE/VSWH)

Switch Node Voltage Transient(1) -8V to 33V

(PHASE/VSWH)

Low-Side Gate Voltage DC (GL) (PGND-0.3V) to

(PVCC+0.3V)

Low-Side Gate Voltage (PGND-2.5V) to

Transient(2) (GL) (PVCC+0.3V)

VSWH Current DC 50A

VSWH Current 10ms Pulse 80A

VSWH Current 10us Pulse 120A

Storage Temperature (TS) -65°C to +150°C

Max Junction Temperature (TJ) 150°C

(3)

ESD Rating 2kV

Notes:

1. Peak voltages can be applied for 10ns per switching cycle.

2. Peak voltages can be applied for 20ns per switching cycle.

3. Devices are inherently ESD sensitive, handling precautions are

required. Human body model rating: 1.5k in series with 100pF.

Rev. 1.0 May 2019 www.aosmd.com Page 5 of 17

Downloaded from: http://www.datasheetcatalog.com/

AOZ5311NQI

Electrical Characteristics(4)

TA = 25°C to 125°C. Typical values reflect 25°C ambient temperature; VIN = 12V, VCC= PVCC= DISB# = 5V, unless otherwise

specified.

Symbol Parameter Conditions Min. Typ. Max. Units

GENERAL

VIN Power Stage Power Supply 2.5 20 V

VCC Low Voltage Bias Supply PVCC = VCC 4.5 5.5 V

RJC(5) Reference to High-Side MOSFET 2.5 °C/W

Thermal Resistance temperature rise

RJA(5) Freq = 300kHz. AOS Demo Board 12.5 °C/W

INPUT SUPPLY AND UVLO

VCC_UVLO VCC Rising 3.5 3.9 V

Under-Voltage Lockout

VCC_HYST VCC Hysteresis 400 mV

DISB# = 0V 1 A

SMOD# = 5V, PWM = 0V 550 A

IVCC Control Circuit Bias Current

SMOD# = 0V, PWM = 0V 535 A

SMOD# = 0V, PWM =1.65V 430 A

PWM = 400kHz, 20% Duty Cycle 13 mA

IPVCC Drive Circuit Operating Current

PWM = 1MHz, 20% Duty Cycle 33 mA

PWM INPUT

VPWMH Logic High Input Voltage 2.7 V

VPWML Logic Low Input Voltage 0.72 V

IPWM_SRC PWM = 0V -150 A

PWM Pin Input Current

IPWM_SNK PWM = 3.3V 150 A

VTRI PWM Input Tri-State Window 1.35 1.95 V

VPMW_

PWM Tri-State Voltage Clamp PWM = Floating 1.65 V

FLOAT

DISB# INPUT

VDISB#_

Enable Input Voltage 2.0 V

ON

VDISB#_

Disable Input Voltage 0.8 V

OFF

RDISB# DISB# Input Resistance Pull-Down Resistor 850 k

SMOD# INPUT

VSMOD#_H Logic High Input Voltage 2.0 V

VSMOD#_L Logic Low Input Voltage 0.8 V

RSMOD# SMOD# Input Resistance Pull-Down Resistor 850 k

GATE DRIVER TIMING

tPDLU PWM to High-Side Gate PWM: H→L, VSWH: H→L 30 ns

tPDLL PWM to Low-Side Gate PWM: L H, GL: H L 25 ns

(6)

tPDHU Low-side to High-Side Gate Deadtime GL: H L, GH : L H 15 ns

tPDHL High-Side to Low-side Gate Deadtime VSWH: H 1V, GL: L H 13 ns

PWM: L VTRI, GL: H L and

tTSSHD Tri-State Shutdown Delay 25 ns

PWM: H VTRI, VSWH: H L

PWM: VTRI H, VSWH: L H

tTSEXIT Tri-State Propagation Delay 35 ns

PWM: VTRI L, GL: L H

tLGMIN Low-Side Minimum On-Time SMOD# = L 350 ns

Rev. 1.0 May 2019 www.aosmd.com Page 6 of 17

Downloaded from: http://www.datasheetcatalog.com/

AOZ5311NQI

Electrical Characteristics(4)

TA = 25°C to 125°C. Typical values reflect 25°C ambient temperature; VIN = 12V, VCC= PVCC= DISB# = 5V, unless otherwise spec-

ified.

Symbol Parameter Conditions Min. Typ. Max. Units

(5)

THERMAL NOTIFICATION

TJTHWN Junction Thermal Threshold Temperature Rising 150 °C

TJHYST Junction Thermal Hysteresis 30 °C

VTHWN THWN Pin Output Low ITHWN = 0.5mA 60 mV

RTHWN THWN Pull-Down Resistance 120

Notes:

4. All voltages are specified with respect to the corresponding AGND pin.

5. Characterization value. Not tested in production.

6. GH is the internal pin.

Rev. 1.0 May 2019 www.aosmd.com Page 7 of 17

Downloaded from: http://www.datasheetcatalog.com/

AOZ5311NQI

Timing Diagram

VPWMH

PWM

VPWML

tPDLL

tPDHL

GL

1V 1V

tPDLU

90%

VSWH tPDHU

1V 1V

Figure 1. PWM Logic Input Timing Diagram

PWM VTRI

t TSSHD tTSSHD t TSSHD tTSSHD

GL

t TSEXIT TTSEXIT tTSEXIT t TSEXIT

VSWH

Figure 2. PWM Tri-State Hold Off and Exit Timing Diagram

Rev. 1.0 May 2019 www.aosmd.com Page 8 of 17

Downloaded from: http://www.datasheetcatalog.com/

AOZ5311NQI

Table 1. Input Control Truth Table

DISB# SMOD# PWM(7) GH (Not a Pin) GL

L X X L L

H L H H L

H L H to Tri-State L H, Forward IL

L, Reverse IL

H L L to Tri-State L L

H L L L H

H H H H L

H H L L H

H H Tri-state L L

Note:

7. Diode emulation mode is activated when SMOD# is LOW and PWM transition from HIGH to Tri-State.Zero Cross Detection (ZCD) at IL*Rdson(LS) =

0.5mV to turn off GL.

Rev. 1.0 May 2019 www.aosmd.com Page 9 of 17

Downloaded from: http://www.datasheetcatalog.com/

AOZ5311NQI

Typical Performance Characteristics

TA = 25°C, VIN = 12V, PVCC = VCC = 5V, unless otherwise specified.

94 8.0

7.0

92

6.0

90

Power Ploss (W)

300kHz

Efficiency (%)

5.0

88 500kHz

4.0

86

3.0

84 300kHz

500kHz 2.0

82

1.0

80 0

5 10 15 20 25 30 35 40 5 10 15 20 25 30 35 40

Load Current (A) Load Current (A)

Figure 3. Efficiency vs. Load Current Figure 4. Power Loss vs. Load Current

600 4.0

580 3.5

560 3.0

PVCC Current (uA)

Logic High Threshold

PWM Voltage (V)

540 2.5

520 2.0

Tri-state Window

500 1.5

480 1.0

Logic Low Threshold

460 0.5

440 0.0

-50 -25 0 25 50 75 100 125 150 -50 -25 0 25 50 75 100 125 150

Temperature (°C) Temperature (°C)

Figure 5. Supply Current (IPVCC) vs. Temperature Figure 6. PWM Threshold vs. Temperature

1.8 3.7

1.7 3.6

Rising Threshold

1.6 3.5

SMOD# Voltage (V)

Logic High Threshold

VCC Voltage (V)

1.5 3.4

1.4 3.3

1.3 3.2

Logic Low Threshold

1.2 3.1

Falling Threshold

1.1 3.0

1.0 2.9

-50 -25 0 25 50 75 100 125 150 -50 -25 0 25 50 75 100 125 150

Temperature (°C) Temperature (°C)

Figure 7. SMOD# Threshold vs. Temperature Figure 8. UVLO (VCC) Threshold vs. Temperature

Rev. 1.0 May 2019 www.aosmd.com Page 10 of 17

Downloaded from: http://www.datasheetcatalog.com/

AOZ5311NQI

Typical Performance Characteristics

TA = 25°C, VIN = 12V, PVCC = VCC = 5V, unless otherwise specified.

1.8 4.0

1.7 3.5

1.6 3.0

DISB# Voltage (V)

Logic High Threshold Logic High Threshold

PWM Voltage (V)

1.5 2.5

1.4 2.0 ‐

Tri state Window

1.3 1.5 Logic Low Threshold

Logic Low Threshold

1.2 1.0

1.1 0.5

1.0 0

-50 -25 0 25 50 75 100 125 150 4.2 4.4 4.6 4.8 5.0 5.2 5.4 5.6 5.8

Temperature (°C) VCC Voltage (V)

Figure 9. DISB# Thereshold vs. Temperature Figure 10. PWM Threshold vs. VCC Voltage

Figure 11. High-Side MOSFET SOA Figure 12. Low-Side MOSFET SOA

Rev. 1.0 May 2019 www.aosmd.com Page 11 of 17

Downloaded from: http://www.datasheetcatalog.com/

AOZ5311NQI

Application Information should monitor the current output and protect the load under

all possible operating and transient conditions.

AOZ5311NQI is a fully integrated power module

designed to work over an input voltage range of 2.5V to Disable (DISB#) Function

20V with a separate 5V supply for gate drive and internal

control circuitry. The MOSFETs are individually The AOZ5311NQI can be enabled and disabled through

optimized for efficient operation on both High-Side and DISB# (Pin 31). The driver output is disabled when

Low-Side for a low duty cycle synchronous buck DISB# input is connected to AGND. The module would

converter. High current MOSFET Gate Drivers are be in standby mode with low quiescent current of less

integrated in the package to minimize parasitic loop than 1A. The module will be active when DISB# is

inductance for optimum switching efficiency. connected to VCC Supply. The driver output will follow

PWM input signal. A weak pull-down resistor is

Powering the Module and the Gate Drives connected between DISB# and AGND.

An external supply PVCC = 5V is required for driving the

MOSFETs. The MOSFETs are designed with optimally Power up sequence design must be implemented to

customized gate thresholds voltages to achieve the most ensure proper coordination between the module and

advantageous compromise between fast switching external PWM controller for soft start and system enable/

speed and minimal power loss. The integrated gate driver disable. It is recommended that the AOZ5311NQI should

is capable of supplying large peak current into the Low- be disabled before the PWM controller is disabled. This

Side MOSFET to achieve fast switching. A ceramic would make sure AOZ5311NQI will be operating under

bypass capacitor of 1F or higher is recommended from the recommended conditions.

PVCC (Pin 29) to PGND (Pin 28). The control logic

supply VCC (Pin 3) can be derived from the gate drive Input Voltage VIN

supply PVCC (Pin 29) through an RC filter to bypass the AOZ5311NQI is rated to operate over a wide input range

switching noise (See Typical Application Circuit). from 2.5V to 20V. For high current synchronous buck

converter applications, large pulse current at high

The boost supply for driving the High-Side MOSFET is frequency and high current slew rates (di/dt) will be

generated by connecting a small capacitor (100nF) drawn by the module during normal operation. It is

between the BOOT (Pin 5) and the switching node strongly recommended to place a bypass capacitor very

PHASE (Pin 7). It is recommended that this capacitor close to the package leads at the input supply (VIN). Both

CBOOT should be connected to the device across Pin 5 X7R or X5R quality surface mount ceramic capacitors are

and Pin 7 as close as possible. A bootstrap switch is suitable.

integrated into the device to reduce external component

count. An optional resistor RBOOT in series with CBOOT The High-Side MOSFET is optimized for fast switching

between 1Ω to 5Ω can be used to slow down the turn on by using low gate charges (QG) device. When the

speed of the High-Side MOSFET to achieve both short module is operated at high duty cycle ratio, conduction

switching time and low VSWH switching node spikes at loss from the High-Side MOSFET will be higher. The total

the same time. power loss for the module is still relatively low but the

High-Side MOSFET higher conduction loss may have

Under-Voltage Lockout higher temperature. The two MOSFETs have their own

AOZ5311NQI starts up to normal operation when VCC exposed pads and PCB copper areas for heat

rises above the Under-Voltage Lock-Out (UVLO) dissipation. It is recommended that worst case junction

threshold voltage. The UVLO release is set at 3.5V temperature be measured for both High-Side MOSFET

typically. Since the PWM control signal is provided from and Low-Side MOSFET to ensure that they are operating

an external controller or a digital processor, extra caution within Safe Operating Area (SOA).

must be taken during start up. AOZ5311NQI must be

powered up before PWM input is applied. PWM Input

AOZ5311NQI is compatible with 3V and 5V (CMOS)

Normal system operation begins with a soft start PWM logic. Refer to Figure 1 for PWM logic timing and

sequence by the controller to minimize in-rush current propagation delays diagram between PWM input and the

during start up. Powering the module with a full duty MOSFET gate drives. AOZ5311NQI is compatible with

cycle PWM signal may lead to many undesirable 3V and 5V (CMOS) PWM logic. Refer to Figure 1 for

consequences due to excessive power. AOZ5311NQI PWM logic timing and propagation delays diagram

provides some protections such as UVLO and thermal between PWM input and the MOSFET gate drives.

monitor. For system level protection, the PWM controller

Rev. 1.0 May 2019 www.aosmd.com Page 12 of 17

Downloaded from: http://www.datasheetcatalog.com/

AOZ5311NQI

The PWM is also compatible with Tri-State input. When When the falling edge of switching node VSWH goes

the PWM output from the external PWM controller is in below 1V, the blanking period is activated. After a pre-

high impedance or not connected both High-Side and determined value (tPDHL), the complementary Low-Side

Low-Side MOSFETs are turned off and VSWH is in high Gate Driver output GL is turned on

impedance state. Table 2 shows the thresholds level for

high-to-low and low-to-high transitions as well as Tri- This mechanism prevents cross conduction across the

State window. input bus line VIN and PGND. The anti-overlap circuit

monitors the switching node VSWH to ensure a smooth

There is a Hold-off Delay between the corresponding transition between the two MOSFETs under any load

PWM Tri-State signal and the MOSFET gate drivers to transient conditions.

prevent spurious triggering of Tri-State mode which may

be caused by noise or PWM signal glitches. The Hold-off Thermal Warning (THWN)

Delay is typically 25ns. The driver IC temperature is internally monitored and an

thermal warning flag at THWN (Pin 30) is asserted if it

Table 2. PWM Input and Tri-State Thresholds exceeds 150°C. This warning flag is reset when the

temperature drop back to 120°C. THWN is an open drain

Thresholds VPWMH VPWML VTRIH VTRIL

output that is pulled to AGND to indicate an over-

AOZ5311NQI 2.7 V 0.72 V 1.35 V 1.95 V temperature condition. It should be connected to VCC

Note: See Figure 2 for propagation delays and tri-state window.

through a resistor for monitoring purpose. The device

will not power down during the over temperature

Diode Mode Emulation of Low Side MOSFET condition.

(SMOD#)

AOZ5311NQI can be operated in the diode emulation or PCB Layout Guidelines

pulse skipping mode using SMOD# (Pin 2). This enables AOZ5311NQI is a high current module rated for

the converter to operate in asynchronous mode during operation up to 2MHz. This requires fast switching

start up, light load or under pre-bias conditions. speed to keep the switching losses and device

temperatures within limits. An integrated gate driver

When SMOD# is high, the module will operate in within the package eliminates driver-to-MOSFET gate

Continuous Conduction Mode (CCM). The Driver logic pad parasitic of the package or on PCB.

will use the PWM signal and generate both the High-Side

and Low-Side complementary gate drive outputs with To achieve high switching speeds, high levels of slew

minimal anti-overlap delays to avoid cross conduction. rate (dv/dt and di/dt) will be present throughout the

power train which requires careful attention to PCB

When SMOD# is low, the module can operate in layout to minimize voltage spikes and other transients.

Discontinuous Conduction Mode (DCM). The High-Side As with any synchronous buck converter layout, the

MOSFET gate drive output is not affected but Low-Side critical requirement is to minimize the path of the primary

MOSFET will enter diode emulation mode. See Table 2 switching current loop formed by the High-Side MOSFET,

for all truth table for DISB#, SMOD# and PWM inputs. Low-Side MOSFET, and the input bypass capacitor CIN.

The PCB design is greatly simplified by the optimization

Gate Drives

of the AOZ5311NQI pin out. The power inputs of VIN

AOZ5311NQI has an internal high current high speed and PGND are located adjacent to each other and the

driver that generates the floating gate driver for the High- input bypass capacitors CIN should be placed as close

Side MOSFET and a complementary driver for the Low- as possible to these pins. The area of the secondary

Side MOSFET. An internal shoot through protection switching loop is formed by Low-Side MOSFET, output

scheme is implemented to ensure that both MOSFETs inductor L1, and output capacitor COUT is the next

cannot be turned on at the same time. The operation of critical requirement. This requires second layer or “Inner

PWM signal transition is illustrated as below. 1” to be the PGND plane. VIAs should then be placed

near PGND pads.

1. PWM from logic Low to logic High

While AOZ5311NQI is a highly efficient module, it is still

When the falling edge of Low-Side Gate Driver output GL dissipating significant amount of heat under high power

goes below 1V, the blanking period is activated. After a conditions. Special attention is required for thermal

pre-determined value (tPDHU), the complementary High- design. MOSFETs in the package are directly attached to

Side Gate Driver output GH is turned on. individual exposed pads (VIN and PGND) to simplify

thermal management. Both VIN and VSWH pads should

2. PWM from logic High to logic Low be attached to large areas of PCB copper. Thermal relief

Rev. 1.0 May 2019 www.aosmd.com Page 13 of 17

Downloaded from: http://www.datasheetcatalog.com/

AOZ5311NQI

pads should be placed to ensure proper heat dissipation descending down through the rest of the layers. Refer to

to the board. An inner power plane layer dedicated to Figure 14.

VIN, typically the high voltage system input, is desirable

and VIAs should be provided near the device to connect

the VIN pads to the power plane. Significant amount of

heat can also be dissipated through multiple PGND pins.

A large copper area connected to the PGND pins in

addition to the system ground plane through VIAs will

further improve thermal dissipation.

As shown on Figure. 13, the top most layer of the PCB

should comprise of wide and exposed copper area for

the primary AC current loop which runs along VIN pad

originating from the input capacitors C10, C11 and C12

that are mounted to a large PGND pad. They serve as

thermal relief as heat flows down to the VIN exposed pad

that fan out to a wider area. Adding VIAs will only help

transfer heat to cooler regions of the PCB board through

Figure 14. Bottom Layer PCB layout, VSWH Copper Plane

the other layers beneath but serve no purpose to AC Voided on Descending Layers

activity as all the AC current sees the lowest impedance

on the top layer only. Positioning via through the landing pattern of the VIN and

PGND thermal pads will help quickly facilitate the thermal

build up and spread the heat much more quickly towards

the surrounding copper layers descending from the top

layer. (See RECOMMENDED LANDING PATTERN AND

VIA PLACEMENT section).

The exposed pads dimensional footprint of the 5x5 QFN

package is shown on the package dimensions page. For

optimal thermal relief, it is recommended to fill the PGND

and VIN exposed landing pattern with 10mil diameter

VIAs. 10mil diameter is a commonly used via diameter as

it is optimally cost effective based on the tooling bit used

in manufacturing. Each via is associated with a 20mil

diameter keep out. Maintain a 5mil clearance (127um)

Figure 13. Top Layer of Demo Board, VIN, VSWH and around the inside edge of each exposed pad in an event

PGND Copper Planes of solder overflow, potentially shorting with the adjacent

expose thermal pad.

As the primary and secondary (complimentary) AC

current loops move through VIN to VSWH and through

PGND to VSWH, large positive and negative voltage

spike appear at the VSWH terminal which are caused by

the large internal di/dt produced by the package parasitic.

To minimize the effects of this interference at the VSWH

terminal, at which the main inductor L1 is mounted, size

just enough for the inductor to physically fit. The goal is to

employ the least amount of copper area for this VSWH

terminal, only enough so the inductor can be securely

mounted.

To minimize the effects of switching noise coupling to the

rest of the sensitive areas of the PCB, the area directly

underneath the designated VSWH pad or inductor

terminal is voided and the shape of this void is replicated

Rev. 1.0 May 2019 www.aosmd.com Page 14 of 17

Downloaded from: http://www.datasheetcatalog.com/

AOZ5311NQI

Package Dimensions, QFN5x5A-31L, EP3_S

DIMENSION IN MM DIMENSION IN INCHES

SYMBOLS

MIN NOM MAX MIN NOM MAX

A 0.700 0.750 0.800 0.028 0.030 0.031

A1 0.000 - 0.050 0.000 - 0.002

A2 0.200REF 0.008REF

D 4.900 5.000 5.100 0.193 0.197 0.201

E 4.900 5.000 5.100 0.193 0.197 0.201

D1 1.870 1.920 1.970 0.074 0.076 0.078

D2 0.850 0.900 0.950 0.033 0.035 0.037

D3 0.990 1.040 1.090 0.039 0.041 0.043

D4 0.250 0.300 0.350 0.010 0.012 0.014

D5 0.200 0.250 0.300 0.008 0.010 0.012

E1 3.875 3.925 3.975 0.153 0.155 0.156

E2 1.270 1.320 1.370 0.050 0.052 0.054

E3 2.050 2.100 2.150 0.081 0.083 0.085

E4 0.500 0.550 0.600 0.020 0.022 0.024

E5 1.661 1.711 1.761 0.065 0.067 0.069

E6 3.061 3.111 3.161 0.121 0.122 0.124

E7 0.836 0.886 0.936 0.033 0.035 0.037

E8 1.650 1.700 1.750 0.065 0.067 0.069

L 0.350 0.400 0.450 0.014 0.016 0.018

L1 0.350 0.400 0.450 0.014 0.016 0.018

L2 0.575 0.625 0.675 0.023 0.025 0.027

L3 0.350 0.400 0.450 0.014 0.016 0.018

L4 0.400 0.450 0.500 0.016 0.018 0.020

L5 0.450 0.500 0.550 0.018 0.020 0.022

b 0.200 0.250 0.300 0.008 0.010 0.012

b1 0.130 0.180 0.230 0.005 0.007 0.009

e 0.500BSC 0.020BSC

Rev. 1.0 May 2019 www.aosmd.com Page 15 of 17

Downloaded from: http://www.datasheetcatalog.com/

AOZ5311NQI

Tape and Reel Dimensions, QFN5x5A-31L, EP3_S

Rev. 1.0 May 2019 www.aosmd.com Page 16 of 17

Downloaded from: http://www.datasheetcatalog.com/

AOZ5311NQI

Part Marking

AOZ5311NQI

(QFN5x5)

BLN0

Part Number Code

YWLT

Year Code & Week Code Assembly Lot Code

LEGAL DISCLAIMER

Alpha and Omega Semiconductor makes no representations or warranties with respect to the accuracy or

completeness of the information provided herein and takes no liabilities for the consequences of use of such

information or any product described herein. Alpha and Omega Semiconductor reserves the right to make changes to

such information at any time without further notice. This document does not constitute the grant of any intellectual

property rights or representation of non-infringement of any third party’s intellectual property rights.

LIFE SUPPORT POLICY

ALPHA AND OMEGA SEMICONDUCTOR PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL

COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS.

As used herein: 2. A critical component in any component of a life

support, device, or system whose failure to perform can

1. Life support devices or systems are devices or be reasonably expected to cause the failure of the life

systems which, (a) are intended for surgical implant into support device or system, or to affect its safety or

the body or (b) support or sustain life, and (c) whose effectiveness.

failure to perform when properly used in accordance with

instructions for use provided in the labeling, can be

reasonably expected to result in a significant injury of the

user.

Rev. 1.0 May 2019 www.aosmd.com Page 17 of 17

Downloaded from: http://www.datasheetcatalog.com/

This datasheet has been downloaded from:

www.DatasheetCatalog.com

Datasheets for electronic components.

Downloaded from: http://www.datasheetcatalog.com/

You might also like

- Aoz5311nqi PDFDocument17 pagesAoz5311nqi PDFJohn InfinityNo ratings yet

- AOZ5312NQIDocument17 pagesAOZ5312NQISamuel tuñonNo ratings yet

- AOZ5507QI Support DocumentsDocument17 pagesAOZ5507QI Support DocumentsNorberto CruzNo ratings yet

- High-Current Buck Module for Servers and PCsDocument14 pagesHigh-Current Buck Module for Servers and PCsСергей ГилязитдиновNo ratings yet

- High-Current DrMOS Buck ModuleDocument18 pagesHigh-Current DrMOS Buck ModulePablo AllosiaNo ratings yet

- FSDM0565R: Green Mode Fairchild Power Switch (FPS)Document20 pagesFSDM0565R: Green Mode Fairchild Power Switch (FPS)Najam Ul HassanNo ratings yet

- General Description Features: 28V/12A Synchronous Ezbuck RegulatorDocument16 pagesGeneral Description Features: 28V/12A Synchronous Ezbuck RegulatorholinsunNo ratings yet

- Fairchild - Semiconductor FAN73611MX DatasheetDocument14 pagesFairchild - Semiconductor FAN73611MX DatasheetDeddy WilopoNo ratings yet

- NB679Document18 pagesNB679Tri Nguyen Real EstateNo ratings yet

- FDMF 6823 DCDocument19 pagesFDMF 6823 DCtechgamebr85No ratings yet

- 2.75V To 17V, 6A, 1.2Mhz, Synchronous, Ultra-Thin Power Module Description FeaturesDocument22 pages2.75V To 17V, 6A, 1.2Mhz, Synchronous, Ultra-Thin Power Module Description FeaturesEugene FlexNo ratings yet

- Nb679a MpsDocument19 pagesNb679a MpswarkeravipNo ratings yet

- FAN7392 High-Current, High-And Low-Side, Gate-Drive IC: Features DescriptionDocument18 pagesFAN7392 High-Current, High-And Low-Side, Gate-Drive IC: Features DescriptionRaghu RamanNo ratings yet

- Arduino Nano 3 User ManualDocument20 pagesArduino Nano 3 User ManualDj PopNo ratings yet

- 28V, 6.5A, Low Iq, Synchronous Buck Converter With 2-Bit VIDDocument24 pages28V, 6.5A, Low Iq, Synchronous Buck Converter With 2-Bit VIDElla Wijaya ChandraNo ratings yet

- OB2263 On-Bright PDFDocument13 pagesOB2263 On-Bright PDFamaliah bamesuNo ratings yet

- ADP3410Document12 pagesADP3410Edson ConceicaoNo ratings yet

- An 4150 PDFDocument18 pagesAn 4150 PDFVeerababu SilaparasettiNo ratings yet

- Is Now Part ofDocument18 pagesIs Now Part ofVeerababu SilaparasettiNo ratings yet

- FS7M0680, FS7M0880: Fairchild Power Switch (FPS)Document18 pagesFS7M0680, FS7M0880: Fairchild Power Switch (FPS)Candelaria CortesNo ratings yet

- Infineon ICE5ARxxxxBZS DS v02 - 10 EN PDFDocument36 pagesInfineon ICE5ARxxxxBZS DS v02 - 10 EN PDFanand shekhawatNo ratings yet

- FAN7602C Green Current Mode PWM Controller: Features DescriptionDocument19 pagesFAN7602C Green Current Mode PWM Controller: Features DescriptionAmjad ZaidNo ratings yet

- HIP6302CBDocument18 pagesHIP6302CBrjbordaNo ratings yet

- MP3391Document18 pagesMP3391Raul AlfaroNo ratings yet

- MP3391 r1.12Document18 pagesMP3391 r1.12Elsa Nababan EchaNo ratings yet

- A4950 DatasheetDocument9 pagesA4950 DatasheetIndra KurniawanNo ratings yet

- Fsl117mrin 1010027Document18 pagesFsl117mrin 1010027ferreirabarbo93065gmail.com BarboNo ratings yet

- Aoz2262qi 1Document16 pagesAoz2262qi 1Eric ArcherNo ratings yet

- FAN7602 Datasheet PDFDocument17 pagesFAN7602 Datasheet PDFSergio Daniel BarretoNo ratings yet

- DM0565RDocument20 pagesDM0565RSURESH CHANDRA ROUTNo ratings yet

- Ic Fan73832Document18 pagesIc Fan73832David CoronadoNo ratings yet

- DM311Document16 pagesDM311Hernan Ortiz EnamoradoNo ratings yet

- 24V, High Current Synchronous Buck Converter With +/-1.5A LDO and Buffed ReferenceDocument21 pages24V, High Current Synchronous Buck Converter With +/-1.5A LDO and Buffed Reference8ctanoNo ratings yet

- G5725 1MHz 1A Synchronous Step-Down RegulatorDocument2 pagesG5725 1MHz 1A Synchronous Step-Down RegulatorM. M.No ratings yet

- 5V/12V Synchronous-Rectified Buck Controller With Reference InputDocument19 pages5V/12V Synchronous-Rectified Buck Controller With Reference InputIgor LabutinNo ratings yet

- gm07652r PDFDocument21 pagesgm07652r PDFjose luisNo ratings yet

- A4975 DatasheetDocument15 pagesA4975 DatasheetWisard MagalhãesNo ratings yet

- An 4103Document16 pagesAn 4103taninavcoNo ratings yet

- DP2269Document7 pagesDP2269GABRIEL AMORIM ARAUJONo ratings yet

- FDMF6823B FairchildSemiconductorDocument19 pagesFDMF6823B FairchildSemiconductortechgamebr85No ratings yet

- CR6224Document10 pagesCR6224sergioviriliNo ratings yet

- Datasheet DMO565RDocument21 pagesDatasheet DMO565RSteve Bravo83% (6)

- F DatasheetDocument16 pagesF DatasheetTerelia Kinan GallenNo ratings yet

- Driver de Motor Paso A PasoDocument4 pagesDriver de Motor Paso A PasoRoberto GonzalesNo ratings yet

- DP9127V DPDocument11 pagesDP9127V DPGustavo AlonsoNo ratings yet

- Datasheet FSL117MRINDocument15 pagesDatasheet FSL117MRINeurofutabNo ratings yet

- Sunrom 814104Document13 pagesSunrom 814104Valentin LeonteNo ratings yet

- Datasheet AUIRS1170SDocument28 pagesDatasheet AUIRS1170SJesus HernadezNo ratings yet

- 6A, 23V, 500Khz, Acot Synchronous Buck Converter With Ldo For System 3.3VDocument18 pages6A, 23V, 500Khz, Acot Synchronous Buck Converter With Ldo For System 3.3VDanny RiveroNo ratings yet

- LMR 23625Document43 pagesLMR 23625GaneshNo ratings yet

- Programmable DC/DC Controller For Advanced Microprocessors: Device Package Temp Range (T)Document6 pagesProgrammable DC/DC Controller For Advanced Microprocessors: Device Package Temp Range (T)ibrahim başderNo ratings yet

- Fan 73892Document20 pagesFan 73892heribertosfaNo ratings yet

- FSCQ1565RT: Green Mode Fairchild Power Switch (FPS) For Quasi-Resonant Switching ConverterDocument25 pagesFSCQ1565RT: Green Mode Fairchild Power Switch (FPS) For Quasi-Resonant Switching ConverterPaulo Roberto s freireNo ratings yet

- LD5760-DS-02 LeadtrendDocument20 pagesLD5760-DS-02 Leadtrendvahid hoseinpourNo ratings yet

- Features: 40A Drmos Power Module With Integrated Diode Emulation and Thermal Warning OutputDocument15 pagesFeatures: 40A Drmos Power Module With Integrated Diode Emulation and Thermal Warning OutputantoniocljNo ratings yet

- FSCQ1565RP: Green Mode Fairchild Power Switch (FPS) For Quasi-Resonant Switching ConverterDocument24 pagesFSCQ1565RP: Green Mode Fairchild Power Switch (FPS) For Quasi-Resonant Switching ConverterManuelAlejandroVicuñaRojasNo ratings yet

- FSCQ0765RT PDFDocument25 pagesFSCQ0765RT PDFGreivin GonzálezNo ratings yet

- Up 9505Document40 pagesUp 9505techgamebr85No ratings yet

- UP1962SDocument14 pagesUP1962Stechgamebr85No ratings yet

- RT8125C 6XDocument17 pagesRT8125C 6Xtechgamebr85No ratings yet

- RT7296FGJ8FDocument12 pagesRT7296FGJ8FManuel PuntosNo ratings yet

- Sic 632Document19 pagesSic 632techgamebr85No ratings yet

- Rt8816a-06 Gtx1070 Gigabyte MemoriasDocument21 pagesRt8816a-06 Gtx1070 Gigabyte Memoriastechgamebr85No ratings yet

- Tps 51218Document27 pagesTps 51218techgamebr85No ratings yet

- DS7296F-05 Marking08Document15 pagesDS7296F-05 Marking08carol2No ratings yet

- FDMF 6823 DCDocument19 pagesFDMF 6823 DCtechgamebr85No ratings yet

- NCP 4208Document30 pagesNCP 4208techgamebr85No ratings yet

- Mp1474 - Iadkf - Xbox One - StdbyDocument16 pagesMp1474 - Iadkf - Xbox One - StdbyDiamantes EletrônicosNo ratings yet

- GIGABYTE GEFORCE GTX 760 GV-N760OC-2GD (P2002 2GB GDDR5, 256b, 64Mx32) REV. 2.0Document34 pagesGIGABYTE GEFORCE GTX 760 GV-N760OC-2GD (P2002 2GB GDDR5, 256b, 64Mx32) REV. 2.0Juan RiquelmeNo ratings yet

- Gigabyte GV-N1060G1 GAMING-6GD Rev 2.0Document42 pagesGigabyte GV-N1060G1 GAMING-6GD Rev 2.0Roger Ricardo Reis EduardoNo ratings yet

- Remote Sensing Mineral Exploration LithiumDocument16 pagesRemote Sensing Mineral Exploration LithiumGerald Darshan MogiNo ratings yet

- AEIOU Framework - Case Study On Agriculture Domain (Automatic Drip Tube Irrigation System)Document30 pagesAEIOU Framework - Case Study On Agriculture Domain (Automatic Drip Tube Irrigation System)Kunal TalegaonkarNo ratings yet

- Population Density: Factors and Global DistributionDocument16 pagesPopulation Density: Factors and Global DistributionRYANJUSTIN NICOLASNo ratings yet

- Agribusiness ManagementDocument20 pagesAgribusiness Managementronald_leabresNo ratings yet

- GynecologyDocument24 pagesGynecologylovelots1234No ratings yet

- Strength of CSG and TBGDocument10 pagesStrength of CSG and TBGTiffany DacinoNo ratings yet

- Service Manual: Mds-Ja20EsDocument84 pagesService Manual: Mds-Ja20Esfoxmulder6161695No ratings yet

- B757-200 MPDDocument393 pagesB757-200 MPDSebastian Rendon100% (3)

- Assessing A Peripheral PulseDocument5 pagesAssessing A Peripheral Pulsecrrfrnc0% (1)

- Frequency-Domain Analysis of Discrete-Time Signals and SystemsDocument31 pagesFrequency-Domain Analysis of Discrete-Time Signals and SystemsSwatiSharmaNo ratings yet

- NEDO's Role in International Technical Cooperation ProjectsDocument45 pagesNEDO's Role in International Technical Cooperation Projectsamitsh20072458No ratings yet

- Relative Density and Load Capacity of SandsDocument14 pagesRelative Density and Load Capacity of SandsgatotNo ratings yet

- A Perspective in Accelerated Orthodontics With Aligner Treatment 2017 Seminars in OrthodonticsDocument7 pagesA Perspective in Accelerated Orthodontics With Aligner Treatment 2017 Seminars in Orthodonticsdruzair007No ratings yet

- Comparison and Contrast EssayDocument2 pagesComparison and Contrast Essayputri fadillahNo ratings yet

- Underwater Cutting and Welding Equipment - 89250054 - AbDocument38 pagesUnderwater Cutting and Welding Equipment - 89250054 - AbAhmed Adel100% (1)

- NIA045462022 KL 13 AR 1130 Royal Enfield Motors LTD Classic X 350 ESDocument10 pagesNIA045462022 KL 13 AR 1130 Royal Enfield Motors LTD Classic X 350 ESAkhil DasNo ratings yet

- Well Components: Petroleum Production Engineering. DOI: © 2007 Elsevier Inc. All Rights ReservedDocument15 pagesWell Components: Petroleum Production Engineering. DOI: © 2007 Elsevier Inc. All Rights Reservedsoran najebNo ratings yet

- Less Than 60 MilesDocument36 pagesLess Than 60 MilesDavid MckinleyNo ratings yet

- Usg Iom PDFDocument56 pagesUsg Iom PDFAnonymous 7xHNgoKE6eNo ratings yet

- HP DeskJet Report POM 20150413Document5 pagesHP DeskJet Report POM 20150413Carolina DelgadoNo ratings yet

- Shell Marine Pocketbook For International MarineDocument60 pagesShell Marine Pocketbook For International MarineGage Cendk HNo ratings yet

- Attack TCSDocument93 pagesAttack TCSjosekinNo ratings yet

- Syngo MR E11 OncoDocument64 pagesSyngo MR E11 OncoLuís GuerraNo ratings yet

- Interview Questions - Godrej Technical & HR Interview QuestionsDocument9 pagesInterview Questions - Godrej Technical & HR Interview Questionssasithar jaisankaranNo ratings yet

- Unit 1 Unit 2 Unit 3 DIFFERENTIAL CALCULUS 1 2 3 PDFDocument124 pagesUnit 1 Unit 2 Unit 3 DIFFERENTIAL CALCULUS 1 2 3 PDFjayaram prakash kNo ratings yet

- Des 415 Research 01Document29 pagesDes 415 Research 01Just scribble me For funNo ratings yet

- Form Vs Content in P.K. Dick's The Father ThingDocument4 pagesForm Vs Content in P.K. Dick's The Father ThingFrank BertrandNo ratings yet

- ABR College Mechanical Mid Exam Questions on MetrologyDocument1 pageABR College Mechanical Mid Exam Questions on MetrologySrinu ArnuriNo ratings yet

- DL Throughput Improvement with Aperiodic CQI ReportingDocument10 pagesDL Throughput Improvement with Aperiodic CQI ReportingAqeel HasanNo ratings yet

- MR Skin Prick TestingDocument9 pagesMR Skin Prick TestingAyuAnatrieraNo ratings yet