Professional Documents

Culture Documents

16 Bit Alu in VHDL

16 Bit Alu in VHDL

Uploaded by

puppyrOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

16 Bit Alu in VHDL

16 Bit Alu in VHDL

Uploaded by

puppyrCopyright:

Available Formats

16 bit alu in vhdl

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

use IEEE.NUMERIC_STD.ALL;

entity alu is

Port ( r : in std_logic_vector(15 downto 0);

w : in std_logic_vector(15 downto 0);

d : in std_logic_vector(3 downto 0);

clk : in std_logic;

f : out std_logic_vector(15 downto 0));

end alu;

architecture behavioral of alu is

begin

process(r,w,d,clk)

begin

if clk'event and clk='1' then

case d is

when "0000" =>f<= w and r;

when "0001" =>f<= w or r;

when "0010" =>f<= w nor r;

when "0011" =>f<= w xor r;

when "0100" =>f<= w xnor r;

when "0101" =>f<= w nand r;

when "0110" =>f<= not r;

when "0111" =>f<= w + r;

when "1000" =>f<= r - w;

when "1001" =>f<= r+"0000000000000001";

when "1010" =>f<= w-"0000000000000001";

when "1011" =>f<= r;

when others =>f<= "0000000000000000";

end case;

end if;

end process;

end behavioral;

test bench

LIBRARY ieee;

USE ieee.std_logic_1164.ALL;

-- Uncomment the following library declaration if using

-- arithmetic functions with Signed or Unsigned values

USE ieee.numeric_std.ALL;

ENTITY alut IS

END alut;

ARCHITECTURE behavior OF alut IS

-- Component Declaration for the Unit Under Test (UUT)

COMPONENT alu

PORT(

r : IN std_logic_vector(15 downto 0);

w : IN std_logic_vector(15 downto 0);

d : IN std_logic_vector(3 downto 0);

clk : IN std_logic;

f : OUT std_logic_vector(15 downto 0)

);

END COMPONENT;

--Inputs

signal r : std_logic_vector(15 downto 0) := (others => '0');

signal w : std_logic_vector(15 downto 0) := (others => '0');

signal d : std_logic_vector(3 downto 0) := (others => '0');

signal clk : std_logic := '0';

--Outputs

signal f : std_logic_vector(15 downto 0);

-- Clock period definitions

constant clk_period : time := 10 ns;

BEGIN

-- Instantiate the Unit Under Test (UUT)

uut: alu PORT MAP (

r => r,

w => w,

d => d,

clk => clk,

f => f

);

-- Clock process definitions

clk_process :process

begin

clk <= '0';

wait for clk_period/2;

clk <= '1';

wait for clk_period/2;

end process;

-- Stimulus process

stim_proc: process

begin

-- hold reset state for 100 ns.

wait for 100 ns;

-- insert stimulus here

r<="0000000000000010";

w<="0000000000000011";

wait for 20 ns;

d<="0000";

wait for 20 ns;

r<="0000000000000010";

w<="0000000000000011";

d<="0001";

wait for 20 ns;

r<="0000000000000010";

w<="0000000000000011";

d<="0010";

wait for 20 ns;

r<="0000000000000010";

w<="0000000000000011";

d<="0011";

wait for 20 ns;

r<="0000000000000010";

w<="0000000000000011";

d<="0100";

wait for 20 ns;

r<="0000000000000010";

w<="0000000000000011";

d<="0101";

wait for 20 ns;

r<="0000000000000010";

d<="0110";

wait for 20 ns;

r<="0000000000000010";

w<="0000000000000011";

d<="0111";

wait for 20 ns;

r<="0000000000000010";

w<="0000000000000011";

d<="1000";

wait for 20 ns;

r<="0000000000000010";

d<="1001";

wait for 20 ns;

w<="0000000000000011";

d<="1010";

wait for 20 ns;

r<="0000000000000010";

d<="1011";

wait for 20 ns;

wait;

end process;

END;

You might also like

- Focal Catalog StudioMonitor 2016Document40 pagesFocal Catalog StudioMonitor 2016guitaristddjNo ratings yet

- Some VHDL CodesDocument11 pagesSome VHDL CodesFABIO DAVID HERNANDEZ MARTINEZNo ratings yet

- S7-1500 ModbusRTU PROJ v21 enDocument39 pagesS7-1500 ModbusRTU PROJ v21 enManju Nath100% (1)

- M Us 22054 LC-WM Handbook Reva PDFDocument120 pagesM Us 22054 LC-WM Handbook Reva PDFneo43No ratings yet

- VHDL Code For LCD DisplayDocument7 pagesVHDL Code For LCD DisplayNguyễn Văn TâmNo ratings yet

- Formulas For EE 201Document3 pagesFormulas For EE 201berickson_14No ratings yet

- H13-Electronic Injection PDFDocument101 pagesH13-Electronic Injection PDFrafael alcantaraNo ratings yet

- Stop Watch Coding (VHDL)Document15 pagesStop Watch Coding (VHDL)Anonymous ZCb9xz100% (1)

- Digital Clock in VHDLDocument2 pagesDigital Clock in VHDLTapas KolteNo ratings yet

- Lecture 4 Maximum PrincipleDocument21 pagesLecture 4 Maximum Principlemohamed-gamaaNo ratings yet

- Library IeeeDocument3 pagesLibrary IeeeRyan Sharpe60% (5)

- VHDL Interfacing ProgramsDocument22 pagesVHDL Interfacing ProgramsNithish ManjuNo ratings yet

- Electiva - CIRCUITOS SECUENCIALES EN VHDLDocument5 pagesElectiva - CIRCUITOS SECUENCIALES EN VHDLfer gutiNo ratings yet

- Function: TestbenchDocument27 pagesFunction: TestbenchY AmulyaNo ratings yet

- Lab 5 Firna FrilanisaDocument18 pagesLab 5 Firna FrilanisaFirna FrilanisaNo ratings yet

- Subiecte Tip Examen Vlsi1Document21 pagesSubiecte Tip Examen Vlsi1Iuli SirbuNo ratings yet

- Solution Manual of Appendix A Exercise at (CMOS VLSI Design) by NEILL and HarrisDocument13 pagesSolution Manual of Appendix A Exercise at (CMOS VLSI Design) by NEILL and HarrisAhmed Gad100% (1)

- VHDL SkriptaDocument98 pagesVHDL SkriptaLana HajroNo ratings yet

- Practica No4. Simulaciones Mediante Fuentes Test Bench: VHDL ModuleDocument6 pagesPractica No4. Simulaciones Mediante Fuentes Test Bench: VHDL ModuleAndrea jaimesNo ratings yet

- MemoriaDocument10 pagesMemoriaAlvaroNo ratings yet

- PR 1 - Alu 4 Bit OmkarDocument6 pagesPR 1 - Alu 4 Bit OmkarSEN158Omkar SalunkeNo ratings yet

- Expt No.:1 Batch: B4 Roll No.:404B070Document10 pagesExpt No.:1 Batch: B4 Roll No.:404B070Aishwarya RautNo ratings yet

- TB Elevator0Document2 pagesTB Elevator0Jimy Yan LinNo ratings yet

- Engr2015 Lab2Document13 pagesEngr2015 Lab2SUPER AMAZINGNo ratings yet

- HardwareDocument4 pagesHardwareHarish SvNo ratings yet

- Lab 6 Firna FrilanisaDocument22 pagesLab 6 Firna FrilanisaFirna FrilanisaNo ratings yet

- AIM OF THE EXPERIMENT:-Binary To Decimal, Gray Code Apparatus RequiredDocument8 pagesAIM OF THE EXPERIMENT:-Binary To Decimal, Gray Code Apparatus RequiredSai KaneNo ratings yet

- Codigo Electronica Digital - Con - CajasDocument11 pagesCodigo Electronica Digital - Con - CajasLeidysita RamirezNo ratings yet

- Programme No.10 AIM-To Design A D - Flip Flop CODE - Following Is The VHDL Code For Simulation of D Flip FlopDocument8 pagesProgramme No.10 AIM-To Design A D - Flip Flop CODE - Following Is The VHDL Code For Simulation of D Flip FlopAnkit GoelNo ratings yet

- VHDL Codes For Mips Instructions LW, SW, Beq, Bne, J, Jal, Lui, Add, Addi, Or, Ori, SLT, Nor, And, ExceptionsDocument24 pagesVHDL Codes For Mips Instructions LW, SW, Beq, Bne, J, Jal, Lui, Add, Addi, Or, Ori, SLT, Nor, And, ExceptionsbingoahaNo ratings yet

- Half AdderDocument11 pagesHalf AdderTahsin RahmanNo ratings yet

- Comp Arch ElevatorDocument24 pagesComp Arch ElevatorUtkarsh KumarNo ratings yet

- Computer Architecture & Digital Hardware Design (ECD09) : (Practical File)Document18 pagesComputer Architecture & Digital Hardware Design (ECD09) : (Practical File)prem kumarNo ratings yet

- Bach Khoa University of Technology: Digital Systems Laboratory Prelab 4 Finite State MachineDocument11 pagesBach Khoa University of Technology: Digital Systems Laboratory Prelab 4 Finite State MachineMờ LanhNo ratings yet

- TB ElevadorDocument2 pagesTB ElevadorJimy Yan LinNo ratings yet

- FPGA应用举例Document12 pagesFPGA应用举例lieshi2958100% (1)

- Pico VHDLDocument6 pagesPico VHDLapi-584316598No ratings yet

- 3Document2 pages3Nguyễn Tiến DũngNo ratings yet

- Problema 1 "Lavadora" Código VHDL ModuleDocument40 pagesProblema 1 "Lavadora" Código VHDL ModuleLeonardoNo ratings yet

- Thiết kế bộ so sánh 2 số nhị phân 4 bitDocument10 pagesThiết kế bộ so sánh 2 số nhị phân 4 bitt4jpr0No ratings yet

- D Flip FlopDocument11 pagesD Flip FlopGurdeep SinghNo ratings yet

- Module of D Flip FlopDocument11 pagesModule of D Flip FlopGurdeep SinghNo ratings yet

- Design Code For CounterDocument6 pagesDesign Code For CounterPranita BhosaleNo ratings yet

- HDL InterfacingDocument8 pagesHDL InterfacingshastryNo ratings yet

- Correction TPDocument4 pagesCorrection TPHichem GuedriNo ratings yet

- Shift Register: CodeDocument3 pagesShift Register: Code1432badassNo ratings yet

- UARTDocument19 pagesUARTErick LoolNo ratings yet

- Testbench For OR GateDocument5 pagesTestbench For OR GateMae ZelNo ratings yet

- Memorie FifoDocument4 pagesMemorie FifoAlexNo ratings yet

- PONGDocument8 pagesPONGJuan Luis Mamani SirpaNo ratings yet

- Ejemplos VHDLDocument5 pagesEjemplos VHDLLeón Emmanuel NNo ratings yet

- AP Lab 9Document19 pagesAP Lab 9Latest TechiansNo ratings yet

- LCD ControllerDocument4 pagesLCD Controllerbinhnhi0007No ratings yet

- Proyecto Código PrincipalDocument18 pagesProyecto Código PrincipalFrancisco Javier ReyesNo ratings yet

- Aplicaciones Spartan6 Ver1Document42 pagesAplicaciones Spartan6 Ver1juan mezaNo ratings yet

- Interface Verilog CodeDocument21 pagesInterface Verilog CodeVishwanath B RajashekarNo ratings yet

- Tugas8 - 2210191006 - Filosofi Dwibakti - LapsemDocument23 pagesTugas8 - 2210191006 - Filosofi Dwibakti - LapsemFD SyndromeNo ratings yet

- Interrogation 1: Nom: Prenom: ..Document3 pagesInterrogation 1: Nom: Prenom: ..capoNo ratings yet

- N Bit Adder: VHDL CodeDocument3 pagesN Bit Adder: VHDL Codeabhay kumarNo ratings yet

- Lab 1 ReportDocument7 pagesLab 1 ReportNguyễn ThắngNo ratings yet

- Up Counter 7 Segment Display Using Clock Divider CircuitDocument7 pagesUp Counter 7 Segment Display Using Clock Divider CircuitRavindra Mathanker50% (2)

- 4 Bit AluDocument2 pages4 Bit AluMansi LangadeNo ratings yet

- BCD Con Contador en VHDLDocument7 pagesBCD Con Contador en VHDLGian SusanaNo ratings yet

- Dic File - 7 SemDocument22 pagesDic File - 7 SemShalini SharmaNo ratings yet

- Electron Devices and IcsDocument4 pagesElectron Devices and IcspuppyrNo ratings yet

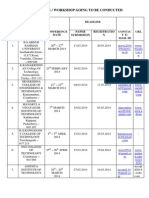

- Conference / Workshop Going To Be Conducted: DeadlineDocument2 pagesConference / Workshop Going To Be Conducted: DeadlinepuppyrNo ratings yet

- CPLD ProgDocument33 pagesCPLD ProgpuppyrNo ratings yet

- NC7101Document6 pagesNC7101puppyrNo ratings yet

- CTS - 1 - Answer KeyDocument1 pageCTS - 1 - Answer KeypuppyrNo ratings yet

- Synchronous Fifo PGMDocument3 pagesSynchronous Fifo PGMpuppyrNo ratings yet

- Sub Code & Name:: DOC/LP/01/28.02.02Document6 pagesSub Code & Name:: DOC/LP/01/28.02.02puppyrNo ratings yet

- Test Paper:6 Paper Type: Whole Testpaper Test Date: 26 December 2010 Test Location: Chennai Posted By: SanjayDocument9 pagesTest Paper:6 Paper Type: Whole Testpaper Test Date: 26 December 2010 Test Location: Chennai Posted By: SanjaypuppyrNo ratings yet

- QMFDocument3 pagesQMFpuppyrNo ratings yet

- Clocked Synchronous Sequential Circuits: ExampleDocument4 pagesClocked Synchronous Sequential Circuits: ExamplepuppyrNo ratings yet

- About The InstitutionDocument3 pagesAbout The InstitutionpuppyrNo ratings yet

- QP 1Document3 pagesQP 1puppyrNo ratings yet

- Rajalakshmi Engineering College MG 1351 - Principles of Management - Lesson Plan VI Sem Mechanical Engineering Lecture Hour Topic UnitDocument2 pagesRajalakshmi Engineering College MG 1351 - Principles of Management - Lesson Plan VI Sem Mechanical Engineering Lecture Hour Topic UnitpuppyrNo ratings yet

- Data Fusion TechniqueDocument8 pagesData Fusion TechniquepuppyrNo ratings yet

- Project Details 2010-11Document5 pagesProject Details 2010-11puppyrNo ratings yet

- VLSI Anna University New Syllabus 2013Document33 pagesVLSI Anna University New Syllabus 2013princeram123No ratings yet

- Ece5745 Tut3 IccDocument6 pagesEce5745 Tut3 IccAnonymous UeI6DVNo ratings yet

- AFC492 eDocument3 pagesAFC492 eAlvaro SanchezNo ratings yet

- Chapter7. FET Biasing: JFET Biasing Configurations Fixed Biasing Self Biasing & Common Gate Voltage DividerDocument42 pagesChapter7. FET Biasing: JFET Biasing Configurations Fixed Biasing Self Biasing & Common Gate Voltage DividerjamesNo ratings yet

- WPG80 16Document4 pagesWPG80 16AlanNo ratings yet

- Application On Three Phase Induction Motor: ObjectivesDocument5 pagesApplication On Three Phase Induction Motor: ObjectivesAdnan AltafNo ratings yet

- Project Contol SystemsDocument10 pagesProject Contol SystemsazamatNo ratings yet

- Redrawing Curva Capability GridDocument9 pagesRedrawing Curva Capability GridarekimbaNo ratings yet

- MOVFR - InstallationDocument32 pagesMOVFR - InstallationSabavoon FazliNo ratings yet

- Technical Data For ADL Power SuppliesDocument48 pagesTechnical Data For ADL Power Suppliesstar2002sun5gmail.comNo ratings yet

- XTS5000InstructionV5Document5 pagesXTS5000InstructionV5Dra CavisNo ratings yet

- Ecg Spo Nibp Temp: Multiparameter Patient Monitoring ModuleDocument1 pageEcg Spo Nibp Temp: Multiparameter Patient Monitoring ModuleRaden Ayu Nurfadhillah RifqahNo ratings yet

- Res wlrd6gDocument2 pagesRes wlrd6gMUHAMMAD TAUFIQNo ratings yet

- Digital Logic Design Homework #2: Name: Đinh Thanh Tùng ID: EEACIU18098Document5 pagesDigital Logic Design Homework #2: Name: Đinh Thanh Tùng ID: EEACIU18098Tung DinhNo ratings yet

- 100 Kva Caterpillar Branded FG Wilson DG SetDocument4 pages100 Kva Caterpillar Branded FG Wilson DG SetMaintenance Unit Anil GroupNo ratings yet

- Compressor Technical DataDocument3 pagesCompressor Technical DataLuis GarciaNo ratings yet

- Design and Simulation of 60kWp Solar On-Grid System For Rural Area in Uttar-Pradesh by "PVsyst"Document13 pagesDesign and Simulation of 60kWp Solar On-Grid System For Rural Area in Uttar-Pradesh by "PVsyst"fatemeh mohammadiNo ratings yet

- Disassembly:: W 0704 M0 Gas-MixerDocument4 pagesDisassembly:: W 0704 M0 Gas-MixerHelder PintoNo ratings yet

- Controls Man Techman Easc24115230 7 08Document19 pagesControls Man Techman Easc24115230 7 08Welmi AfdalNo ratings yet

- X7R Dielectric: General SpecificationsDocument4 pagesX7R Dielectric: General SpecificationsnkswarunNo ratings yet

- M190PW01 V0Document28 pagesM190PW01 V0Tomescu MarianNo ratings yet

- Sequential Circuit Design: Slides ForDocument23 pagesSequential Circuit Design: Slides ForRamarao ChNo ratings yet

- Clause 6.104.2. SC Making and Breaking TestDocument13 pagesClause 6.104.2. SC Making and Breaking Testlnhoang.fgroupNo ratings yet

- Circuit Lab 51Document3 pagesCircuit Lab 51Sulman ShahzadNo ratings yet

- Cat Sensor 242Document42 pagesCat Sensor 242Ramesh KrishnamoorthyNo ratings yet

- 85001-0587 - Audio Notification SystemDocument6 pages85001-0587 - Audio Notification SystemmohammadNo ratings yet

- WM8731 PDFDocument64 pagesWM8731 PDFRAMON JARAMILLO MARTINEZNo ratings yet