Professional Documents

Culture Documents

Dante Experiment#5

Uploaded by

CHRISTIANJOIE DANTEOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Dante Experiment#5

Uploaded by

CHRISTIANJOIE DANTECopyright:

Available Formats

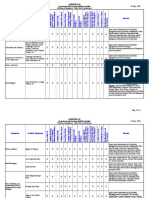

Name: DANTE, CHRISTIAN JOIE C.

Experiment #: 5

Course Code: NCP3201-4CPE - 1B Activity Title: Multiplexer and Demultiplexer

University of the East - Caloocan Page 1 of 4

College of Engineering – CpE Department

University of the East - Caloocan Page 2 of 4

College of Engineering – CpE Department

CODES:

TESTBENCH:

library ieee;

use ieee.std_logic_1164.all; DESIGN:

library IEEE;

entity mux_tb is use IEEE.STD_LOGIC_1164.ALL;

end entity; use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

architecture tb of mux_tb is

component MUX_SOURCE is entity MUX_SOURCE is

Port ( S : in STD_LOGIC_VECTOR (1 downto 0); Port ( S : in STD_LOGIC_VECTOR (1 downto

I : in STD_LOGIC_VECTOR (3 downto 0); 0);

O : out STD_LOGIC); I : in STD_LOGIC_VECTOR (3 downto 0);

end component; O : out STD_LOGIC);

signal S : STD_LOGIC_VECTOR(1 downto 0); end MUX_SOURCE;

signal I : STD_LOGIC_VECTOR(3 downto 0);

signal O : STD_LOGIC; architecture Behavioral of MUX_SOURCE is

begin begin

uut : MUX_SOURCE port map(

S => S, process (S,I)

I => I,

O => O); begin

stim : process

begin if (S <= "00") then

O <= I(0);

I(0) <= '0'; elsif (S <= "01") then

I(1) <= '1'; O <= I(1);

I(2) <= '0'; elsif (S <= "10") then

I(3) <= '1'; O <= I(2);

else

S <= "00";wait for 10 ns; O <= I(3);

S <= "01";wait for 10 ns;

S <= "10";wait for 10 ns; end if;

S <= "11";wait for 10 ns; end process;

wait; end Behavioral;

end process;

end tb;

University of the East - Caloocan Page 3 of 4

College of Engineering – CpE Department

University of the East - Caloocan Page 4 of 4

College of Engineering – CpE Department

You might also like

- ANSI and ISO Geometric Tolerancing Symbols1Document5 pagesANSI and ISO Geometric Tolerancing Symbols1Mahender KumarNo ratings yet

- VHDL CodeDocument34 pagesVHDL CodeHimanshu Thakur100% (1)

- Projects With Microcontrollers And PICCFrom EverandProjects With Microcontrollers And PICCRating: 5 out of 5 stars5/5 (1)

- Discount Factor TemplateDocument5 pagesDiscount Factor TemplateRashan Jida ReshanNo ratings yet

- VHDL LAB 10 FSM Code Solution and Test BenchDocument11 pagesVHDL LAB 10 FSM Code Solution and Test BenchHasanNo ratings yet

- Buku Tahun 5Document234 pagesBuku Tahun 5Hazyzyizuan Bin Abu HassaNo ratings yet

- TP3-VHDL SolutionsDocument3 pagesTP3-VHDL SolutionsfalaNo ratings yet

- Dante Experiment#3Document3 pagesDante Experiment#3CHRISTIANJOIE DANTENo ratings yet

- Mux DemuxDocument8 pagesMux DemuxAadesh LabdeNo ratings yet

- Digital System Design HomeworkDocument5 pagesDigital System Design HomeworkHassanNajjarNo ratings yet

- Mux DemuxDocument4 pagesMux DemuxVinay RaiNo ratings yet

- TugasLab1a - Ichsan Harun Wicaksono - 195060307111011Document16 pagesTugasLab1a - Ichsan Harun Wicaksono - 195060307111011Ichsan WicaksonoNo ratings yet

- Expt 2 Mux 4 1Document3 pagesExpt 2 Mux 4 1Steven VazhappullyNo ratings yet

- Electiva - CIRCUITOS SECUENCIALES EN VHDLDocument5 pagesElectiva - CIRCUITOS SECUENCIALES EN VHDLfer gutiNo ratings yet

- S1 Not (A Xor B) S2 Not D or (C and D) S S2 and (E Xor S1)Document11 pagesS1 Not (A Xor B) S2 Not D or (C and D) S S2 and (E Xor S1)oussama elkaissiNo ratings yet

- Half AdderDocument11 pagesHalf AdderTahsin RahmanNo ratings yet

- RegistruDocument2 pagesRegistruMoniNo ratings yet

- Scheme Quartus ASC Pentru Primul Subiect Poarta ŞiDocument11 pagesScheme Quartus ASC Pentru Primul Subiect Poarta ŞiAlin ChiperNo ratings yet

- CSCE 3730: Reconfigurable Logic Instructor: Prof. Saraju P. MohantyDocument9 pagesCSCE 3730: Reconfigurable Logic Instructor: Prof. Saraju P. MohantyErz SeNo ratings yet

- VHDL TD - CorrigéDocument6 pagesVHDL TD - CorrigéSahsah AbdeslamNo ratings yet

- Raisul Falah - (165060300111051) - Lab1Document11 pagesRaisul Falah - (165060300111051) - Lab1Wibi Wisnu WNo ratings yet

- T Are A Multiplex orDocument5 pagesT Are A Multiplex orROD STEVEN CARRASCO BENAVENTENo ratings yet

- VHDLDocument8 pagesVHDLROD STEVEN CARRASCO BENAVENTENo ratings yet

- LAB 1 GDocument4 pagesLAB 1 G201B076No ratings yet

- Proiectarea Flux de Date: Instrucţiunea de Atribuire Concurentă Directă de SemnalDocument15 pagesProiectarea Flux de Date: Instrucţiunea de Atribuire Concurentă Directă de SemnalCristian ConeaNo ratings yet

- VHDL ExamplesDocument23 pagesVHDL ExamplestkpradhanNo ratings yet

- Bài 1: thiết kế mạch giải mã 3 -8Document7 pagesBài 1: thiết kế mạch giải mã 3 -8Thắng TrầnNo ratings yet

- Expt 2 Demux 1 4Document3 pagesExpt 2 Demux 1 4Steven VazhappullyNo ratings yet

- hw1 PDFDocument3 pageshw1 PDFDevaraj SubrmanayamNo ratings yet

- VLSI Lab Assignment (VHDL) PRITAM PANIGRAHIDocument6 pagesVLSI Lab Assignment (VHDL) PRITAM PANIGRAHISunny TiwaryNo ratings yet

- Experiment-3: Aim: Activity1 Truth TableDocument7 pagesExperiment-3: Aim: Activity1 Truth TableHimanshu Rajan jainNo ratings yet

- Program I: To Simulate and Gate: Digital Circuits and Systems - Ii LabDocument72 pagesProgram I: To Simulate and Gate: Digital Circuits and Systems - Ii LabVarun GuptaNo ratings yet

- 8to1 Mux Using 4to1 MuxDocument5 pages8to1 Mux Using 4to1 MuxYashaswiNo ratings yet

- FPGA应用举例Document12 pagesFPGA应用举例lieshi2958100% (1)

- VlsiDocument37 pagesVlsiRitwik SoniNo ratings yet

- VHDL DemuxwhenDocument1 pageVHDL DemuxwhenMahmoud HMILANo ratings yet

- Experiment No.: 10Document5 pagesExperiment No.: 10samrudhiNo ratings yet

- 409 New Lab 2 CorrDocument9 pages409 New Lab 2 Corrhung kungNo ratings yet

- Lab Assignment 1Document8 pagesLab Assignment 1Ishrak MahmudNo ratings yet

- Code Led 7 Đo N A Chung. stt20Document6 pagesCode Led 7 Đo N A Chung. stt20Công TùngNo ratings yet

- Implemente Un Contador de 3 A 9, Si La Salida Del Contador Es Mayor Al Último Digito de Tu Código de Alumno Activa La SalidaDocument5 pagesImplemente Un Contador de 3 A 9, Si La Salida Del Contador Es Mayor Al Último Digito de Tu Código de Alumno Activa La SalidaFarromeque Eyzaguirre Luis EnriqueNo ratings yet

- Taller de Diseños de Sistemas DigitalesDocument22 pagesTaller de Diseños de Sistemas DigitalesCarlos Sánchez NietoNo ratings yet

- 1) VHDL Code To Realize All The Logic Gates: Iv Semester HDL LabDocument45 pages1) VHDL Code To Realize All The Logic Gates: Iv Semester HDL LabPamidi VishnuNo ratings yet

- Experiment-1: Simulation Result For Half Adder and Full Adder CircuitDocument7 pagesExperiment-1: Simulation Result For Half Adder and Full Adder CircuitHimanshu Rajan jainNo ratings yet

- 0 - Mec2019010 Report Assignment 2 HDM PDFDocument42 pages0 - Mec2019010 Report Assignment 2 HDM PDFShaily GargNo ratings yet

- Basic Gates ProgramDocument34 pagesBasic Gates ProgramJoychandra LoukrakpamNo ratings yet

- Digital Integrated Circuits Lab: Practical FILEDocument55 pagesDigital Integrated Circuits Lab: Practical FILELakshayNo ratings yet

- Programme No.10 AIM-To Design A D - Flip Flop CODE - Following Is The VHDL Code For Simulation of D Flip FlopDocument8 pagesProgramme No.10 AIM-To Design A D - Flip Flop CODE - Following Is The VHDL Code For Simulation of D Flip FlopAnkit GoelNo ratings yet

- Lab 1 ReportDocument7 pagesLab 1 ReportNguyễn ThắngNo ratings yet

- REPORT Assignment 2 HDMDocument36 pagesREPORT Assignment 2 HDMShaily GargNo ratings yet

- Formation VHDL FPGA Cours 1Document79 pagesFormation VHDL FPGA Cours 1LAUNo ratings yet

- Experiment No.1: AIM: Design The Following Combinational Circuits Using VHDL and Test The Circuits Using TestDocument83 pagesExperiment No.1: AIM: Design The Following Combinational Circuits Using VHDL and Test The Circuits Using Testdelinquent_abhishekNo ratings yet

- New Text DocumentDocument3 pagesNew Text DocumentNaveen NegiNo ratings yet

- Ec-452 VHDL CadDocument39 pagesEc-452 VHDL Cadkishorereddy416No ratings yet

- Correction TPDocument4 pagesCorrection TPHichem GuedriNo ratings yet

- Cad of Electronics LabDocument4 pagesCad of Electronics LabVaibhav PandeyNo ratings yet

- Final Exam - VLSI - Fall2018 - AnswerDocument6 pagesFinal Exam - VLSI - Fall2018 - Answeromar mostafaNo ratings yet

- LAB02 ReportDocument8 pagesLAB02 Report21021326 Phùng Mạnh KhangNo ratings yet

- Experiment-1 AIM: Design A Half Adder ProgramDocument10 pagesExperiment-1 AIM: Design A Half Adder Programjai_007No ratings yet

- CENG355 Final Exam Spring2019 SolutionDocument13 pagesCENG355 Final Exam Spring2019 SolutionHadi SleemNo ratings yet

- FSMDocument12 pagesFSMRohit PanwarNo ratings yet

- Two-Degree-of-Freedom Control Systems: The Youla Parameterization ApproachFrom EverandTwo-Degree-of-Freedom Control Systems: The Youla Parameterization ApproachNo ratings yet

- Dante Experiment#1Document15 pagesDante Experiment#1CHRISTIANJOIE DANTENo ratings yet

- Dante Experiment#4Document11 pagesDante Experiment#4CHRISTIANJOIE DANTENo ratings yet

- Dante Experiment#2Document8 pagesDante Experiment#2CHRISTIANJOIE DANTENo ratings yet

- Directions: Answer The Following With Solution. Box Your Final AnswerDocument2 pagesDirections: Answer The Following With Solution. Box Your Final AnswerCHRISTIANJOIE DANTENo ratings yet

- Name: Dante, Christian Joie C. Assignment#: 5 Course Code: Activity Title: Op-Amp ApplicationDocument1 pageName: Dante, Christian Joie C. Assignment#: 5 Course Code: Activity Title: Op-Amp ApplicationCHRISTIANJOIE DANTENo ratings yet

- Name: Dante, Christian Joie C. Assignment 6 Course Code: Activity Title: Op Amp Application Part 2Document2 pagesName: Dante, Christian Joie C. Assignment 6 Course Code: Activity Title: Op Amp Application Part 2CHRISTIANJOIE DANTENo ratings yet

- Dante Assignment1Document2 pagesDante Assignment1CHRISTIANJOIE DANTENo ratings yet

- Excel Series Resonant Lead-Acid Battery ChargerDocument2 pagesExcel Series Resonant Lead-Acid Battery ChargerbtiscribdNo ratings yet

- An Interview With Michael AtiyahDocument11 pagesAn Interview With Michael AtiyahXin WangNo ratings yet

- CEN 372: Transportation Engineering Lab I: Final ExaminationDocument3 pagesCEN 372: Transportation Engineering Lab I: Final ExaminationSNKNo ratings yet

- College of Engineering Architecture and Technology: Capiz State UniversityDocument3 pagesCollege of Engineering Architecture and Technology: Capiz State UniversityMilk FishNo ratings yet

- Week 1 Lecture #7 - The Control of Microbial GrowthDocument24 pagesWeek 1 Lecture #7 - The Control of Microbial GrowthNgoc PhamNo ratings yet

- Experiment 3: Study of Powder Compaction BehaviourDocument17 pagesExperiment 3: Study of Powder Compaction BehaviourBhavika TambiNo ratings yet

- Chapter 1 Two-Phase Flow and Boiling Heat TransferDocument44 pagesChapter 1 Two-Phase Flow and Boiling Heat TransferjackleesjNo ratings yet

- University of Cambridge International Examinations General Certificate of Education Advanced LevelDocument20 pagesUniversity of Cambridge International Examinations General Certificate of Education Advanced LeveltakundavsNo ratings yet

- ContinueDocument2 pagesContinuejackyNo ratings yet

- Bruker XRF SOPDocument14 pagesBruker XRF SOPsupendra phuyalNo ratings yet

- Preventive Maintenance (BJ2 - US) : Test Script SAP S/4HANA - 15-09-20Document78 pagesPreventive Maintenance (BJ2 - US) : Test Script SAP S/4HANA - 15-09-20AleksNo ratings yet

- Mechanics of Options Markets: Options, Futures, and Other Derivatives, 8th Edition, 1Document20 pagesMechanics of Options Markets: Options, Futures, and Other Derivatives, 8th Edition, 1Dinesh ChandNo ratings yet

- A Robotic Cane For Balance Maintenance AssistanceDocument12 pagesA Robotic Cane For Balance Maintenance AssistancesouravNo ratings yet

- General Diagnostic Table: Malfunction of Parts Other Than Those Listed Is Also Possible.Document2 pagesGeneral Diagnostic Table: Malfunction of Parts Other Than Those Listed Is Also Possible.miguelNo ratings yet

- DAN2400 Product BriefDocument2 pagesDAN2400 Product BriefGuy ResheffNo ratings yet

- Quaternary Science Reviews: Jerome P. Reynard, Sarah WurzDocument17 pagesQuaternary Science Reviews: Jerome P. Reynard, Sarah WurzJerome ReynardNo ratings yet

- LIT-0080 - FGD-0027 - Humidity SensorDocument2 pagesLIT-0080 - FGD-0027 - Humidity SensorErik KeupNo ratings yet

- Assembly Chapter6 BDocument4 pagesAssembly Chapter6 BMr hacksNo ratings yet

- High Precision Spectroradiometer Integrating Sphere SystemDocument11 pagesHigh Precision Spectroradiometer Integrating Sphere SystemLISUN GROUPNo ratings yet

- 770 - Rail Clamp Manual (GA-9-180KN-TR68 Ex II 2D T3)Document30 pages770 - Rail Clamp Manual (GA-9-180KN-TR68 Ex II 2D T3)j3fersonNo ratings yet

- PLC For MTEDocument9 pagesPLC For MTEMd Shahadat HossainNo ratings yet

- Equipment Auxiliary Equipment Remarks: Spare Parts Data Package (SPDP) ChecklistDocument11 pagesEquipment Auxiliary Equipment Remarks: Spare Parts Data Package (SPDP) ChecklistMohammed IlliasuddinNo ratings yet

- ISE Design Suite Software Manuals - PDF CollectionDocument14 pagesISE Design Suite Software Manuals - PDF CollectionyrikkiNo ratings yet

- 1 Procedure 10 2 Process Flow Diagram (PFD) 20 3 Workbook 30 4 Questions & Discussions 40Document11 pages1 Procedure 10 2 Process Flow Diagram (PFD) 20 3 Workbook 30 4 Questions & Discussions 40Emily SwanNo ratings yet

- Epo540 TransformerDocument72 pagesEpo540 TransformerMUHAMMAD FAHIMULLAH SOBAHUL KHAIRINo ratings yet

- Design and CFD Analysis of Centrifugal Compressor For A MicrogasturbineDocument7 pagesDesign and CFD Analysis of Centrifugal Compressor For A MicrogasturbineFurqanNo ratings yet

- Asupan Protein, Lemak, Karbohidrat Dan Lama Hari Rawat Pasien Demam Tifoid Di Rsud Dr. Moh. Soewandhie SurabayaDocument8 pagesAsupan Protein, Lemak, Karbohidrat Dan Lama Hari Rawat Pasien Demam Tifoid Di Rsud Dr. Moh. Soewandhie SurabayaAnna MardiyahNo ratings yet