Professional Documents

Culture Documents

Giai

Uploaded by

Hưng PhạmOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Giai

Uploaded by

Hưng PhạmCopyright:

Available Formats

TRƯỜNG ĐẠI HỌC BÁCH KHOA TP.HCM ĐỀ THI CUỐI KỲ 2.

2012-2013

Khoa Khoa Học và Kỹ Thuật Máy Tính Môn: Thiết kế luận lý 1

-----oOo----- Thời gian: 90 phút - Ngày: 10/06/2013

Họ và tên: ....................................................... (30 câu trắc nghiệm)

MSSV: ............................................................ Được phép sử dụng tài liệu giấy

Sinh viên làm phần TỰ LUẬN trực tiếp vào đề thi Mã đề 0001

PHẦN TRẮC NGHIỆM

Câu 1: Chọn phát biểu đúng nhất:

A. Sử dụng phương pháp bìa Karnaugh có thể cho nhiều hơn 1 kết quả tối giản

B. Sử dụng phương pháp bìa Karnaugh luôn cho kết quả tối giản

C. Sử dụng phương pháp bìa Karnaugh cho phép rút gọn biểu thức có tối đa 6 biến

D. Tất cả đều đúng

Câu 2: Sơ đồ thiết kế mạch nào sau đây thỏa mãn điều kiện fOUTPUT = fCLK/24 và Duty cycle của ngõ

xuất OUTPUT bằng 50%

U1 U2 U1 U2

74LS293 74LS293 OUTPUT 74LS293 74LS293 OUTPUT

MR1 Q3 MR1 Q3 MR1 Q3 MR1 Q3

MR2 Q2 MR2 Q2 MR2 Q2 MR2 Q2

CP0 Q1 CP0 Q1 CP0 Q1 CP0 Q1

CP1 Q0 CP1 Q0 CP1 Q0 CP1 Q0

A. B.

U1 U2 U1 U2

74LS293 74LS293 OUTPUT 74LS293 74LS293

MR1 Q3 MR1 Q3 MR1 Q3 MR1 Q3 OUTPUT

MR2 Q2 MR2 Q2 MR2 Q2 MR2 Q2

CP0 Q1 CP0 Q1 CP0 Q1 CP0 Q1

CP1 Q0 CP1 Q0 CP1 Q0 CP1 Q0

C. D.

Câu 3: Chọn bảng sự thật đúng cho sơ đồ mạch điện sau đây (NC = no change):

Mạch lật SR

Các giá trị, SET, CLEAR, Q giống NOR

Kích cạnh xuống

A. B.

C. D.

Trang 1/6 - Mã đề thi 0001

Sơ đồ mạch dưới đây sử dụng cho các câu từ 4 đến 5

5V 5V

U1 U2

74LS193 74LS193

CPU CPU

CPD CPD

PL TCU PL TCU

MR TCD MR TCD

D3 Q3 D3 Q3

D2 Q2 D2 Q2

D1 Q1 D1 Q1

D0 Q0 D0 Q0

Câu 4: . Xác định số MOD của bộ đếm:

A. 90 B. 100 C. 144 D. 160

Câu 5: . Xác định Duty cycle (mức 1) của ngõ xuất TCU của U1:

A. 95% B. 3.125 % C. 93.75 % D. Tất cả đều sai

Câu 6: Cho sơ đồ mạch đếm sau

5V

A B C D

S S S S

D Q D Q D Q D Q

_ _ _ _

CP Q CP Q CP Q CP Q

R R R R

Giả sử trạng thái ban đầu của DCBA = 0000. Xác định chuỗi 5 trạng thái kế tiếp của bộ đếm

A. 1110, 0011, 1000, 1111, 0001 B. 0001, 0010, 0011, 0100, 0101

C. 1111, 1110, 1101, 1100, 1011 D. 1110, 1101, 1011, 0111, 1110

Câu 7: Xác định biểu thức tối giản nhất của hàm F với F C.B. A C.B B. A B. A

A. B. A C.B B. A B. B. A B. A C. A (= B.A B. A C.B )

C. B. A B. A C.B D. Tất cả đều sai

Câu 8: Cho mạch phát hiện cạnh clock như hình dưới đây:

Chọn phát biểu đúng.

A. Mạch tạo ra xung thấp (LOW) khi có cạnh lên.

B. Mạch tạo ra xung cao (HIGH) khi có cạnh xuống.

C. Mạch tạo ra xung cao (HIGH) khi có cạnh lên.

D. Mạch tạo ra xung thấp (LOW) khi có cạnh xuống.

Câu 9: Giả sử ban đầu ABCD = 0000. Xác định giá trị của bộ đếm sau 10 chu kỳ clock tiếp theo:

J

S

Q

A J

S

Q

B J

S

Q

C J

S

Q

D

CP _ CP _ CP _ CP _

K Q K Q K Q K Q

R R R R

Các chân S, R của 4 Flip-Flop đều được nối lên nguồn (mức 1)

A. 1100 B. 1111 C. 0000 D. 0111

Trang 2/6 - Mã đề thi 0001

Câu 10: Cho mạch tổ hợp như hình bên dưới. Xác định điều kiện đầy đủ để LED sáng.

1

LED0

0

1

A. A=0 hoặc B=0 hoặc (B=0 và C=1) B. (A=0 hoặc B=0) và C=0

C. (A=1 và B=1) hoặc C=1 D. Tất cả đều đúng.

Câu 11: Xét các mạch Enable/Disable. Chọn phát biểu đúng:

A. Để ngõ xuất ở mức 0 khi disable, có thể sử dụng cổng OR hoặc cổng AND.

B. Khi sử dụng cổng OR, ngõ xuất ở mức 0 khi disable.

C. Khi sử dụng cổng NAND, ngõ xuất ở mức 1 khi disable.

D. Tất cả đều đúng.

Câu 12: Một mạch tổ hợp có 4 ngõ nhập (D, C, B, A) và 1 ngõ xuất (X). Ngõ xuất X=1 khi số DCBA

(D là MSB và A là LSB) là một số BCD. Ngược lại, X=0. Biểu thức đại số Bool của mạch là:

A. D C.B B. D C.B C. D C.B D. Tất cả đều đúng

Câu 13: Cho hàm F(D,C,B,A) = Σ(0, 5, 8, 10, 11, 12, 14) + d(1, 2, 11, 15) với D là MSB và A là LSB.

Biểu thức rút gọn (dạng SOP) của hàm F là:

A. C. A D.B C.B. A B. C. A D.C D.B. A C. C. A D.C C.B. A D. Cả 3 câu đều đúng

Câu 14: Chọn phát biểu đúng:

A. S-C Flip Flop có thể được dùng như 1 J-K Flip Flop. (Ngõ nhập J tương đương với S. Ngõ nhập

K tương đương với C)

B. Để hiện thực truyền dữ liệu song song, chỉ có thể sử dụng D Flip-Flop, không thể dùng J-K Flip

Flop.

C. J-K Flip Flop có thể được dùng như 1 S-C Flip Flop. (Ngõ nhập J tương đương với S. Ngõ nhập

K tương đương với C)

D. Tất cả đều đúng.

Câu 15: Cho bìa Karnaugh 4 biến như hình bên. Xác định biểu thức đại số Bool tối giản nhất:

A. D.B C.B. A C.B.A B. D.B C.B. A D.C. A

C. 2 câu A và B đều đúng D. Tất cả đều sai

Câu 16: Giả sử ban đầu AB = 00. Xác định chuỗi trạng thái của bộ đếm:

5V

S A S B Các chân S, R của 3

J Q J Q

CLK CP _ CP _ Flip-Flop đều được nối

K

R

Q K

R

Q

xuống đất (mức 0)

A. 00, 01, 10, 11 và quay lại 00 B. 00, 10, 01, 11 và quay lại 00

C. 00, 11, 01, 10 và quay lại 00 D. 00, 11, 10, 01 và quay lại 00

Trang 3/6 - Mã đề thi 0001

Câu 17: Cho một số trong hệ thống bù 2 như sau: 101101. Số thập phân tương đương là:

A. -13 B. 13 C. -18 D. -19

Câu 18: Chọn sơ đồ mạch có nguyên lý hoạt động tương ứng với bảng sự thật dưới đây:

SET CLR CLK Q

0 0 ↑ NC

0 1 ↑ 1

1 0 ↑ 0

1 1 ↑ Invalid

SET SET

Q Q

CLK CLK

CLR CLR

A. B.

SET

Q

CLK

Mạch lật SR kích cạch xuống, SET=1, CLR=0 thì Q=1 mới đúng

CLR

C. D. Cả A và C đều đúng

Câu 19: Biểu diễn số (-10) trong hệ thống bù 2 là:

A. 01010 B. 10110 C. 11010 D. 10101

Sơ đồ mạch dưới đây sử dụng cho các câu từ 20 đến 21

5V 5V 5V

Các chân J, K của 4

S A S B S C S D

J

CP

Q

_

J

CP

Q

_

J

CP

Q

_

J

CP

Q

_

Flip-Flop đều được nối lên

K

R

Q K

R

Q K

R

Q K

R

Q

nguồn (mức 1)

5V

Câu 20: . Giả sử ban đầu DCBA = 1111. Xác định chuỗi 5 trạng thái kế tiếp của bộ đếm:

A. 0010, 0011, 0100, 0101, 0110 B. 0000, 0001, 0010, 0011, 0100

C. 0010, 0011, 0010, 0011, 0010 D. 1110, 1101, 1100, 1011, 1010

Câu 21: . Giả sử ban đầu DCBA = 0111. Xác định chuỗi 5 trạng thái kế tiếp của bộ đếm:

A. 0010, 0011, 0100, 0101, 0110 B. 0010, 0011, 0010, 0011, 0010

C. 0110, 0101, 0100, 0010, 0010 D. 1000, 1001, 1010, 1011, 1100

Sơ đồ mạch dưới đây sử dụng cho các câu từ 22 đến 25

5V

S A S B S C S D

J

CP

Q

_

J

CP

Q

_

J

CP

Q

_

J

CP

Q

_

Các chân J, K của 4

K Q K Q K Q K Q 5V Flip-Flop đều được nối

R R R R

lên 5V (mức 1)

Trang 4/6 - Mã đề thi 0001

Câu 22: . Chọn phát biểu đúng về sơ đồ mạch đếm với ngõ xuất DCBA:

A. Mạch đếm lên bất đồng bộ MOD-11 B. Mạch đếm lên bất đồng bộ MOD-10

C. Mạch đếm xuống bất đồng bộ MOD-12 D. Mạch đếm xuống bất đồng bộ MOD-7

Câu 23: . Xác định Duty cycle (mức 1) cho ngõ xuất C của mạch đếm:

A. 27 % B. 33 % C. 43 % D. 50 %

Câu 24: . Giả sử các Flip-Flop có thời gian trễ tpd = 25 us. Xác định tần số tối đa của xung CLK để

mạch vẫn hoạt động đúng:

A. 5 KHz B. 10 KHz C. 40 KHz D. 25 KHz

Câu 25: . Xác định tín hiệu bị xung gai của mạch đếm:

A. Tín hiệu B B. Tín hiệu C C. Tín hiệu A D. Tín hiệu D

Sơ đồ mạch dưới đây sử dụng cho các câu từ 26 đến 30. Cho tần số tín hiệu CLK = 10 KHz

U1 U2

74LS293 74LS293

MR1 Q3 MR1 Q3

MR2 Q2 MR2 Q2

CP0 Q1 CP0 Q1

CP1 Q0 CP1 Q0

Câu 26: . Xác định số MOD của bộ đếm:

A. 36 B. 44 C. 50 D. 55

Câu 27: . Tần số của ngõ xuất Q3 của U2 là:

A. 227 Hz B. 200 Hz C. 333 Hz D. 250 Hz

Câu 28: . Tần số của ngõ xuất Q1 của U1 là:

A. 1.25 Hz B. 10 KHz C. 1 KHz D. 2.5 KHz

Câu 29: . Xác định tín hiệu bị xung gai của bộ đếm:

A. Q1 của U2 B. Q2 của U1 C. Q0 của U1 D. Q3 của U2

Câu 30: . Xác định Duty cycle (mức 1) cho ngõ xuất Q2 của U2:

A. 40% B. 36.36% C. 33.33% D. 30%

PHẦN TỰ LUẬN (1đ)

Sử dụng D Flip-Flop để thiết kế mạch đếm đồng bộ theo sơ đồ chuyển trạng thái sau (chú ý trình bày

đầy đủ các bước thiết kế - bao gồm cả sơ đồ mạch):

000

100

111 001 011

101

110 010

-----------------------------------------------

Trang 5/6 - Mã đề thi 0001

Trạng thái hiện tại Trạng thái kế tiếp

A B C A B C DA DB DC

0 0 0 0 0 1 0 0 1

0 0 1 0 1 0 0 1 0

0 1 0 1 1 0 1 1 0

0 1 1 0 0 1 0 0 1

1 0 0 1 1 1 1 1 1

1 0 1 1 1 1 1 1 1

1 1 0 1 1 1 1 1 1

1 1 1 0 0 0 0 0 0

B’C’ B’C BC BC’

A’ 0 0 0 1

A 1 1 0 1

DA = AB’ + BC’

B’C’ B’C BC BC’

A’ 0 1 0 1

A 1 1 0 1

DB = AB’ + BC’ + B’C (hoặc AC’ + B’C + BC’)

B’C’ B’C BC BC’

A’ 1 0 1 0

A 1 1 0 1

DC = AB’ + B’C’ + AC’+ A’BC

Trang 6/6 - Mã đề thi 0001

You might also like

- He-Thong-So - Tran-Ngoc-Thinh - Dapan-Dethicuoikytkll12013-0001 - (Cuuduongthancong - Com)Document6 pagesHe-Thong-So - Tran-Ngoc-Thinh - Dapan-Dethicuoikytkll12013-0001 - (Cuuduongthancong - Com)Trần Bảo PhúcNo ratings yet

- Thiet Ke Luan Ly 1 Nguyen Quang Huy Dap+an+ +de+Thi+Cuoi+Ky+Tkll1+2013+ +0003 (Cuuduongthancong - Com)Document6 pagesThiet Ke Luan Ly 1 Nguyen Quang Huy Dap+an+ +de+Thi+Cuoi+Ky+Tkll1+2013+ +0003 (Cuuduongthancong - Com)Đức Anh LêNo ratings yet

- He Thong So Tran Ngoc Thinh 2012 2013 de Thi Cuoi Hk2 Thiet Ke Luan Ly (Cuuduongthancong - Com)Document6 pagesHe Thong So Tran Ngoc Thinh 2012 2013 de Thi Cuoi Hk2 Thiet Ke Luan Ly (Cuuduongthancong - Com)Anh KhaliesNo ratings yet

- He Thong So - Tran Ngoc Thinh - de On Tap Cuoi Ky Thiet Ke Luan Ly 1Document6 pagesHe Thong So - Tran Ngoc Thinh - de On Tap Cuoi Ky Thiet Ke Luan Ly 1Nguyễn Hữu MinhNo ratings yet

- Thiet Ke Luan Ly 1 - Nguyen Quang HuyDocument3 pagesThiet Ke Luan Ly 1 - Nguyen Quang HuyHưng PhạmNo ratings yet

- Thuc Tap Kts NDKhoaDocument12 pagesThuc Tap Kts NDKhoaThuận NguyễnNo ratings yet

- Ngân hàng câu hỏi tnganh CNTTDocument9 pagesNgân hàng câu hỏi tnganh CNTTNguyễn Giản TuấnNo ratings yet

- Bai 4-BANG - TRA - LOI - TAI - PHONG - THI - NGHIEMDocument7 pagesBai 4-BANG - TRA - LOI - TAI - PHONG - THI - NGHIEMquison141No ratings yet

- Lab 5 Hệ thống số HCMUTDocument21 pagesLab 5 Hệ thống số HCMUTNhan HuynhNo ratings yet

- LAB5 in ProgressDocument17 pagesLAB5 in Progressviet.hoang3060No ratings yet

- Bai Tap DTS-KTS PDFDocument6 pagesBai Tap DTS-KTS PDFQuốc HuyNo ratings yet

- Bai 5Document45 pagesBai 5Duy NguyễnNo ratings yet

- 1 Bctsltuan 3Document21 pages1 Bctsltuan 3Đức AnhNo ratings yet

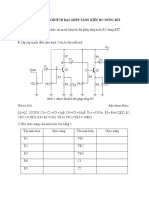

- Bài 3: Mạch Khuếch Đại Ghép Tầng Kiểu Rc Dùng Bjt I. Nhiệm vụ: Lắp ráp và khảo sát mạch khuếch đại ghép tầng kiểu RC dùng BJT. II. Yêu cầu: 1/ Lắp ráp mạch điện như hình 1 lên bo BreadboadDocument4 pagesBài 3: Mạch Khuếch Đại Ghép Tầng Kiểu Rc Dùng Bjt I. Nhiệm vụ: Lắp ráp và khảo sát mạch khuếch đại ghép tầng kiểu RC dùng BJT. II. Yêu cầu: 1/ Lắp ráp mạch điện như hình 1 lên bo BreadboadĐức Phi ĐỗNo ratings yet

- Đáp Án KTS HK2 2022 2023 - Final 14Document5 pagesĐáp Án KTS HK2 2022 2023 - Final 1422119228No ratings yet

- Thiet Ke Mach Dem Co KD 16Document26 pagesThiet Ke Mach Dem Co KD 16thevinh_thevinhNo ratings yet

- Đáp Án KTS HK2 2018-2019Document4 pagesĐáp Án KTS HK2 2018-2019Cường Thái ViệtNo ratings yet

- An - Nguyentruongthien 1510019Document55 pagesAn - Nguyentruongthien 1510019Nguyễn Trường Thiên AnNo ratings yet

- Giai Bai Tap Chuong 3 - Bai 13-15Document4 pagesGiai Bai Tap Chuong 3 - Bai 13-15Minh NguyễnNo ratings yet

- Lab06dt LabDocument3 pagesLab06dt LabPhú Hà LêNo ratings yet

- Bao Cao TopicDocument17 pagesBao Cao TopicLương Công Hân67% (3)

- Bài 5: Mạch Khuếch Đại CôngDocument8 pagesBài 5: Mạch Khuếch Đại Cônghaipro2010No ratings yet

- Chương 3 - Giang - Lab 3Document37 pagesChương 3 - Giang - Lab 321161251No ratings yet

- DapanTCKI 14 15 De2Document5 pagesDapanTCKI 14 15 De2Thế PhúcNo ratings yet

- TN LTM 2Document14 pagesTN LTM 2Nguyễn Tùng AnhNo ratings yet

- ĐÁP ÁN KHÍ CỤ ĐIỆN CQ1-22Document3 pagesĐÁP ÁN KHÍ CỤ ĐIỆN CQ1-22Huynh Cong HieuNo ratings yet

- Giai BaiTap Tuan 12Document23 pagesGiai BaiTap Tuan 12Thương NguyễnNo ratings yet

- báo cáo bài tập lớn mạch buck converterDocument37 pagesbáo cáo bài tập lớn mạch buck converterTrần TuấnNo ratings yet

- Báo Cáo TN VLBDDocument52 pagesBáo Cáo TN VLBDTuan MinhNo ratings yet

- VLBD Nhóm 3 1Document42 pagesVLBD Nhóm 3 1Kiệt NgôNo ratings yet

- Dinh Duc Anh-21161391 - Bao Cao TT Truyen So Lieu Tuan 4 (1111)Document12 pagesDinh Duc Anh-21161391 - Bao Cao TT Truyen So Lieu Tuan 4 (1111)Đức AnhNo ratings yet

- Đap An KTDĐT de 1B - HK1 - 2016 - 2017 - 02 2Document8 pagesĐap An KTDĐT de 1B - HK1 - 2016 - 2017 - 02 2Trung Võ Lê MinhNo ratings yet

- Dien Tu Cong Suat CH VIII Dieu Khien Va Bao VeDocument18 pagesDien Tu Cong Suat CH VIII Dieu Khien Va Bao VeĐỗ Nhật MinhNo ratings yet

- Lab06dt LabDocument4 pagesLab06dt LabVõ Trọng ThứcNo ratings yet

- UntitledDocument4 pagesUntitledLâm Đức ChánhNo ratings yet

- BÀI TN 1 VDocument8 pagesBÀI TN 1 VNguyễn Thanh TúNo ratings yet

- Báo Cáo Đ Án 1 Nhóm 6Document19 pagesBáo Cáo Đ Án 1 Nhóm 6Minh Lương ThịNo ratings yet

- Đề 100 Câu Xác Suất Cao Số 29Document9 pagesĐề 100 Câu Xác Suất Cao Số 29hw8ghftqngNo ratings yet

- 2018-2019 Finalterm2Document11 pages2018-2019 Finalterm2Gia Linh PhamNo ratings yet

- Chương 1: Nguyên Lí Hoạt Động Của Hệ Thống Vi Điều KhiểnDocument34 pagesChương 1: Nguyên Lí Hoạt Động Của Hệ Thống Vi Điều KhiểnHùng HoàngNo ratings yet

- De Thi Giua HK1 Cong Nghe 12 Nam 2022 2023 de 1Document5 pagesDe Thi Giua HK1 Cong Nghe 12 Nam 2022 2023 de 1tranthiphuonganh.10022005No ratings yet

- tuhoc365.vn DẠNG 2 - Ghép tụ điện chưa tích điện trước chương 1 lớp 11Document27 pagestuhoc365.vn DẠNG 2 - Ghép tụ điện chưa tích điện trước chương 1 lớp 11Đinh Duy SớmNo ratings yet

- Bài báo cáo môn KTS - CLC - đề tài Mod 20- Mod 50; Reset Mod20 (Kỹ Thuật Số)Document20 pagesBài báo cáo môn KTS - CLC - đề tài Mod 20- Mod 50; Reset Mod20 (Kỹ Thuật Số)Huy Ngô PhùngNo ratings yet

- CBDocument11 pagesCBHa Phuong TamNo ratings yet

- Chương 4Document18 pagesChương 4Nguyễn HùngNo ratings yet

- Chương 4 InstructionDocument21 pagesChương 4 Instruction21161251No ratings yet

- ĐỀ THI + ĐÁP ÁN LẦN 2 KTX-S CĐ Đ-ĐT 11A,B,C,D,EDocument4 pagesĐỀ THI + ĐÁP ÁN LẦN 2 KTX-S CĐ Đ-ĐT 11A,B,C,D,EVü PhämNo ratings yet

- Da Digi330163 KtsDocument6 pagesDa Digi330163 KtsThương NguyễnNo ratings yet

- BTL Dong Ho So Dung 7490Document11 pagesBTL Dong Ho So Dung 7490duonghungbg1No ratings yet

- Ky Thuat So Co BanDocument30 pagesKy Thuat So Co BanTrần ThắngNo ratings yet