Professional Documents

Culture Documents

Previ 3 Sistemes

Uploaded by

nuriabruch12Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Previ 3 Sistemes

Uploaded by

nuriabruch12Copyright:

Available Formats

Universitat Politècnica de Catalunya

Departament d’Enginueria Minera, Industrial i TIC

Estudi previ 3:

Introducció als sistemes

seqüencials

Autora: Núria Bruch Mas

Titulació: Grau en Enginyeria de Sistemes TIC

Assignatura: Introducció als sistemes digitals

Curs: Curs 2023-24

Grup: Grup 10, Grup 12 de pràctiques

Data de realització: 13 de novembre del 2023

Data d’entrega: 14 de novembre del 2023

1 Tasca 1: Biestable SET/RESET

El biestable més senzill és l’anomenat biestable Set/Reset. Una implementació d’a-

quest biestable amb portes NAND és la següent:

Amb un integrat 7400, construı̈u al laboratori aquest biestable. Verifiqueu el seu

funcionament posant LEDs a les sortides Q i Q̄.

Suggeriment: Feu servir les NANDs corresponents als pins 8-13. Aquest muntatge

s’aprofitarà en els experiments que venen a continuació. Tingueu cura de que el

muntatge sigui el més clar possible i eviteu cables massa llargs.

(13/11/2023) Estudi previ 3: Introducció als sistemes seqüencials - N.Bruch pàg.1 de 10

Si tenim en compte la taula de la veritat corresponent al biestable SET/RESET:

Entrades Sortides

S R Q Q̄

1 1 no varia no varia

0 1 1 0

1 0 0 1

0 0 no vàlid no vàlid

• Si S=0 i R=0; Qt =La sortida es mantindrà igual que l’estat en què es trobava

l’entrada

• Si S=0 i R=1; Qt+1 = 1 (SET)

• Si S=1 i R=0; Qt+1 = 0 (RESET)

• Si les dues entrades son 0, el resultat no serà vàlid, tot i que en el circuit

s’il·luminaran els dos LEDs.

La taula de la veritat NAND ens permetrà comprendre quina serà la sortida si

introduı̈m certs valors en les entrades:

A B Y

0 0 1

1 0 1

0 1 1

1 1 0

(13/11/2023) Estudi previ 3: Introducció als sistemes seqüencials - N.Bruch pàg.2 de 10

1.1 Simulació del biestable SET/RESET

A continuació es mostren les simulacions que s’han realitzat, tenint en compte que

el LED de l’esquerra es el que representa Q, i el de la dreta Q̄. A més a més,

l’interruptor 1 representa l’entrada SET i el 2 l’entrada RESET.

1.1.1 Si S=1 i R=0

Figura 1: En aquesta figura podem veure com, si les entrades son 1 i 0, s’il·lumina

Q̄.

1.1.2 Si S=0 i R=1

Figura 2: En aquesta figura podem veure com, si les entrades son 0 i 1, s’il·lumina

Q.

(13/11/2023) Estudi previ 3: Introducció als sistemes seqüencials - N.Bruch pàg.3 de 10

1.1.3 Si S=1 i R=1

Figura 3: En aquesta figura podem veure com, si les entrades son 1 i 1, la sortida

es manté exactament igual que l’anterior, és a dir, es segueix il·luminant Q.

1.1.4 Si S=0 i R=0

Figura 4: En aquesta figura podem veure com, si les entrades son 0 i 0, s’il·luminen

els dos LEDs.

(13/11/2023) Estudi previ 3: Introducció als sistemes seqüencials - N.Bruch pàg.4 de 10

2 Previ 1: Study on the D-type Flip-Flop with

Enable.

La tipologia de flip-flop D amb Enable és un circuit seqüencial a la electrònica

digital. En aquest cas, està principalment compost per portes NAND i, a més,

integra el flip-flop SET-RESET que vam definir anteriorment. No obstant això, és

capaç de controlar el valor de les seves sortides independentment de les entrades.

Això s’aconsegueix amb l’entrada Enable (E). Bàsicament, determina si els canvis a

la entrada de dades (D) haurien de afectar la sortida del flip-flop (Q). L’Enable té

dos possibles estats diferents:

• Active state:

En aquest cas, el circuit funciona de manera normal, i la entrada de dades

té un efecte directe sobre la sortida Q. Si analitzem el circuit en aquestes

circumstàncies, el valor de D sempre correspon al valor de Q. Per tant, si D

canvia, Q es actualitzarà segons el nou valor de D.

• Inactive state:

En aquest estat, impedeix que els canvis a l’entrada (D) afectin les sortides.

És a dir, en aquest cas, si la entrada a D canvia, la sortida a Q romandrà la

mateixa que inicialment.

En altres paraules, la entrada E actua com un interruptor que ”decideix”si el circuit

executarà les seves sortides en funció de les entrades proporcionades.

A continuació es mostra el diagrama de temporització corresponent:

(13/11/2023) Estudi previ 3: Introducció als sistemes seqüencials - N.Bruch pàg.5 de 10

Com es pot veure, Q es representa com una funció tant de D com de E. Quan E està

inactiu, significa que Q mostra l’entrada anterior a D, les dades més recents que E

permet çonèixer”sobre Q, però no les dades actuals. Quan E està actiu, el diagrama

de temporització de Q és idèntic al de D.

Aquest és un exemple que il·lustra el funcionament d’aquest circuit:

Primerament, suposem que l’habilitació està activa i, per tant, el circuit està funci-

onant normalment; D = 1 i E = 1. Segons la taula de veritat de la porta NAND,

realitzant operacions lògiques amb les entrades de cada porta, podem observar com

el valor de la entrada D es correspon amb el valor de la sortida Q.

(13/11/2023) Estudi previ 3: Introducció als sistemes seqüencials - N.Bruch pàg.6 de 10

Quan el valor de D canvia, donat que E=1, el valor de Q també canvia en conse-

cuència:

No obstant això, si el valor de E esdevé 0, cosa que significa que està en un estat

inactiu, el valor de Q ja no correspondrà al valor de D i mostrarà l’última sortida

que tenia, en aquest cas, 0.

Indeed, Q and its complement, Q̄, will always be complementary to each other.

(13/11/2023) Estudi previ 3: Introducció als sistemes seqüencials - N.Bruch pàg.7 de 10

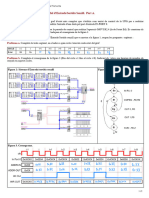

3 Previ 2: D-type flip-flop triggered by edge

Feu un estudi detallat del funcionament d’aquest circuit. Novament, feu una des-

cripció amb paraules recolzada amb un cronograma que mostri exactament el que

voleu transmetre.

Aquest circuit seqüencial funcionarà de manera molt semblant als que s’han mostrat

anteriorment. L’única diferència és que, aquesta vegada, l’actualització de les dades

per a les sortides (Q i Q̄) es desencadenarà pel canvi de flanc, és a dir, pel canvi

d’estat. Aixı́, podrı́em dir que el que el caracteritza és que el canvi d’estat està

determinat pel flanc del rellotge. No obstant això, cada circuit es configurarà per

especificar si l’actualització de les dades (canvi del flip-flop) es produirà en els flancs

de pujada o de baixada.

a) El canvi del flip-flop es produirà en els flancs de pujada.

b) El canvi del flip-flop es produirà en els flancs de baixada.

(13/11/2023) Estudi previ 3: Introducció als sistemes seqüencials - N.Bruch pàg.8 de 10

Here goes the corresponding timing diagram:

Aquest horari opera depenent dels flancs de pujada. Per tant, podem veure com hi

ha constantment diferents entrades a la entrada de dades (D), però aquestes només

es poden percebre quan el rellotge ho permet, concretament, quan la transició del

flanc és de pujada (de 0 a 1). Per entendre-ho millor, analitzem un fragment especı́fic

de l’horari:

Les lı́nies blaves indiquen el moment en què l’estat canvia de 0 a 1. A partir d’aquı́,

podem veure com la sortida Q pren el valor de la D actual, però només en aquest

moment especı́fic.

(13/11/2023) Estudi previ 3: Introducció als sistemes seqüencials - N.Bruch pàg.9 de 10

4 Previ 3: Type 7474 flip-flops.

Feu una ullada al datasheet d’aquest integrat i intenteu comprendre el seu funciona-

ment. (no cal que escriviu res en particular).

1. Entrades:

· D (Dades): Aquesta és la entrada de dades que s’introdueix al flip-flop.

· CLK (Rellotge): Els canvis en el flip-flop es produeixen segons els flancs de

pujada i baixada d’aquest senyal.

2. Sortides:

· Q: És la principal sortida del flip-flop, que representa l’estat actual o l’última

actualització en el flip-flop.

· Q̄: És la sortida complementària de Q.

3. Com funciona?

El flip-flop 7474 és actiu tant en els flancs de pujada com en els de baixada.

Aixı́, quan es produeix un canvi d’estat, es reflecteix en Q. Si D és 1 en aquell

moment, Q romandrà a 1 fins al pròxim canvi d’estat. El mateix s’aplica per

a 0.

4. Entrades SET i RESET:

Aquestes s’utilitzen bàsicament per establir (S) o restablir manualment (R)

l’estat del flip-flop, independentment de la entrada de dades (D). Quan s’activa

la entrada S, la sortida Q s’estableix a l’estat 1, i quan s’activa la entrada R,

(13/11/2023) Estudi previ 3: Introducció als sistemes seqüencials - N.Bruch pàg.10 de 10

la sortida Q es restableix a l’estat 0. Aquestes entrades poden ser útils per

forçar un estat especı́fic al flip-flop.

5 Previ 4: Type 7474 flip-flops.

Un sistema d’alarma elemental consta de a) un sensor i b) una central. En la ver-

sió més senzilla, l’alarma s’activaria de manera permanent quan un sensor es posa

en marxa. L’activació d’un sensor significa que emet una senyal lògica alta durant

un temps indeterminat (des de uns pocs milisegons fins a desenes de segons) mentre

dura la condició de disparo de l’alarma. Fent ús d’un 74HCT74, dissenyeu un circuit

que mantingui indefinidament encès un LED quan rep un impuls positiu de durada

indeterminada. Proporcioneu-li també un mecanisme per aturar manualment l’alar-

ma.

Inputs Outputs

S R Q Q̄

1 1 no varia no varia

0 1 1 0

1 0 0 1

0 0 no vàlid no vàlid

(13/11/2023) Estudi previ 3: Introducció als sistemes seqüencials - N.Bruch pàg.11 de 10

Figura 5: If R=1 and S=0

Figura 6: If R=1 and S=1

Figura 7: If R=0 and S=1

(13/11/2023) Estudi previ 3: Introducció als sistemes seqüencials - N.Bruch pàg.12 de 10

You might also like

- Introducció de Sistemes Previ 4bDocument5 pagesIntroducció de Sistemes Previ 4bjohnmendoza0725No ratings yet

- Problemes Dexamen de DS PDFDocument116 pagesProblemes Dexamen de DS PDFToni HinojoNo ratings yet

- Totxaco PràctikeDocument296 pagesTotxaco PràctikeJan Masferrer TriusNo ratings yet

- DDB Tema 6 - 2023-2024 EETbisDocument35 pagesDDB Tema 6 - 2023-2024 EETbisJULIA ARCASNo ratings yet

- DOSSIER 4rT ESO-TECNOLOGIA-2017-2018-UNITAT 4 - ELECTRÒNICA DIGITALDocument13 pagesDOSSIER 4rT ESO-TECNOLOGIA-2017-2018-UNITAT 4 - ELECTRÒNICA DIGITALRida Eddellah MohamedNo ratings yet

- ExamenesJuntos FisicaDocument344 pagesExamenesJuntos FisicaWillyRodríguezBarceloNo ratings yet

- Practica 3 ELDI 22TDocument9 pagesPractica 3 ELDI 22TZakaria Moussaoui HajjiNo ratings yet

- Pràctica 1 - Pèndol Simple - T12 PDFDocument7 pagesPràctica 1 - Pèndol Simple - T12 PDFJulie RileyNo ratings yet

- Pràctica 1-1Document38 pagesPràctica 1-1Sergi RosadoNo ratings yet

- Practica 4 AutoDocument7 pagesPractica 4 AutoKelly Oropeza IbarraNo ratings yet

- DAVID MARTÍ ÁLVAREZ - 4929473 - Assignsubmission - File - Informe3Document8 pagesDAVID MARTÍ ÁLVAREZ - 4929473 - Assignsubmission - File - Informe3Laurentiu CristeaNo ratings yet

- STI - PAG ResoltDocument10 pagesSTI - PAG ResoltFalcon NeyJiNo ratings yet

- PAC2SOL v5Document20 pagesPAC2SOL v5Antonio Hernando MañeruNo ratings yet

- Preguntes ConceptualsDocument13 pagesPreguntes ConceptualsCristina Gil-Penna AlierNo ratings yet

- Final Analogica 2017Document2 pagesFinal Analogica 2017jose.martinez.garciaNo ratings yet

- 6 Sintonia 2021Document10 pages6 Sintonia 2021renata guerreiroNo ratings yet

- Obs R 0Document4 pagesObs R 0Erick GarciaNo ratings yet

- Estudi-Previ-1b Dispositivos ElectronicosDocument9 pagesEstudi-Previ-1b Dispositivos ElectronicosLolelo1234567890No ratings yet

- 5 Realimentacio 2021Document8 pages5 Realimentacio 2021renata guerreiroNo ratings yet

- Pràctica 1 AmplificacióDocument5 pagesPràctica 1 AmplificacióMeritxell Galletto CarnerNo ratings yet

- InformeDocument8 pagesInformeMiriam Pedrera GomezNo ratings yet

- EE02904CDocument49 pagesEE02904CAlejandro XulucNo ratings yet

- Tema2 1Document58 pagesTema2 1Hanan AmarkiNo ratings yet

- GuillemCarrasco - ArnauSirvent - PreviaPractica4 - Configuració Inversora - CaracteritzacióDocument12 pagesGuillemCarrasco - ArnauSirvent - PreviaPractica4 - Configuració Inversora - CaracteritzacióGuillem CarrascoNo ratings yet

- 02 - Conceptes HardwareDocument10 pages02 - Conceptes HardwarePablo AlgarateNo ratings yet

- P3 Rega EebeDocument8 pagesP3 Rega Eebearnau.gonzalez.almirallNo ratings yet

- Solució Examen SR 2021Document6 pagesSolució Examen SR 2021Fineas GrozaNo ratings yet

- Pràctica 2 ComparadorsDocument5 pagesPràctica 2 ComparadorsMeritxell Galletto CarnerNo ratings yet

- Pràctica 3: Caracterització Elèctrica Famílies LògiquesDocument8 pagesPràctica 3: Caracterització Elèctrica Famílies LògiquesLaurentiu CristeaNo ratings yet

- #L86Ttr: Laboratori Control AutomatttzaciilindustrialDocument4 pages#L86Ttr: Laboratori Control Automatttzaciilindustrialrenata guerreiroNo ratings yet

- La Biblia 2 SimulacioDocument17 pagesLa Biblia 2 SimulacioJoel medina jimenezNo ratings yet

- Practica 5 (Resultats) - 2020-21 - Q2Document20 pagesPractica 5 (Resultats) - 2020-21 - Q2DanisWarsNo ratings yet

- Projecte 2: Elaboració I Programació D'una BarreraDocument11 pagesProjecte 2: Elaboració I Programació D'una BarreraPablo Alonso BarberoNo ratings yet

- F2 Tema3 Feines Sol 3 Circuits RCDocument13 pagesF2 Tema3 Feines Sol 3 Circuits RCpaula.tong.ferrerNo ratings yet

- PRÀCTICA 4 Ultrasò Roger V.Document18 pagesPRÀCTICA 4 Ultrasò Roger V.Roger vinyolesNo ratings yet

- Circuit LògicDocument7 pagesCircuit LògicAriadna CuberoNo ratings yet

- Control de Sistemes Pràctica 3 - Linialització: Abstract-En Aquest Informe Es Realitzaran Un Seguit deDocument6 pagesControl de Sistemes Pràctica 3 - Linialització: Abstract-En Aquest Informe Es Realitzaran Un Seguit deRoger Jimenez MayoralNo ratings yet

- Pràctica 2 - Pèndol Simple - T13 - v4Document7 pagesPràctica 2 - Pèndol Simple - T13 - v4Ibrahim NadorNo ratings yet

- Guia de La Pràctica 1 CIIA v23 - 2Document17 pagesGuia de La Pràctica 1 CIIA v23 - 2ruben.ruiz.ruizNo ratings yet

- Pràctica Iv PÈNDOL DE POHL: Oscil Lacions Esmorteïdes I ForçadesDocument6 pagesPràctica Iv PÈNDOL DE POHL: Oscil Lacions Esmorteïdes I Forçadesasunaa.love.kiritoNo ratings yet

- Informe de Pràctiques: Pràctica 2. Càrrega I Descàrrega Del CondensadorDocument13 pagesInforme de Pràctiques: Pràctica 2. Càrrega I Descàrrega Del CondensadorBf BNo ratings yet

- Visualització de Un Sistema de Control en LabViewDocument4 pagesVisualització de Un Sistema de Control en LabViewtonala gamesNo ratings yet

- Problemes de Circuits LògicsDocument2 pagesProblemes de Circuits LògicssolercruanyesNo ratings yet

- Sessió 2 Tecnologies ComplementariesDocument8 pagesSessió 2 Tecnologies Complementariesnuriabruch12No ratings yet

- Problemes Tema - 6 - MOSFET - SOLUCIODocument5 pagesProblemes Tema - 6 - MOSFET - SOLUCIOFerney ChavesNo ratings yet

- Wuolah Free Primer Questionari AvaluableDocument4 pagesWuolah Free Primer Questionari AvaluablelmkpkzfncmljazntmcNo ratings yet

- Meteorologia DinàmicaDocument31 pagesMeteorologia Dinàmicasipira100% (1)

- EE02902CDocument19 pagesEE02902CAlejandro XulucNo ratings yet

- P4. Circuits Amb n-MOSFETDocument3 pagesP4. Circuits Amb n-MOSFEThdhudra19No ratings yet

- 15 Enero 2021Document10 pages15 Enero 2021Cristian DazaNo ratings yet

- 15 Enero 2021Document10 pages15 Enero 2021Cristian DazaNo ratings yet

- Ac1 Catalina AlemanyDocument5 pagesAc1 Catalina AlemanyCatalina Alemany RoserNo ratings yet

- ET8a 09 10 Q1 ElectronicDocument7 pagesET8a 09 10 Q1 Electronicrc7pablorNo ratings yet

- Punt de Control S2 2016-17 SolucionatDocument3 pagesPunt de Control S2 2016-17 SolucionatCarlos ValdiviaNo ratings yet

- Pèndol SimpleDocument13 pagesPèndol Simpledse3 dse3No ratings yet

- Coleccion de Problemas Juliol 2013Document60 pagesColeccion de Problemas Juliol 2013Catalina LlabresNo ratings yet

- I Out 0Document263 pagesI Out 0Shanon Nicole Mogro CastilloNo ratings yet

- Practica1 PDFDocument6 pagesPractica1 PDFJulie RileyNo ratings yet