Professional Documents

Culture Documents

Bai Giang MDT - Chuong 3 - 03 - 2022

Bai Giang MDT - Chuong 3 - 03 - 2022

Uploaded by

Phat HuynhOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Bai Giang MDT - Chuong 3 - 03 - 2022

Bai Giang MDT - Chuong 3 - 03 - 2022

Uploaded by

Phat HuynhCopyright:

Available Formats

Chương 3.

Phân tích mạch khuếch đại tín hiệu nhỏ tần số thấp dùng FET

Chương 3.

PHÂN TÍCH MẠCH KHUẾCH ĐẠI TÍN HIỆU

NHỎ TẦN SỐ THẤP CỦA FET

Mục tiêu:

- Tính toán được phân cực DC cho các dạng mạch khếch đại cơ bản

- Vẽ được mạch tương đương tín hiệu nhỏ tần số thấp cho 3 dạng mạch khuếch đại

cơ bản là S chung, G chung và D chung.

- Thiết lập được phương trình toán học mô tả hệ số khuếch đại dòng và áp của mạch

điện.

- Tính toán được trở kháng vào và ra của mạch

Yêu cầu: Sinh viên ôn tập kiến thức về

- Đặc tính linh kiện FET

Nội dung: Trang

3.1. Phân cực DC và ỗn định phân cực cho mạch khuếch đại FET .................................. 2

3.2. Phân tích mạch khếch đại tín hiệu nhỏ tần số thấp của FET...................................... 6

Biên soạn: TS. Bùi Thư Cao 1

Chương 3. Phân tích mạch khuếch đại tín hiệu nhỏ tần số thấp dùng FET

3.1. Phân cực DC và ỗn định phân cực cho mạch khuếch đại FET

3.1.1. Ký hiệu và phân loại transistor hiệu ứng trường FET (Field Effect Transistor)

Có 2 loại transistor hiệu ứng trường phổ dụng là JFET (Junction FET) và MOSFET (Metal

Oxide Semiconductor FET). JFET sủ dụng điện cực kim loại nối trực tiếp với vật liệu bán

dẫn còn MOSFET dung điện cực là lớp Oxide Silic cách điện. Với MOSFET thì phổ dụng

nhất hiện nay là loại eMOSFET (enhancement MOSFET) với khả năng nhiểu nội thấp, trỏ

kháng vào cao và độ ỗn định nhiệt tốt hơn nhiều so với BJT.

Hình 3. 1. Cấu tạo JFET kênh N Hình 3. 2. Cấu tạo của JFET kênh P

Q1 Q2

2N3821 2N2608

Hình 3. 3. Ký hiệu của JFET kênh N Hình 3. 4. Ký hiệu của JFET kênh P

Hình 3. 5. Cấu tạo eMOSFET kênh N Hình 3. 6. Cấu tạo của eMOSFET kênh P

Q3 Q4

IRF510 3LP01C-TB-E

Hình 3. 7. Ký hiệu eMOSFET kênh N Hình 3. 8. Ký hiệu của eMOSFET kênh P

3.1.2. Đặc tuyến volt-ampre của FET

a) Junction FET

Với transistor hiệu ứng trường JFET, để khảo sát đặc tính tần số người ta phân cực trực tiếp

cho transistor như Hình 3.9. Khi đó ta thu được dạng đặc tuyến như Hình 3.10.

Mô tả toán học cho hàm phân cực của JFET tại vùng bảo hòa với các điều kiện sauu:

Biên soạn: TS. Bùi Thư Cao 2

Chương 3. Phân tích mạch khuếch đại tín hiệu nhỏ tần số thấp dùng FET

𝑣𝐺𝑆 2

𝑖𝐷 = 𝐼𝐷𝑆𝑆 [1 + ] (1)

𝑉𝑃

|𝑣𝐺𝑆 | < 𝑉𝑃

Với, {

𝑉𝑃 − |𝑣𝐺𝑆 | < 𝑣𝐷𝑆 < 𝑉𝐵𝑟𝑒𝑎𝑘𝑑𝑜𝑤𝑛

Trong đó VP là giá trị điện áp nghẽn đặt vào 𝑣𝐷𝑆 , tại 𝑣𝐺𝑆 = 0, sao cho IDS = 0. IDSS (Drain-

source saturation current) là dòng IDS bảo hòa cho FET, tại 𝑣𝐺𝑆 = 0 V.

Hình 3. 9. Mạch phân cực cho JFET

kênh N

Hình 3. 10. Đặc tuyến Volt-ampere của JFET kênh N

b) Enhancement MOSFET

Với transistor hiệu ứng trường eMOSFET, để khảo sát đặc tính tần số người ta phân cực

trực tiếp cho transistor như Hình 3.10, với điện áp phân cực VGS và VDS dương. Khi đó ta

thu được dạng đặc tuyến như Hình 3.11. Mô tả toán học cho hàm phân cực của MOSFET

trong vùng bảo hòa là,

Hình 3. 11. Mạch phân cực cho

eMOSFET kênh N Hình 3. 12. Đặc tuyến Volt-ampere của eMOSFET kênh N

𝑖𝐷 = 𝑘 [𝑣𝐺𝑆 − 𝑉𝑇 ]2 (2)

𝑣𝐺𝑆 > 𝑉𝑇

Với, {

𝑣𝐺𝑆 − 𝑉𝑇 < 𝑣𝐷𝑆 < 𝑉𝐵𝑟𝑒𝑎𝑘𝑑𝑜𝑤𝑛

Biên soạn: TS. Bùi Thư Cao 3

Chương 3. Phân tích mạch khuếch đại tín hiệu nhỏ tần số thấp dùng FET

Trong đó VT là giá trị điện áp nghưỡng và k là hằng số phụ thuộc vào cấu trúc vật liệu, bề

𝐴

dày và chiều dài của kênh dẫn (10−4 ÷ 10−3 2 ). Vậy 𝑣𝐺𝑆 = 0 là giá trị áp phân cực nhỏ

𝑉

nhất cho eMOSFET.

3.1.3. Phân cực tĩnh (phân cực DC) cho FET

a) Phân cực DC cho JFET

VDD

Cho mạch phân cực DC cho JFET như

Hình vẽ, với VDD = +20V, R1 = 3KΩ, R2

R3

= 1KΩ, R3 = 2KΩ, IDSS = 2mA và Vp= 4V.

Tính phân cực DC cho mạch

Q1

R1

R2

Hình 3. 13. Mạch phân cực cho JFET

Biên soạn: TS. Bùi Thư Cao 4

Chương 3. Phân tích mạch khuếch đại tín hiệu nhỏ tần số thấp dùng FET

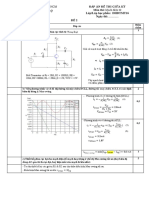

b) Phân cực DC cho MOSFET

Cho mạch phân cực DC cho MOSFET như

Hình vẽ, với VDD = +12V, R1 = 3KΩ, R2

= 8KΩ, RS = RD = 1KΩ, k = 3 × 10−4 𝐴/𝑉 2

và VT = 3V. Tính phân cực DC cho mạch.

Hình 3. 14. Mạch phân cực cho MOSFET

Biên soạn: TS. Bùi Thư Cao 5

Chương 3. Phân tích mạch khuếch đại tín hiệu nhỏ tần số thấp dùng FET

3.2. Phân tích mạch khếch đại tín hiệu nhỏ tần số thấp của FET.

3.2.1. Mạch tương đương tín hiệu nhỏ tần số thấp

Trong đó,

1

- 𝑔𝑚 là trở dẫn (khoảng vài mili )

𝛺

- 𝑐𝑔𝑠 là giá trị cảm kháng ngỏ vào

Hình 3. 15. Mạch tương đương AC tín hiệu nhỏ của FET (vài chục pF)

- 𝑐𝑔𝑑 là giá trị cảm kháng ngỏ vào

(0.1pF - vài pF)

- 𝑐𝑑𝑠 là giá trị cảm kháng ngỏ ra

(vài chục pF)

- 𝑟𝑑𝑠 là giá trị trở kháng ngỏ vào

Hình 3. 16. Mạch tương đương tín hiệu nhỏ, tần số thấp (vài chục KΩ đến vài trăm KΩ)

của FET 𝜕𝑖𝐷

- 𝑔𝑚 = | (1/𝛺)

𝜕𝑣𝐺𝑆 𝑉

𝐷𝑆𝑄

- 𝜇 = 𝑔𝑚 𝑟𝑑𝑠 (1/𝛺)

𝜕𝑣𝐷𝑆

- 𝑟𝑑𝑠 = | (Ω)

𝜕𝑖𝐷 𝑉

𝐺𝑆𝑄

Hình 3. 17. Mạch tương đương tín hiệu nhỏ, tần số thấp

của FET

3.2.2. Phân tích mạch khuếch đại tín hiệu nhỏ của FET cấu hình CS (Common Source)

Bài toán 1: Mạch khếch đại CS dùng JFET

Cho mạch điện như hình bên. Biết JFET

có IDSS = 2mA, VP = 4V. Nguồn có nội

trở là Ri = 50Ω, VDD = 12V. Xem các tụ

là bypass ở tần số làm việc. Chọn điểm

làm việc tại áp phân cực VGS = -3V. Tải

RL = RD = 1KΩ.

a) Thiết kế phân cực cho FET.

b) Tính Av, trở kháng vào và ra của

mạch khuếch đại.

Hình 3. 18. Mạch khuếch đại JFET cấu hình CS

Biên soạn: TS. Bùi Thư Cao 6

Chương 3. Phân tích mạch khuếch đại tín hiệu nhỏ tần số thấp dùng FET

Biên soạn: TS. Bùi Thư Cao 7

Chương 3. Phân tích mạch khuếch đại tín hiệu nhỏ tần số thấp dùng FET

Bài toán 2: Mạch khếch đại CS cho MOSFET

Cho mạch điện như hình bên. Biết

𝐴

MOSFET có k = 3 × 10−4 2 , VT =

𝑉

4V. Nguồn có nội trở là Ri = 50Ω, VDD

= 9V. Xem các tụ là bypass ở tần số

làm việc. Chọn điểm làm việc tại áp

phân cực VGS = 6V. Tải RL = RD =

1KΩ.

a) Thiết kế phân cực cho FET.

b) Tính Av, trợ kháng vào và ra

của mạch khuếch đại.

Hình 3. 19. Mạch khuếch đại MOSFET cấu hình CS

Biên soạn: TS. Bùi Thư Cao 8

Chương 3. Phân tích mạch khuếch đại tín hiệu nhỏ tần số thấp dùng FET

3.2.3. Phân tích mạch khuếch đại tín hiệu nhỏ của FET cấu hình CD (Common Drain)

hay còn được gọi là FS (Following Source)

Bài toán: Mạch khếch đại FS dùng MOSFET

Cho mạch điện như hình bên. Biết

MOSFET có gm = 1/500 (1/Ω). Nguồn

có nội trở là Ri = 50Ω, R1 = R2 = RS

=RL= 1KΩ, rds = 30KΩ. Xem các tụ là

bypass ở tần số làm việc, và mạch đã

được phân cực DC trong vùng bão hòa.

a) Tính Av, trở kháng vào và ra của

mạch khuếch đại.

Hình 3. 20. Mạch khuếch đại JFET cấu hình CS

Biên soạn: TS. Bùi Thư Cao 9

Chương 3. Phân tích mạch khuếch đại tín hiệu nhỏ tần số thấp dùng FET

3.2.4. Phân tích mạch khuếch đại tín hiệu nhỏ của FET cấu hình CG (Common Gate)

Bài toán: Mạch khếch đại CG dùng MOSFET

Cho mạch điện như hình bên. Biết

MOSFET có gm = 1/500(1/Ω) Nguồn

có nội trở là Ri = 50Ω, R1 = R2 = RS

=RL= 1KΩ, rds = 20KΩ. Xem các tụ là

bypass ở tần số làm việc, và mạch đã

được phân cực DC trong vùng bão hòa.

Tính Av, trở kháng vào và ra của mạch

khuếch đại.

Hình 3. 21. Mạch khuếch đại JFET cấu hình CS

Biên soạn: TS. Bùi Thư Cao 10

Chương 3. Phân tích mạch khuếch đại tín hiệu nhỏ tần số thấp dùng FET

Biên soạn: TS. Bùi Thư Cao 11

You might also like

- Câu hỏi điện tửDocument16 pagesCâu hỏi điện tửLinh SuNo ratings yet

- Báo-cáo-TT-DTTT-tuần 2Document13 pagesBáo-cáo-TT-DTTT-tuần 2Hoang Anh VuNo ratings yet

- DCMH Mach Dien Tu Chi Tiet - ABET.201708Document11 pagesDCMH Mach Dien Tu Chi Tiet - ABET.201708laiduong200239No ratings yet

- Bài Phúc Trình 1Document12 pagesBài Phúc Trình 1tran anh tuanNo ratings yet

- Chuong 3 - FET-MDT-HK1 (22-23)Document101 pagesChuong 3 - FET-MDT-HK1 (22-23)TháiNo ratings yet

- Bai Giang MDT - Chuong 4 - 2019Document8 pagesBai Giang MDT - Chuong 4 - 2019Phú Trần ThiênNo ratings yet

- Ngan Hang Cau Hoi TDT Va Anten de OnlyDocument8 pagesNgan Hang Cau Hoi TDT Va Anten de OnlyNgô NamNo ratings yet

- DCBD-Ch05-BJT-P1 - 51 SlidesDocument51 pagesDCBD-Ch05-BJT-P1 - 51 SlidesBlck TùngNo ratings yet

- BJT FetDocument4 pagesBJT Fetnguyendangtri2003No ratings yet

- 6. Chương 2 Mạch điện tử 2Document39 pages6. Chương 2 Mạch điện tử 2lehy16022002No ratings yet

- Bai Giang Ky Thuat Dien Tu Tuong TuDocument258 pagesBai Giang Ky Thuat Dien Tu Tuong TuTình ĐỗNo ratings yet

- Bai 6Document11 pagesBai 6Du NguyenNo ratings yet

- Chuong 1 Tong Quan Ve ĐTCSDocument43 pagesChuong 1 Tong Quan Ve ĐTCSnemmuiyeuNo ratings yet

- CHUONG 10 - MACH KDCSAT (Repaired)Document38 pagesCHUONG 10 - MACH KDCSAT (Repaired)kidgod2111No ratings yet

- Báo cáo đttt tuần 7Document10 pagesBáo cáo đttt tuần 7Nguyễn Văn ThaoNo ratings yet

- Bài giảng Kỹ thuật điện tử C3 - Gửi sinh viênDocument101 pagesBài giảng Kỹ thuật điện tử C3 - Gửi sinh viênLục LinhNo ratings yet

- Mạch Transistor Hiệu Ứng Trường (Fet)Document20 pagesMạch Transistor Hiệu Ứng Trường (Fet)QUYNH TU DOAN TRUCNo ratings yet

- LKDTDocument11 pagesLKDTluuphuctan1310No ratings yet

- Đề 1Document3 pagesĐề 1Tiên NguyễnNo ratings yet

- Bai 4 - FET Va Chuyen Mach - 2020 DoneDocument13 pagesBai 4 - FET Va Chuyen Mach - 2020 DoneKiên PhanNo ratings yet

- TH VĐKDocument25 pagesTH VĐKtrường phạm vănNo ratings yet

- Chapter 5Document22 pagesChapter 5TiếnNo ratings yet

- DCBD-CH05-BJT-P4 - 62 SlidesDocument63 pagesDCBD-CH05-BJT-P4 - 62 SlidesBlck TùngNo ratings yet

- Chuong 1 Tong Quan Ve ĐTCSDocument43 pagesChuong 1 Tong Quan Ve ĐTCSThái PhiênNo ratings yet

- Transistor BJTDocument6 pagesTransistor BJTnguyendangtri2003No ratings yet

- AEDocument4 pagesAEpemot2604No ratings yet

- Đề thi Điện tử thông tinDocument2 pagesĐề thi Điện tử thông tinZuky Trương CôngNo ratings yet

- 10-Đ Án S Tay Tra C U Transistor Dòng 2SBxxxxDocument207 pages10-Đ Án S Tay Tra C U Transistor Dòng 2SBxxxxBùi Lê Tấn PhátNo ratings yet

- Trần Tiến Đạt Nhóm 7 DTCSDocument19 pagesTrần Tiến Đạt Nhóm 7 DTCSTiến Đạt TrầnNo ratings yet

- Câu hỏi và thảo luận (6-4-20)Document2 pagesCâu hỏi và thảo luận (6-4-20)Bin BinNo ratings yet

- Chuong 06 Transistor FETDocument56 pagesChuong 06 Transistor FETNguyễn Đức NamNo ratings yet

- Bài Giảng Kỹ Thuật Điện Tử ET2010- C3- Version 2 - Gửi Sinh ViênDocument106 pagesBài Giảng Kỹ Thuật Điện Tử ET2010- C3- Version 2 - Gửi Sinh ViênQuyền Nguyễn KhắcNo ratings yet

- TRANSISTORDocument12 pagesTRANSISTORbuiduythongqtqlnaNo ratings yet

- Thiết kế mạch khuếch đại tạp âm thấp băng hẹp 2.4GHz công nghệ CMOS 0.35 µm sử dụng cấu trúc suy giảm cảm kháng để phối hợp trở kháng (download tai tailieutuoi.com)Document9 pagesThiết kế mạch khuếch đại tạp âm thấp băng hẹp 2.4GHz công nghệ CMOS 0.35 µm sử dụng cấu trúc suy giảm cảm kháng để phối hợp trở kháng (download tai tailieutuoi.com)dtvt2006No ratings yet

- Chương 5 Đáp ứng tần số của BJT và FETDocument18 pagesChương 5 Đáp ứng tần số của BJT và FETapi-3714448100% (1)

- QDT KTGHK AY1617-S2 Dap-An PDFDocument18 pagesQDT KTGHK AY1617-S2 Dap-An PDFhdainghiaNo ratings yet

- Chapter3 BJTDocument27 pagesChapter3 BJTQuan NguyenNo ratings yet

- A Practical Guide To EMC Engineering PDFDrive Pages 2.en - VIDocument82 pagesA Practical Guide To EMC Engineering PDFDrive Pages 2.en - VItranvietdung1998qnNo ratings yet

- JFETDocument28 pagesJFETDat Nguyen ThanhNo ratings yet

- trắc nghiệm ktdtDocument40 pagestrắc nghiệm ktdtnamnguyen.2808199No ratings yet

- Chuong 1Document62 pagesChuong 1Hoàng QuangNo ratings yet

- JFETDocument26 pagesJFETDat Nguyen ThanhNo ratings yet

- Chapter 3. Single-Stage Transistor Amplifiers Phu-2022Document64 pagesChapter 3. Single-Stage Transistor Amplifiers Phu-2022Công Tâm LêNo ratings yet

- Mach-Dien-Tu-Thong-Tin - Trinh-Xuan-Dung - De-Thi-Cuoi-Ky-Mdttt-21212018 - (Cuuduongthancong - Com)Document2 pagesMach-Dien-Tu-Thong-Tin - Trinh-Xuan-Dung - De-Thi-Cuoi-Ky-Mdttt-21212018 - (Cuuduongthancong - Com)Cảnh Hưng TrầnNo ratings yet

- Tra Cuu BJTDocument170 pagesTra Cuu BJTVũ Thanh TùngNo ratings yet

- Chapter2 Cacphantumachdien1Document139 pagesChapter2 Cacphantumachdien1Bui NamNo ratings yet

- MDTTT KTGK DV19CLC OnlineDocument2 pagesMDTTT KTGK DV19CLC OnlineTrần Hai LyNo ratings yet

- Bài giảng chi tiết Linh kiện điện tử DC2CN18 - Chương 1Document17 pagesBài giảng chi tiết Linh kiện điện tử DC2CN18 - Chương 1Tùng LâmNo ratings yet

- Lab 03 Hand-OutDocument3 pagesLab 03 Hand-OutCt PhươngNo ratings yet

- Báo Cáo TN4 - L12 - 08Document24 pagesBáo Cáo TN4 - L12 - 08Thiên Tú Bùi VõNo ratings yet

- Lab 06Document5 pagesLab 06duonganhquanhsgs20No ratings yet

- 20202Document2 pages20202Nguyễn ĐiệpNo ratings yet

- 1 - Bieu Dien Cac Phan Tu Cua Luoi DienDocument43 pages1 - Bieu Dien Cac Phan Tu Cua Luoi Dientran dungNo ratings yet

- Lab 3Document3 pagesLab 3PhongNo ratings yet

- TNM Mạch-DcDocument13 pagesTNM Mạch-Dcdat.ta2k1No ratings yet

- Chương 2Document56 pagesChương 2Phú Trần ThiênNo ratings yet

- CH 1Document61 pagesCH 1Phú Trần ThiênNo ratings yet

- DCMH Mach Dien Tu AUN 2018Document4 pagesDCMH Mach Dien Tu AUN 2018Phú Trần ThiênNo ratings yet

- Dap An - Rubic - de Thi 2 GK - MDT - 2022Document2 pagesDap An - Rubic - de Thi 2 GK - MDT - 2022Phú Trần ThiênNo ratings yet

- Dap An - Rubic - de Thi 1 GK - MDT - 2022Document2 pagesDap An - Rubic - de Thi 1 GK - MDT - 2022Phú Trần ThiênNo ratings yet

- Bai Giang MDT - Chuong 1 - 2022Document9 pagesBai Giang MDT - Chuong 1 - 2022Phú Trần ThiênNo ratings yet

- Mạch Điện TửDocument37 pagesMạch Điện TửPhú Trần ThiênNo ratings yet

- Bai Giang MDT - Chuong 2 - 2019Document14 pagesBai Giang MDT - Chuong 2 - 2019Phú Trần ThiênNo ratings yet