Professional Documents

Culture Documents

CMOS VLSI Design 70

Uploaded by

Carlos Saavedra0 ratings0% found this document useful (0 votes)

8 views1 pageOriginal Title

CMOS-VLSI-design-70

Copyright

© © All Rights Reserved

Available Formats

PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

© All Rights Reserved

Available Formats

Download as PDF, TXT or read online from Scribd

0 ratings0% found this document useful (0 votes)

8 views1 pageCMOS VLSI Design 70

Uploaded by

Carlos SaavedraCopyright:

© All Rights Reserved

Available Formats

Download as PDF, TXT or read online from Scribd

You are on page 1of 1

1.

9 Circuit Design 43

Energy is required to charge and discharge the load capacitance. This is called

dynamic power because it is consumed when the circuit is actively switching. The dynamic

power consumed when a capacitor is charged and discharged at a frequency f is

2

Pdynamic = CV DD f

Even when the gate is not switching, it draws some static power. Because an OFF transis-

tor is leaky, a small amount of current Istatic flows between power and ground, resulting in

a static power dissipation of

Pstatic = I staticV DD

Chapter 5 examines power in more detail.

A particular logic function can be implemented in many ways.

Should the function be built with ANDs, ORs, NANDs, or NORs?

What should be the fan-in and fan-out of each gate? How wide should

the transistors be on each gate? Each of these choices influences the

capacitance and current and hence the speed and power of the circuit, as g1

well as the area and cost. a x

As mentioned earlier, in many design methodologies, logic synthe- b

g2 g4

sis tools automatically make these choices, searching through the stan- y

a

dard cells for the best implementation. For many applications, synthesis cout

c

is good enough. When a system has critical requirements of high speed g3

or low power or will be manufactured in large enough volume to justify b z

c

the extra engineering, custom circuit design becomes important for criti-

cal portions of the chip. (a)

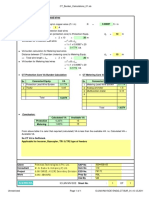

Circuit designers often draw schematics at the transistor and/or gate

level. For example, Figure 1.61 shows two alternative circuit designs for

the carry circuit in a full adder. The gate-level design in Figure 1.61(a) a p1 b p2 b p4

i4

requires 26 transistors and four stages of gate delays (recall that ANDs c p3 i3 a p5 p6

cn

cout

and ORs are built from NANDs and NORs followed by inverters). The c n3 i1 a n5 n6

transistor-level design in Figure 1.61(b) requires only 12 transistors and i2

a n1 b n2 b n4

two stages of gate delays, illustrating the benefits of optimizing circuit

designs to take advantage of CMOS technology.

These schematics are then netlisted for simulation and verification. (b)

One common netlist format is structural Verilog HDL. The gate-level

FIGURE 1.61 Carry subcircuit

design can be netlisted as follows:

module carry(input logic a, b, c,

output logic cout);

logic x, y, z;

and g1(x, a, b);

and g2(y, a, c);

and g3(z, b, c);

or g4(cout, x, y, z);

endmodule

You might also like

- An Optimum Vlsi Design of A 16 6-Bit Alu: Ii. Binary Adder R CircuitsDocument4 pagesAn Optimum Vlsi Design of A 16 6-Bit Alu: Ii. Binary Adder R CircuitsBüşra HasılcıNo ratings yet

- Cmos Design Objective QuestionsDocument18 pagesCmos Design Objective QuestionsdycsteiznNo ratings yet

- Quiz QuestionsDocument40 pagesQuiz QuestionsHarold Wilson0% (1)

- Reservoir GridsDocument6 pagesReservoir GridsappudeselvanNo ratings yet

- 4 Bit Johnson CounterDocument6 pages4 Bit Johnson CountermahimaNo ratings yet

- Reservoir Simulation GridsDocument6 pagesReservoir Simulation GridsŚhâhbäž ÇhNo ratings yet

- Efficient Design of 1Document7 pagesEfficient Design of 1sumathiNo ratings yet

- Vlsi Lab Manual (18ecl77) - 2022-23Document226 pagesVlsi Lab Manual (18ecl77) - 2022-23Prajwal KoppaNo ratings yet

- Capacitance and Power Modeling at Logic-Level: C V F PowerDocument7 pagesCapacitance and Power Modeling at Logic-Level: C V F PowerAnala MNo ratings yet

- Swarm Intelligence Based Sizing Methodology For CMOS Operational AmplifierDocument4 pagesSwarm Intelligence Based Sizing Methodology For CMOS Operational AmplifiermohsenparsauniNo ratings yet

- A High Throughput Implementation of QC-LDPC CodesDocument12 pagesA High Throughput Implementation of QC-LDPC CodesrichnameNo ratings yet

- Shanthi Pavan - CT DSM, Design Considerations - 2016Document6 pagesShanthi Pavan - CT DSM, Design Considerations - 2016Saleh Heidary ShalmanyNo ratings yet

- 2.704Gsps: A 6-Bit DAC For Ds-Cdma UwbDocument4 pages2.704Gsps: A 6-Bit DAC For Ds-Cdma Uwbissam_techNo ratings yet

- Scalable and Low Power LDPC Decoder Design Using High Level Algorithmic SynthesisDocument4 pagesScalable and Low Power LDPC Decoder Design Using High Level Algorithmic Synthesisig77No ratings yet

- VLSI Design SoC CH 6Document125 pagesVLSI Design SoC CH 6Arqam Ali KhanNo ratings yet

- Scaling Trends For The On Chip Power Dissipation: CISX 326, Stanford University, Stanford, CA 94305, USADocument3 pagesScaling Trends For The On Chip Power Dissipation: CISX 326, Stanford University, Stanford, CA 94305, USApvegaNo ratings yet

- Design and Analysis of A Cascode Distributed LNA With Gain and Noise Improvement in 0.15-m GaAs pHEMT TechnologyDocument5 pagesDesign and Analysis of A Cascode Distributed LNA With Gain and Noise Improvement in 0.15-m GaAs pHEMT Technologyسري صالحNo ratings yet

- 8 X 8 Bit Pipelined Dadda Multiplier in CMOSDocument10 pages8 X 8 Bit Pipelined Dadda Multiplier in CMOSHemanthkumarKatreddyNo ratings yet

- Project 5Document4 pagesProject 5krishna mohan pandeyNo ratings yet

- A 4th-Order Analog Continuous-Time Filter Designed Using Standard Cells and Automatic Digital Logic Design ToolsDocument4 pagesA 4th-Order Analog Continuous-Time Filter Designed Using Standard Cells and Automatic Digital Logic Design ToolsByron TarabataNo ratings yet

- Implementation of Pafl Circuit Model Using Sequencial LogicsDocument17 pagesImplementation of Pafl Circuit Model Using Sequencial Logicskalyan settaluriNo ratings yet

- Sub-System Design: Designing of Various Arithmetic Building BlocksDocument84 pagesSub-System Design: Designing of Various Arithmetic Building BlocksAdi SaggarNo ratings yet

- PNR FlowDocument23 pagesPNR Flowsanthosh216eeeNo ratings yet

- Technical Note: Bypass Capacitor Selection For High-Speed DesignsDocument8 pagesTechnical Note: Bypass Capacitor Selection For High-Speed DesignsGHz VcoasmNo ratings yet

- Vlsi - Objective-Questions PDFDocument9 pagesVlsi - Objective-Questions PDFvmspraneethNo ratings yet

- Zipper Cmos Logic CircuitDocument15 pagesZipper Cmos Logic CircuitShreerama Samartha G BhattaNo ratings yet

- Screenshot 2021-04-07 at 2.10.43 PMDocument95 pagesScreenshot 2021-04-07 at 2.10.43 PMtecheatNo ratings yet

- DDR Design Part 1 PCB-May2011Document4 pagesDDR Design Part 1 PCB-May2011Mudassar SaeedNo ratings yet

- CH 04Document44 pagesCH 04Senthil KumarNo ratings yet

- A Low-Power Reconfigurable - Analog-to-Digital ConverterDocument12 pagesA Low-Power Reconfigurable - Analog-to-Digital ConvertergetitabidNo ratings yet

- Cairo University SPARC V2 CUSPARC V2 ProcessorDocument4 pagesCairo University SPARC V2 CUSPARC V2 ProcessorcvsetfNo ratings yet

- Reliability-Oriented Networking Planning VSC - JOURNALDocument10 pagesReliability-Oriented Networking Planning VSC - JOURNALDaniel Adolfo Medina CarvajalNo ratings yet

- Hindawi PDFDocument8 pagesHindawi PDFSupriya AggarwalNo ratings yet

- A Comparative Study Between Different Types of Adders and MultipliersDocument5 pagesA Comparative Study Between Different Types of Adders and MultipliersVivek SinghNo ratings yet

- ABC: An Industrial-Strength Logic Synthesis and Verification ToolDocument29 pagesABC: An Industrial-Strength Logic Synthesis and Verification ToolM Chandan ShankarNo ratings yet

- Efficiency Based Design Flow For Fully-Integrated Class C RF Power Amplifiers in Nanometric CMOSDocument4 pagesEfficiency Based Design Flow For Fully-Integrated Class C RF Power Amplifiers in Nanometric CMOSHimanshu SardanaNo ratings yet

- VHDL MCQDocument18 pagesVHDL MCQtoshit jain100% (1)

- LE PaperDocument16 pagesLE PaperYagami LightNo ratings yet

- Optimal Processor Interface For Cgra-Based Accelerators Implemented On FpgasDocument7 pagesOptimal Processor Interface For Cgra-Based Accelerators Implemented On FpgasBanusha chandranNo ratings yet

- Waleed K. Al-Assadi Anura P. Jayasumana Yashwant K. Malaiya Technical Report CS-96-102Document10 pagesWaleed K. Al-Assadi Anura P. Jayasumana Yashwant K. Malaiya Technical Report CS-96-102RajasekharVenkataNo ratings yet

- Application of Improved PSO For Optimal Design of CMOS Two-Stage Op-Amp Using Nulling Resistor Compensation CircuitDocument6 pagesApplication of Improved PSO For Optimal Design of CMOS Two-Stage Op-Amp Using Nulling Resistor Compensation CircuitmohsenparsauniNo ratings yet

- CTSDocument6 pagesCTSNishanth GowdaNo ratings yet

- FPGA Interview QuestionsDocument11 pagesFPGA Interview Questionssneha587No ratings yet

- Moin-10 1109@EIConRus 2019 8657039Document3 pagesMoin-10 1109@EIConRus 2019 8657039Moin SadiNo ratings yet

- A 112-Gb S PAM-4 Long-Reach Wireline Transceiver Using A 36-Way Time-Interleaved SAR ADC and Inverter-Based RX Analog Front-End in 7-nm FinFETDocument12 pagesA 112-Gb S PAM-4 Long-Reach Wireline Transceiver Using A 36-Way Time-Interleaved SAR ADC and Inverter-Based RX Analog Front-End in 7-nm FinFET王国庆No ratings yet

- Rajagopal 2021Document4 pagesRajagopal 2021Vani YamaniNo ratings yet

- Realizable Reduction For RC Interconnect Circuits: Corporation, 11400 Burnet TXDocument4 pagesRealizable Reduction For RC Interconnect Circuits: Corporation, 11400 Burnet TXJackyNo ratings yet

- At Speed TestDocument20 pagesAt Speed TestJa JaNo ratings yet

- RFA - FinalDocument4 pagesRFA - Finalkanakaraghu sreeramaNo ratings yet

- 1992.10.GaAs20RISC20Processors GaAsICSympDocument5 pages1992.10.GaAs20RISC20Processors GaAsICSympTibor PappNo ratings yet

- CT Sigma Delta WhitePaperDocument8 pagesCT Sigma Delta WhitePaperSomnath KunduNo ratings yet

- Low Power and High Speed 8x8 Bit Multiplier Using Non-Clocked Pass Transistor LogicDocument5 pagesLow Power and High Speed 8x8 Bit Multiplier Using Non-Clocked Pass Transistor LogicDai LewisNo ratings yet

- Minimizing The Delay of C2mos D Flip Flop Using Logical Effort TheoryDocument3 pagesMinimizing The Delay of C2mos D Flip Flop Using Logical Effort TheorySavio SNo ratings yet

- Pipelined AddersDocument9 pagesPipelined AddersAtul SinghNo ratings yet

- Energy Efficient CMOS Microprocessor DesignDocument10 pagesEnergy Efficient CMOS Microprocessor Designnew accNo ratings yet

- A CMOS Based Low Power Digitally Controlled OscillDocument12 pagesA CMOS Based Low Power Digitally Controlled OscillDEEPAK PRAJAPATINo ratings yet

- MCQsDocument19 pagesMCQsansalvNo ratings yet

- Expanding The Synopsys Primetime Solution With Power AnalysisDocument7 pagesExpanding The Synopsys Primetime Solution With Power AnalysisRamakrishnaRao SoogooriNo ratings yet

- Cmos Vlsi Design 208Document1 pageCmos Vlsi Design 208Carlos SaavedraNo ratings yet

- Cmos Vlsi Design 184Document1 pageCmos Vlsi Design 184Carlos SaavedraNo ratings yet

- 4.4.6.4 Voltage Dependence: Chapter 4 DelayDocument1 page4.4.6.4 Voltage Dependence: Chapter 4 DelayCarlos SaavedraNo ratings yet

- CMOS VLSI Design 192Document1 pageCMOS VLSI Design 192Carlos SaavedraNo ratings yet

- Cmos Vlsi Design 186Document1 pageCmos Vlsi Design 186Carlos SaavedraNo ratings yet

- Cmos Vlsi Design 207Document1 pageCmos Vlsi Design 207Carlos SaavedraNo ratings yet

- Cmos Vlsi Design 198Document1 pageCmos Vlsi Design 198Carlos SaavedraNo ratings yet

- Cmos Vlsi Design 203Document1 pageCmos Vlsi Design 203Carlos SaavedraNo ratings yet

- CMOS VLSI Design 191Document1 pageCMOS VLSI Design 191Carlos SaavedraNo ratings yet

- Layer Density Rules: Chapter 3 CMOS Processing TechnologyDocument1 pageLayer Density Rules: Chapter 3 CMOS Processing TechnologyCarlos SaavedraNo ratings yet

- Pitfalls and Fallacies: Targeting A Bleeding-Edge ProcessDocument1 pagePitfalls and Fallacies: Targeting A Bleeding-Edge ProcessCarlos SaavedraNo ratings yet

- Cmos Vlsi Design 149Document1 pageCmos Vlsi Design 149Carlos SaavedraNo ratings yet

- Logical Effort of Paths: A and C Begin To Rise (Figure 4.28 (C) ) - at First, Both Nodes See ApproximatelyDocument1 pageLogical Effort of Paths: A and C Begin To Rise (Figure 4.28 (C) ) - at First, Both Nodes See ApproximatelyCarlos SaavedraNo ratings yet

- Manufacturing Issues: Antenna RulesDocument1 pageManufacturing Issues: Antenna RulesCarlos SaavedraNo ratings yet

- Circuit Extraction: CONNECT Layer1 Layer2Document1 pageCircuit Extraction: CONNECT Layer1 Layer2Carlos SaavedraNo ratings yet

- Cmos Vlsi Design 162Document1 pageCmos Vlsi Design 162Carlos SaavedraNo ratings yet

- Chapter 3 CMOS Processing Technology: 3.4.3.4 Transmission LinesDocument1 pageChapter 3 CMOS Processing Technology: 3.4.3.4 Transmission LinesCarlos SaavedraNo ratings yet

- (A) Diffusion Barrier Etch Stop (B) Via Dielectric (C) Line Dielectric (D) Anti-Reflective LayerDocument1 page(A) Diffusion Barrier Etch Stop (B) Via Dielectric (C) Line Dielectric (D) Anti-Reflective LayerCarlos SaavedraNo ratings yet

- CMOS Process Enhancements: Layer Rule Description 65 NM Rule (M) TABLE 3.1Document1 pageCMOS Process Enhancements: Layer Rule Description 65 NM Rule (M) TABLE 3.1Carlos SaavedraNo ratings yet

- Circuit Elements: 3.4.3.1 CapacitorsDocument1 pageCircuit Elements: 3.4.3.1 CapacitorsCarlos SaavedraNo ratings yet

- 3.4.3.7 Non-Volatile Memory: P+ Diode N+ Well Contact Collector Base EmitterDocument1 page3.4.3.7 Non-Volatile Memory: P+ Diode N+ Well Contact Collector Base EmitterCarlos SaavedraNo ratings yet

- 3.4.1.5 Plastic Transistors: InterconnectDocument1 page3.4.1.5 Plastic Transistors: InterconnectCarlos SaavedraNo ratings yet

- 3.4 CMOS Process Enhancements: 3.4.3.3 InductorsDocument1 page3.4 CMOS Process Enhancements: 3.4.3.3 InductorsCarlos SaavedraNo ratings yet

- MOSIS Scalable CMOS Design RulesDocument1 pageMOSIS Scalable CMOS Design RulesCarlos SaavedraNo ratings yet

- CMOS VLSI Design 140Document1 pageCMOS VLSI Design 140Carlos SaavedraNo ratings yet

- Micron Design Rules: Chapter 3 CMOS Processing TechnologyDocument1 pageMicron Design Rules: Chapter 3 CMOS Processing TechnologyCarlos SaavedraNo ratings yet

- 3.4.1.2 Silicon On Insulator: Chapter 3 CMOS Processing TechnologyDocument1 page3.4.1.2 Silicon On Insulator: Chapter 3 CMOS Processing TechnologyCarlos SaavedraNo ratings yet

- 3.4.1.4 Higher Mobility: High-K Gate Stack TEM (© IEEE 2007.)Document1 page3.4.1.4 Higher Mobility: High-K Gate Stack TEM (© IEEE 2007.)Carlos SaavedraNo ratings yet

- Mask Summary: The Masks Encountered For Well Specification May Include N-WellDocument1 pageMask Summary: The Masks Encountered For Well Specification May Include N-WellCarlos SaavedraNo ratings yet

- Mask Summary: The Only Mask Involved With Contacts To Active or PolyDocument1 pageMask Summary: The Only Mask Involved With Contacts To Active or PolyCarlos SaavedraNo ratings yet

- Single Phase Semi ConverterDocument18 pagesSingle Phase Semi Convertermohamed enanyNo ratings yet

- National Electrical Code: Understanding TheDocument36 pagesNational Electrical Code: Understanding TheJuan Carlos Cabello Montiel50% (2)

- EMC 22 Electric Motor CheckerDocument1 pageEMC 22 Electric Motor CheckerindustrialindiaNo ratings yet

- MVC 9078Document32 pagesMVC 9078Rey Arthur100% (1)

- Preventa Safety Detection XCSLE2727312Document2 pagesPreventa Safety Detection XCSLE2727312wolfzaumNo ratings yet

- ACP Revit MEP Electrical Exam Objectives PDFDocument1 pageACP Revit MEP Electrical Exam Objectives PDFAdnan GulshanNo ratings yet

- Panel Bapelkes DIY: Gedung 1 No Material Spesifikasi Sub Total Total Lantai 1Document4 pagesPanel Bapelkes DIY: Gedung 1 No Material Spesifikasi Sub Total Total Lantai 1Ahmad Nur ArifinNo ratings yet

- Racks and Cubicles For Capacitor Banks: CompositionDocument5 pagesRacks and Cubicles For Capacitor Banks: CompositionWang MariusNo ratings yet

- Driver SCN SerieDocument47 pagesDriver SCN SerieWalther Ernesto Molina DominguezNo ratings yet

- Act 2 - 1 Gen Síncrono MaqEle - II 2023Document34 pagesAct 2 - 1 Gen Síncrono MaqEle - II 2023Héctor Manuel Bobadilla PimientaNo ratings yet

- SRNE - HF Series - LV - EU - Solar Charge Inverter - Datasheet - 2.1Document1 pageSRNE - HF Series - LV - EU - Solar Charge Inverter - Datasheet - 2.1Lin YutingNo ratings yet

- Snag List For 142041Document4 pagesSnag List For 142041kassa hilemnehNo ratings yet

- Trench Bushings Cot 24kv To 550kvDocument24 pagesTrench Bushings Cot 24kv To 550kvdsanmi0% (1)

- 100+ Electrical & Electronic Circuit SymbolsDocument35 pages100+ Electrical & Electronic Circuit SymbolsServicios y Repuestos Jeremy Azhael 2320 C.ANo ratings yet

- EEE1001 - ELECTRIC-CIRCUITS-AND-SYSTEMS - LTP - 1.1 - 1 - EEE1001 - Electric Circuits and SystemsDocument2 pagesEEE1001 - ELECTRIC-CIRCUITS-AND-SYSTEMS - LTP - 1.1 - 1 - EEE1001 - Electric Circuits and SystemsParinay SethNo ratings yet

- Data Sheet 6ES7323-1BL00-0AA0: Supply VoltageDocument4 pagesData Sheet 6ES7323-1BL00-0AA0: Supply Voltagefrancisco fernandezNo ratings yet

- Preventive Maintenance Manual: ACS 6000 Medium Voltage DrivesDocument33 pagesPreventive Maintenance Manual: ACS 6000 Medium Voltage Drivesbishwas123100% (2)

- Function of U1 CA555Document7 pagesFunction of U1 CA555sjnl100% (1)

- EDEPRO0146 0116 1 en Prospekt Multicond Data SheetDocument10 pagesEDEPRO0146 0116 1 en Prospekt Multicond Data SheetMartín LópezNo ratings yet

- Principles & ApplicationsDocument12 pagesPrinciples & ApplicationsECE COMPNo ratings yet

- PWM Voltage ConverterDocument1 pagePWM Voltage Converterjmbranco76No ratings yet

- ATS48 Repair Trouble Shooting ManualDocument248 pagesATS48 Repair Trouble Shooting ManualRodolfoAntonioLeónCárdenas100% (3)

- GET6600G Section 10 Guide Form Spec Rev 2Document14 pagesGET6600G Section 10 Guide Form Spec Rev 2NestorNateraNo ratings yet

- AuX 101Document3 pagesAuX 101madaba723504100% (1)

- MIZAR ALKOR UPS ManualDocument73 pagesMIZAR ALKOR UPS ManualAbdelwhab ElsaftyNo ratings yet

- Vacuum Circuit Breaker Test ReportDocument13 pagesVacuum Circuit Breaker Test ReportRajeev babbar100% (1)

- 3AP-3FI - Mach Noi BoDocument168 pages3AP-3FI - Mach Noi BoBảo NguyễnNo ratings yet

- CT Burden Calculations 01 PDFDocument1 pageCT Burden Calculations 01 PDFArunava Basak100% (1)

- Notes: Multi-Function Relay Wiring GuideDocument2 pagesNotes: Multi-Function Relay Wiring GuideKyle Sean YoungNo ratings yet

- SMD DesolderingDocument1 pageSMD Desolderingdavid reyesNo ratings yet